線上影音

Home > ANSYS HFSS 教學 > IC EMC

本文始於2018.10,以2018.2 SIwave、HFSS示範操作,介紹IEC-61967/62132所定義的IC EMC量測/測試方式、如何做IC EMC模擬(CPM+IBIS),以及當你無法從IC供應商取得CPM(Chip Power Model)模型時,如何處理。

-- 更新 10.3 , 2022.07.01

-

IC-EMI量測 (IEC 61967)

-

IC-EMS量測 (IEC 62132)

-

IC Impulse抗擾 (IEC 62215)

-

IC-EMI行為模型 (IEC 62433-2,3)

-

IC-EMI行為模型, I/O模型 (IEC 62014)

-

IC-EMS行為模型 (IEC 62433-4,5)

-

IC Impulse抗擾行為模型 (IEC 62433-6)

-

IC-EMI模擬,含CPM模型

-

IC-EMI模擬,不含CPM模型

-

IC-EMS模擬,含CPM+CECM模型

-

問題與討論

13.2 影響HFSS與SIwave遠場EMI模擬差異的來源? (重要)

13.3 為何9.4.3沒有I/O toggle的EMI,並沒有比較好? (重要)

13.4 如何在指定距離的平面上,以頻譜方式輸出近場最大值?

13.5 為何少數CPM會看到.inc內所描述的不只有電流源,還有電壓源加一些奇怪的東西? (重要)

13.6 為何9.2單在SIwave做的near/far-field與9.4.3用Designer Circuit+SIwave push excitation做的完全不同? (重要)

13.7 仿10.2手法,我們可以把EMI scanner掃到的IC表面E/H (real, imag)資料,輸入HFSS當IC EMI模型嗎?

13.8 為何IC EMC法規IEC62433-2早就定義,至今業界還是很少看到CPM model? (僅大型IC設計公司有,系統廠都拿不到)

![]()

-

近年來由於5G/AI/虛擬貨幣(挖礦機)...等產業需求的推升,更高速且高耗電的IC/封裝設計需求,正以驚人的速度在增加。打個比方:筆者兩年前看到最複雜的封裝是7000 bumps,而2018年看到最複雜的封裝是110000 bumps(平均電流350A, 瞬間最大電流500A),兩年來增加了15倍的複雜度,真是嚇死人了。這對做SI/PI/EMI的人來說,挑戰真的是越來越大,也不得不在整個設計與模擬流程上,找尋更好、更有效的方法。

本文將從IEC所定義的量測/測試角度出發,搭配ANSYS模擬工具介紹適用的IC EMC模擬手法,並對模擬結果做實務性討論。

-

IC-EMI量測 (IEC 61967)

-

IC-EMS量測 (IEC 62132)

-

IC Impulse抗擾 (IEC 62215)

- IC-EMI行為模型 (IEC

62433-2,3) [6][7]

-

IC-EMI行為模型, I/O model (IEC 62014) [8]

- IC-EMS行為模型 (IEC 62433-4,5) [6][7][9]

-

IC Impulse抗擾行為模型 (IEC 62433-6)

-

IC-EMI模擬,含CPM模型

-

IC-EMI模擬,不含CPM模型

- IC-EMS模擬,含CPM+CECM模型

-

IC EMC模擬,推薦的手法是包含封裝(.mcm/.sip)與IC CPM模型一起模擬。

-

2.5D EM求解器(SIwave)可以快速計算EMI,並與3D EM求解器(HFSS)結果有一致性。(有完整參考平面下)

-

掃頻設定對EMI模擬分析非常重要,掃頻解析度必須確保所關心的EMI頻點有被計算到。

-

問題與討論Q&A

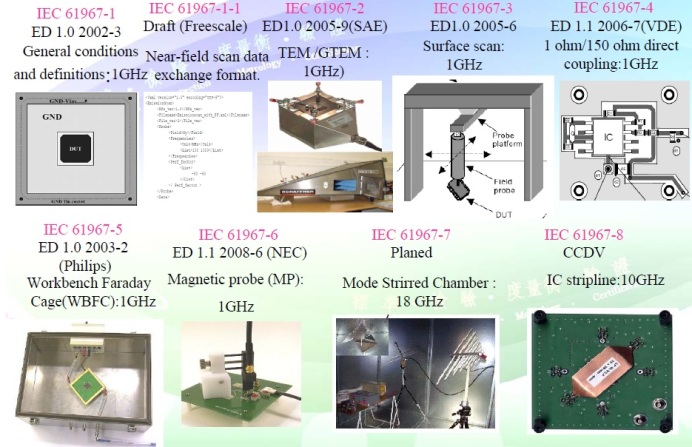

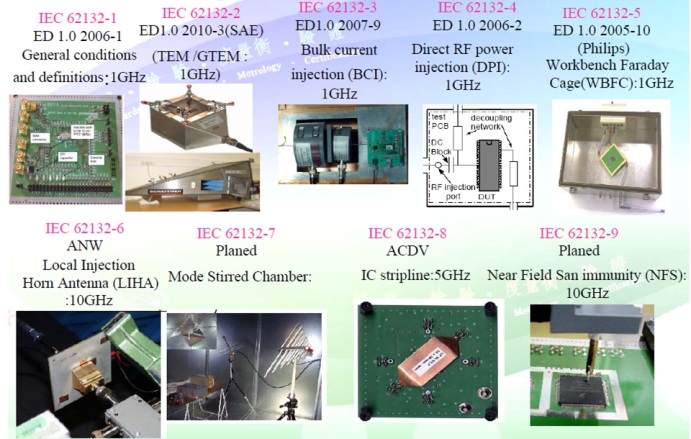

下圖取自逢甲大學林漢年教授整理的資料

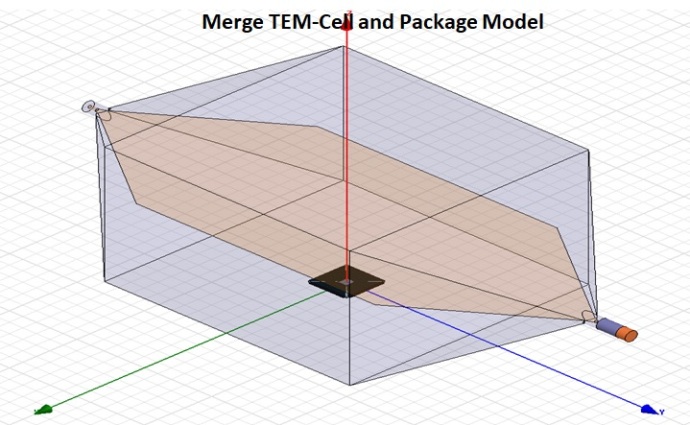

IEC 61967-1定義一個參考平面完整10cmx10cm的四層板PCB,待測IC放一面,走線與被動元件放另一面,搭配IEC 61967-2的TEM Cell測試IC radiative EMI。

IEC 61967-3主要是測IC正上方由IC帶出的EMI。市面上有一些商用的EMI scanner,業界使用蠻多的 (as NEC EMI scanner)

IEC 61967-6主要是測走線帶出的EMI,其感應量較大,但探棒(magnetic probe)的空間解析度較差。

下圖取自逢甲大學林漢年教授整理的資料

IEC 62132-2與ICE 61967-2測試儀器基本相同,只是操作程序反過來。前者以TEM-Cell中間的導體平面打出輻射能量干擾待測物(IC),後者以TEM-Cell中間的導體平面偵測待測物(IC)所散逸的輻射干擾(EMI)

IEC 62132-3直接對IC腳以電流探棒注入電流雜訊

IEC 62132-6/7/8/9目前法規未定案,但2018年IEEE有一篇IEC 62132-8 做的paper [3]

IEC 62215-2 p.6有寫:未來標準將跟IEC 6100-4-2/4/5類似(ESD/EFT/Surge) [4][5]

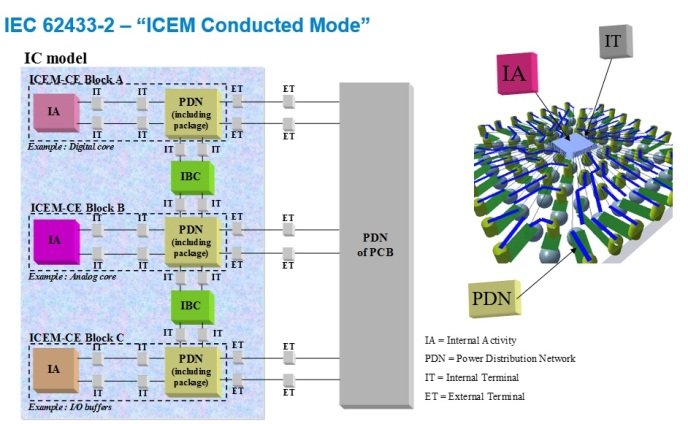

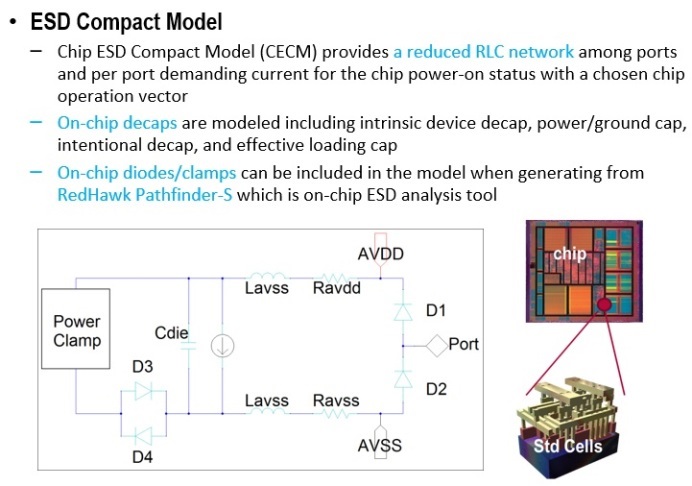

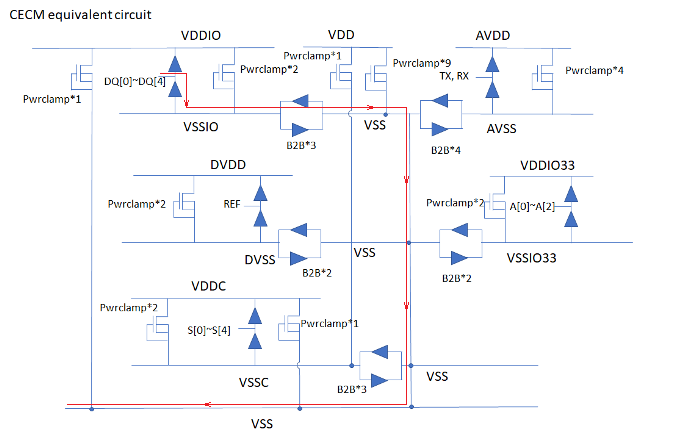

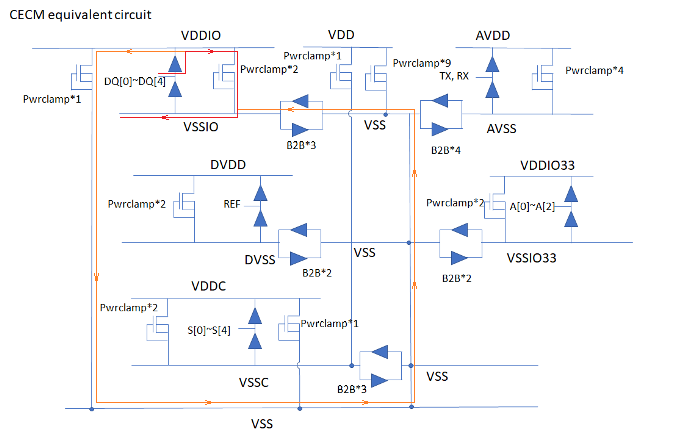

IEC 62433-2定義IC model必須包含內部操作行為(IA),電源寄生網路(PDN),包含封裝/PCB寄生效應

![]() 這其實就是CPM (Chip Power Model, ie. IC電流源 + IC電源分布網路) + 封裝模型,搞半天這不是EDA廠商自己推的,人家IEC法規也是這樣定義的

這其實就是CPM (Chip Power Model, ie. IC電流源 + IC電源分布網路) + 封裝模型,搞半天這不是EDA廠商自己推的,人家IEC法規也是這樣定義的

這項就是定義I/O行為模型,也就是我們做SI/PI的人,幾乎天天會用的IBIS model

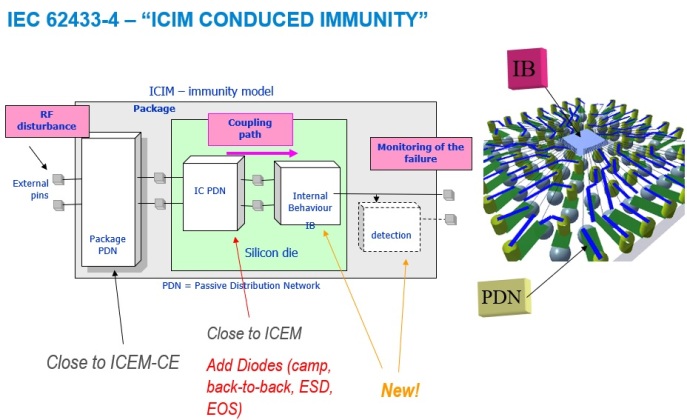

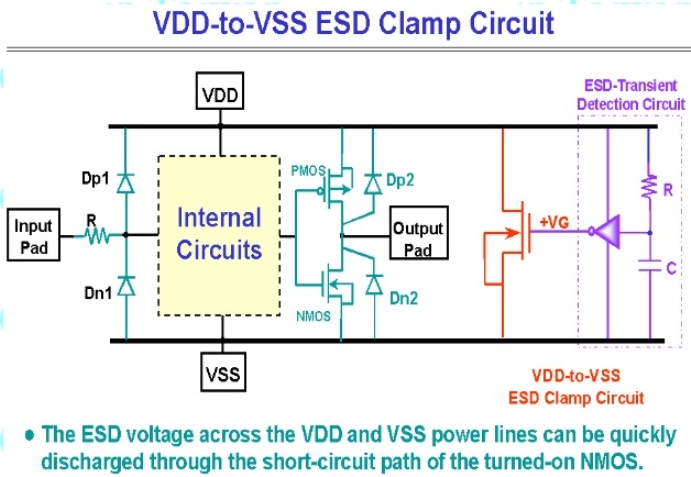

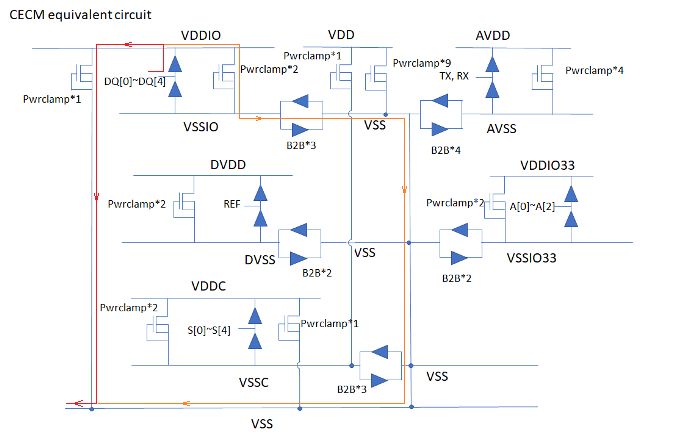

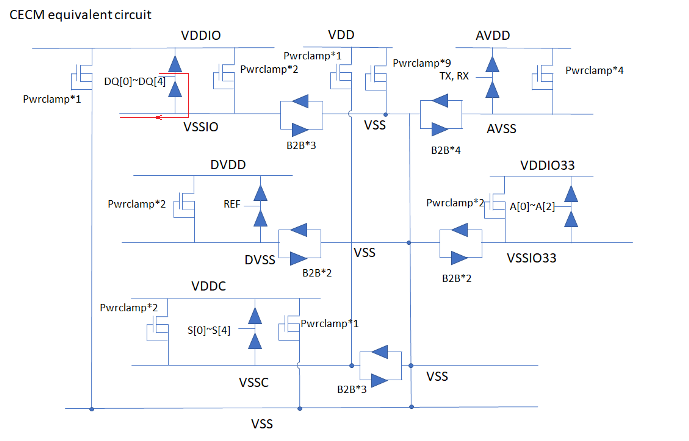

比起IEC 62433-2,IEC 62433-4為了模擬抗擾需多加IC內二極體, 箝位電路, 背對背二極體...。也就是除了考慮IC PDN (passive RLC),還要考慮非線性元件 (diode)。

![]() 這就是Chip ESD Compact Model (CECM)

這就是Chip ESD Compact Model (CECM)

如果不懂IC內for ESD為何要有on-die diode或clamp (RC drive NMOS),請參考交大柯明道教授網頁

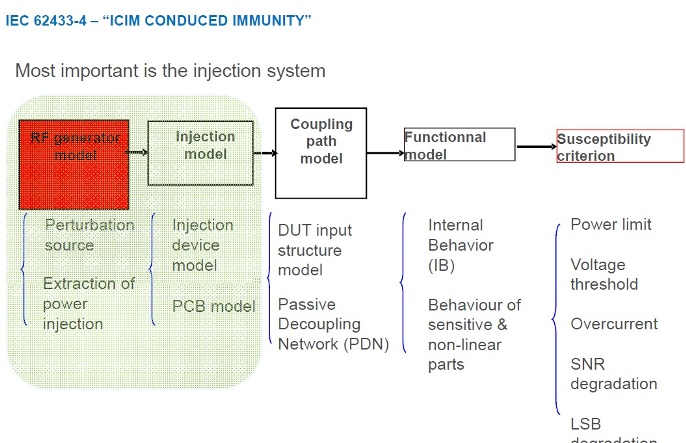

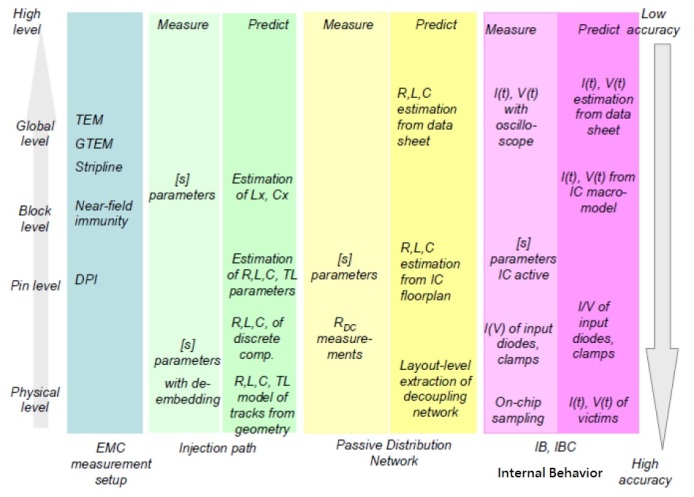

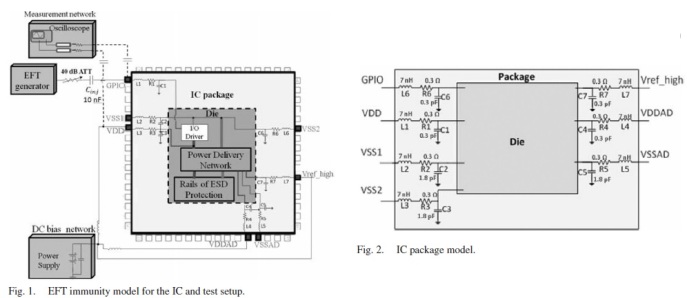

在實踐模擬的手法上,首先最重要的是干擾源的產生與注入,也就是先要有EMS雜訊產生器,如ESD/EFT/Surge generator

接著,由左至右分別考慮Source/Coupling Path/Receiver,EMC三要素的模型。由下至上分別考慮實際物理模型,由IC到系統(透過模擬或量測)

以上,不知各位有沒有看懂,到底IEC建議我們IC EMC模擬要怎麼做??

沒看懂? 不理解? 有看沒有懂??? ![]()

有看出 ... 就是建議IC核心用CPM (Chip Power Model),加上I/O model用IBIS嗎?

如果沒看出來,再多看幾次 ... 就會

... 領悟了 ![]()

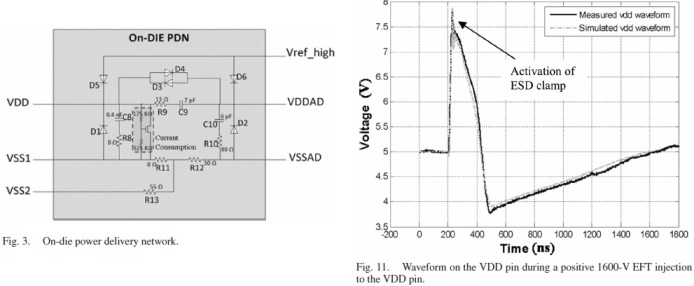

我們來看看一篇2014 IEEE 論文[10]。

站長無意中發現,該篇論文的第一作者Ji Zhang是北京清華大學的高材生,在美國密蘇里大學拿到博士學位後,目前在CISCO工作。本文另外參考的[11][12],他也是第一作者 ,真的是人才,佩服佩服。

9.1 ANSYS

CPM模型 ![]()

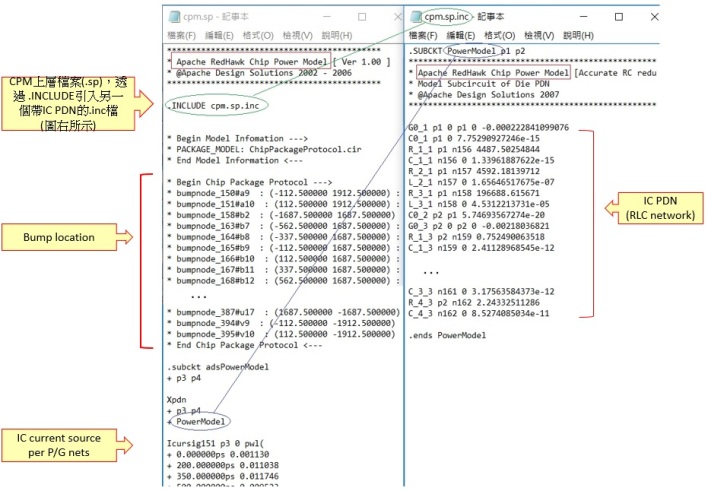

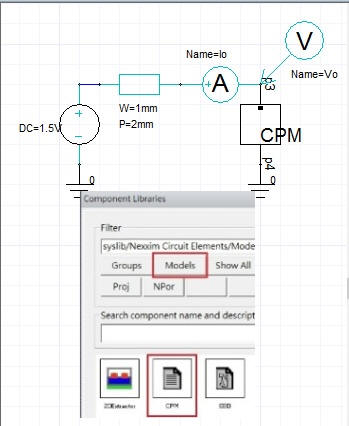

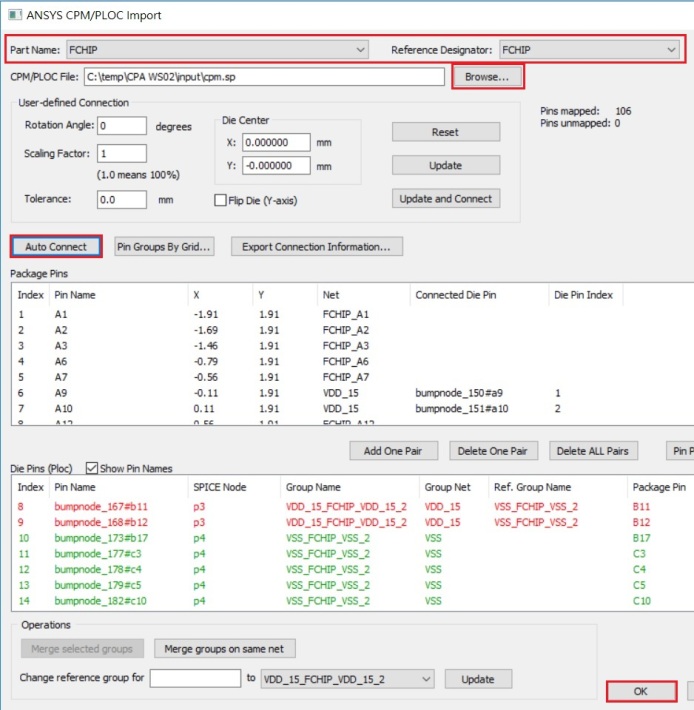

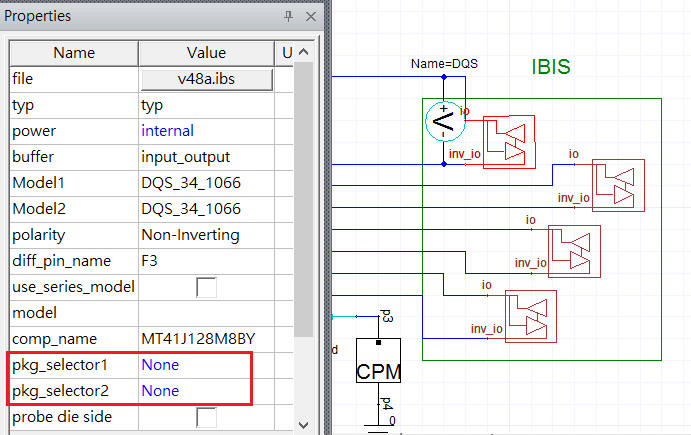

ANSYS CPM model是由.sp與.inc兩個SPICE檔案所組成,前者含Power/Ground埠對net 0的電流源定義(ie. the IA defined in IEC-62433-2),後者含IC Power/Ground RLC network 定義(ie. PDN defined in IEC-62433-2)。每個檔案檔頭都有Apache RedHawk Chip Power Model宣告自字樣。

首先,匯入與測試從IC供應商拿到的CPM模型。注意:並非所有的CPM模型都由ANSYS所產生。 請參閱13.5

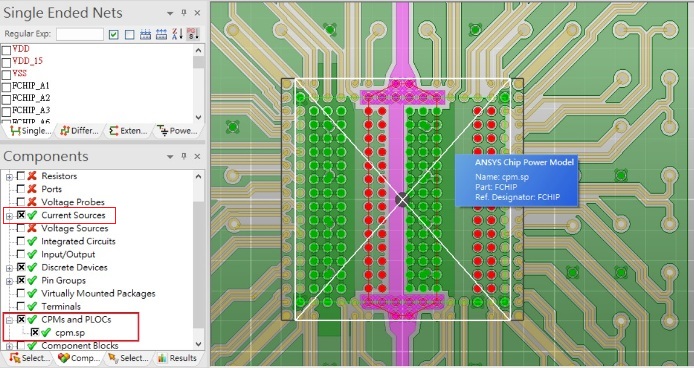

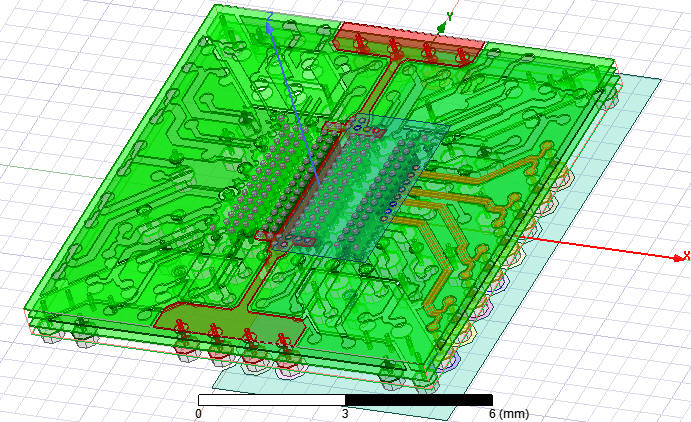

9.2 於SIwave內,封裝帶CPM模型 ![]()

從SIwave步驟 [Import] Tab \ [ANSYS CPM/PLOC file],在DIE端附上CPM模型

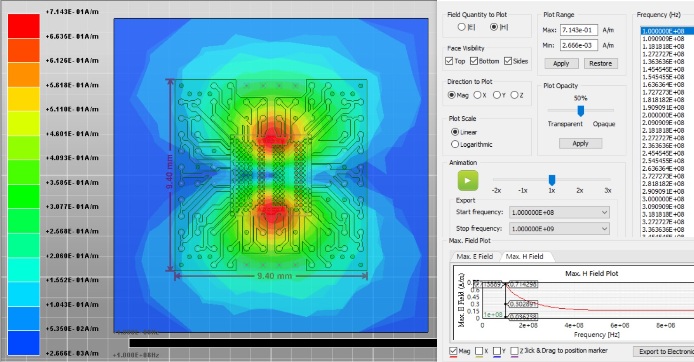

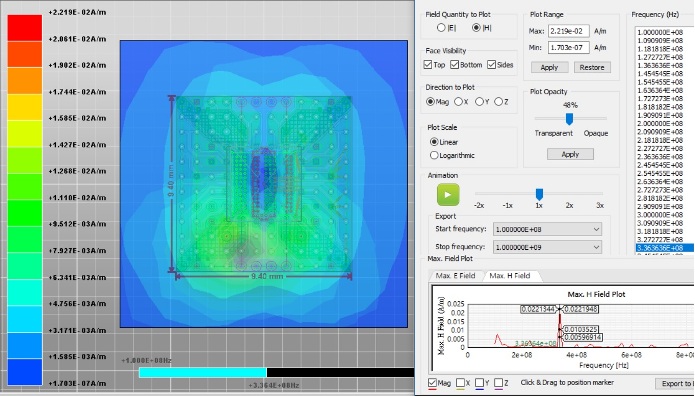

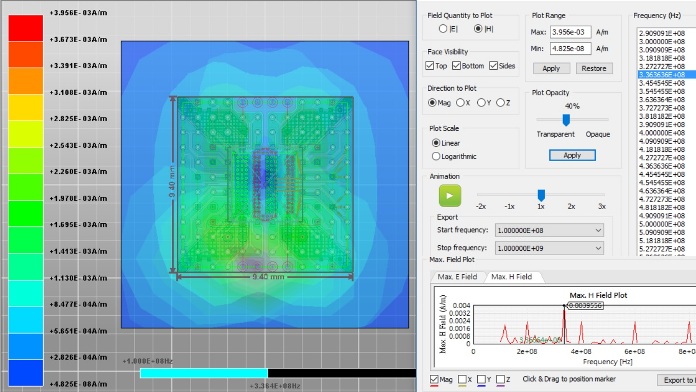

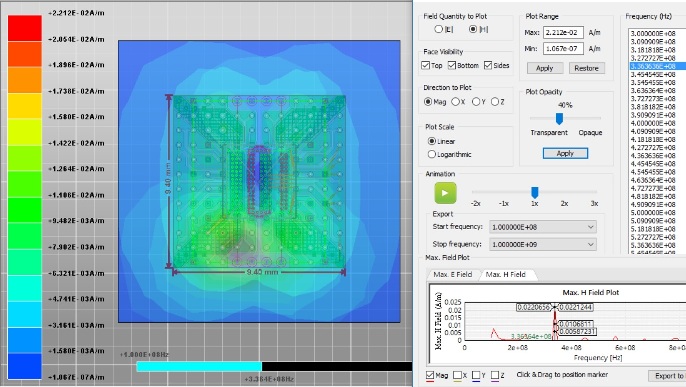

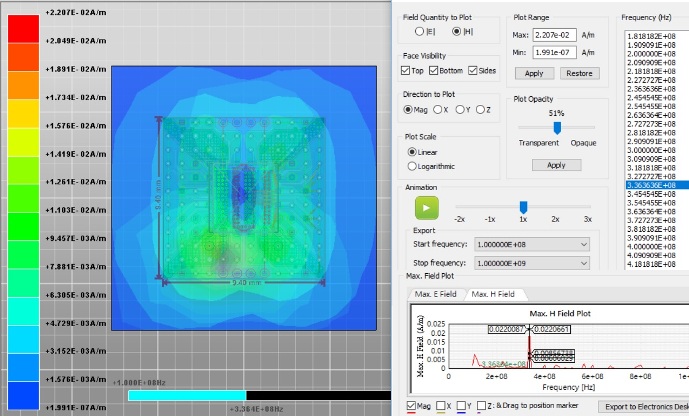

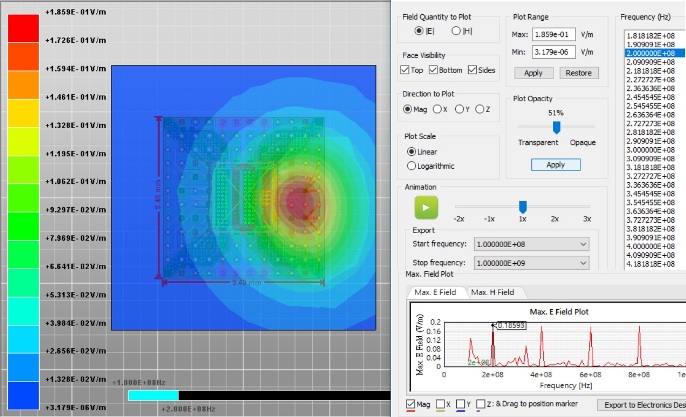

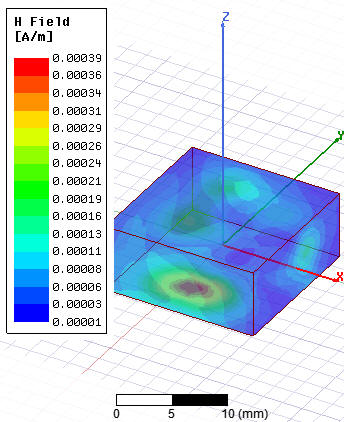

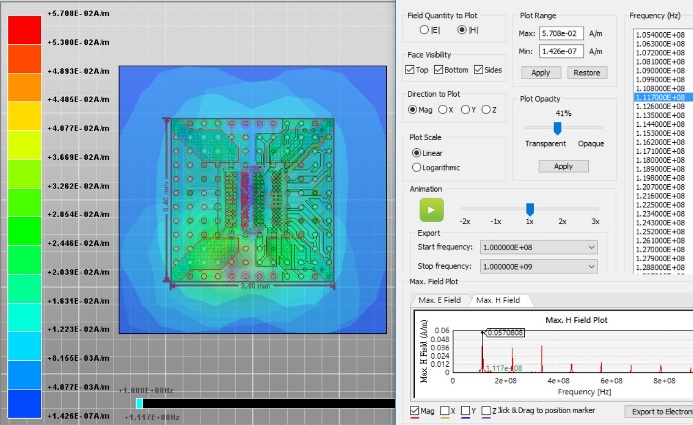

執行SIwave近場分析(這EMI是由CPM內所定義的P/G電流源所激發),在100MHz的磁場

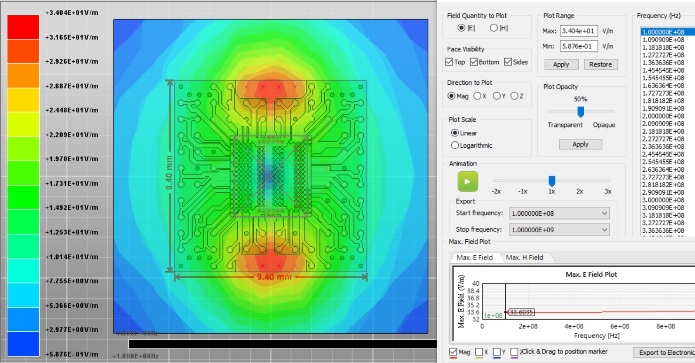

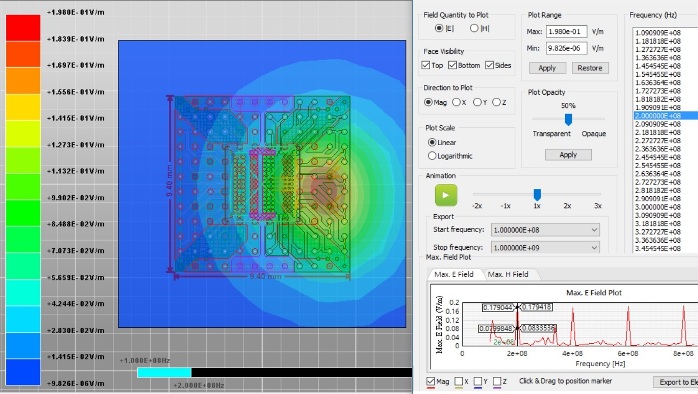

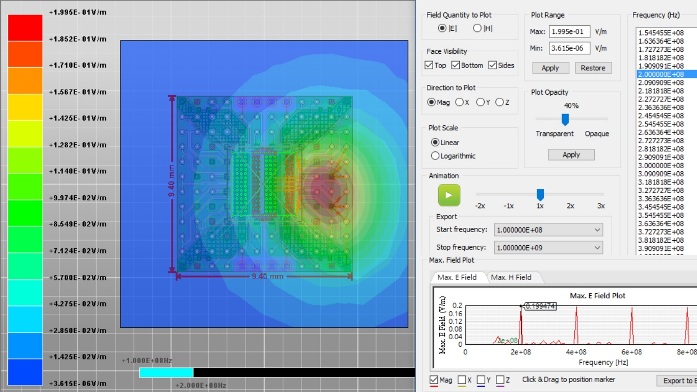

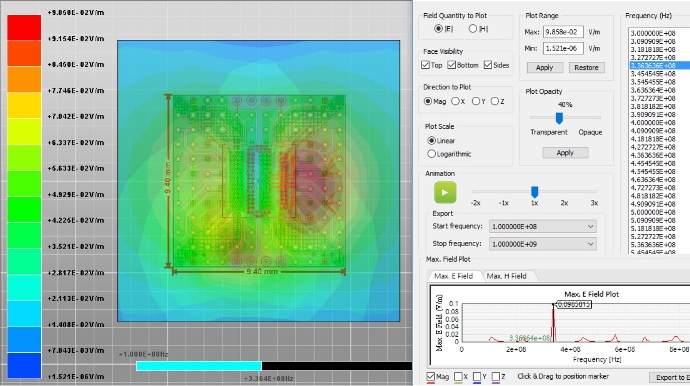

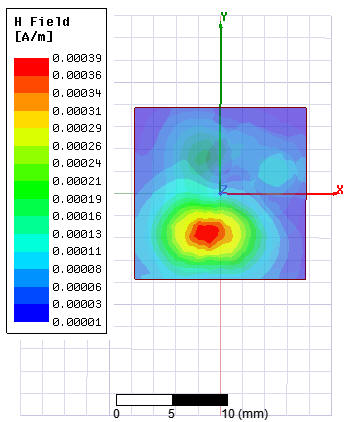

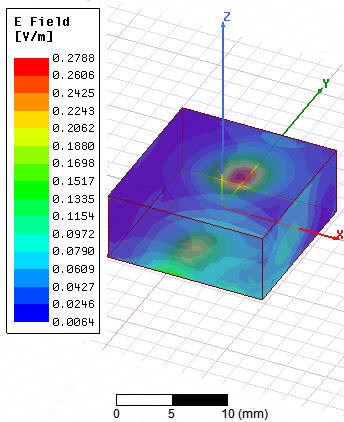

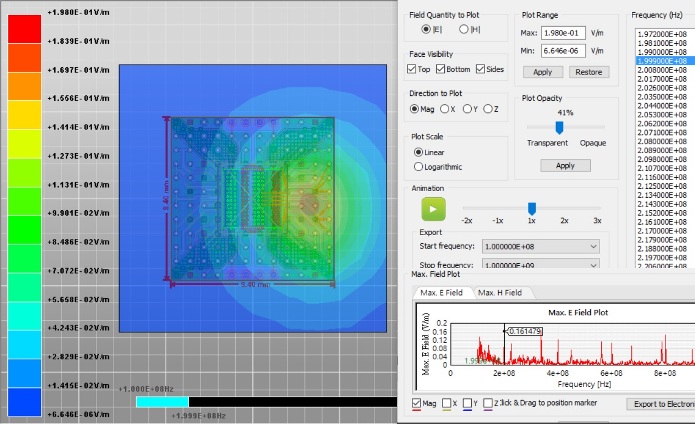

執行SIwave近場分析(這EMI是由CPM內所定義的P/G電流源所激發),在100MHz的電場

執行SIwave遠場分析(這EMI是由CPM內所定義的P/G電流源所激發)

9.3 以CPM與IBIS模型做暫態(時域)分析 ![]()

先關閉SIwave內的CPM與電壓/電流源,然後在Designer環境下連接CPM, IBIS與封裝模型,如下所示。

CPM + Package model + IBIS model with external power (non-ideal power 1.5V)

請移除IBIS內所帶的封裝寄生效應, 因為這部分的影響已經透過SIwave抽出模型,在Designer內連接考慮了。

9.4 於SIwave內,透過激發反饋看遠場EMI ![]()

9.4.1 SIwave跑近/遠場分析 (EMI以P/G電流和5ns bit time的IBIS激發)

EMI triggered by P/G nets (CPM) and I/O nets (IBIS), H-field at 336MHz. (the energy of 336MHz is from CPM current)

EMI以P/G nets (CPM)和I/O nets (IBIS)激發, E-field at 200MHz

E場在200/400/600/800/1000MHz最強的區域正好是四對高速訊號線所在位置(IBIS I/O high-low toggle with 5ns bit time)

為何CPM定義的IC電流主要反映在H-field,而IBIS I/O toggle抽的電流反映在E-field? Refer to here

這是含IC CPM電流(224/336/448/562/674MHz...),IBIS I/O充放電對PI的影響,與IBIS high/low toggle從走線帶出的輻射(200/400/600/800MHz...) 。

9.4.2 CPM + Package model + IBIS model with internal (ideal) power

EMI以 P/G nets (CPM)和I/O nets (IBIS)激發, H-field at 336MHz

EMI以 P/G nets (CPM)和I/O nets (IBIS)激發, E-field at 200MHz

這是含IC CPM電流(224/336/674MHz...),IBIS I/O toggle從走線帶出的輻射(200/400/600/800MHz...),但不含IBIS I/O本身充放電對PI的影響。

與9.4.1相比,近場H在336MHz有下降,但遠場沒有下降。

9.4.3 CPM + Package model + Open IBIS model

這是只有IC CPM電流帶出的輻射。

9.5 以上所有步驟也可以HFSS+Designer實現 ![]()

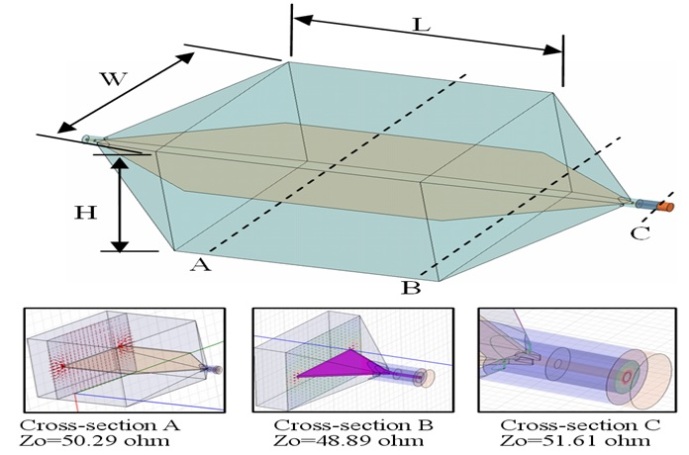

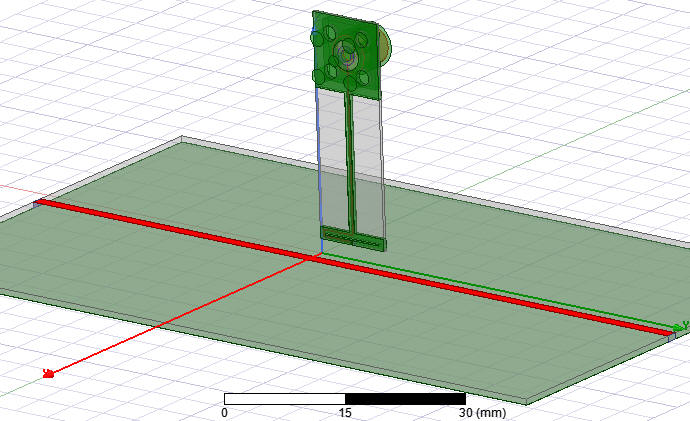

9.6 考慮全系統EMI(IC+封裝/PCB+測試環境, FE-BI) ![]()

如上所示目前的full-wave FEM模擬工具,已經有能力解這種大尺寸比的題目。實際做IC+PCB的EMI模擬分析,不需要搞這麼複雜,直接在HFSS內選Emission Test Report輸出由軟體幫你用後處理估出的|Emax|即可。

如果真的想在HFSS內放一個接收天線,透過模擬得到跟EMI實驗室一樣的結果,那還必須跟實驗室一樣先對天線做全頻帶的增益校正(後處理),想到就頭皮發麻。除非吃飽太閒,或純做研究練功,不然我還真想不到什麼理由非得需要這麼做。

10.1以時域量測資料來模型化電流源 ![]()

對於大部份拿不到IC CPM模型的系統廠,可以透過高解析度電流探棒量測P/G電流,然後將量到的I-T Table匯入Designer內的I_PWL(Piecewise Linear Source)當IC電流源。

IC核心模型以量測的電流來描述其負載行為,I/O特性則用IBIS model描述。

我們把9.3電流探棒量到的IVDD輸出成I-T Table (.csv/.tab),匯入Designer的電流源I_PWL。此時的電流源已經是考慮IC PDN與 封裝寄生RLC的結果。再把以下模擬電路與9.3做比較,近場E/H與遠場EMI幾乎都是一模一樣。

就模擬IC EMI的角度,筆者認為取得實際封裝結構,比取得CPM來的重要,此例即是一個說明。但對於模擬PI最佳化的角度,兩者一樣重要。

10.2 以近場邊界條件來模型化EMI輻射源 ![]()

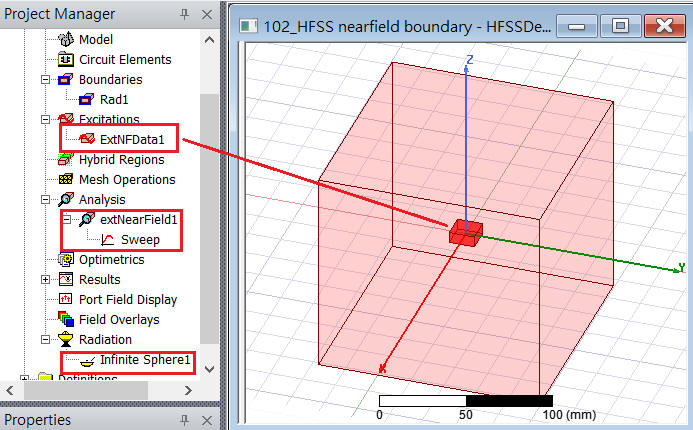

在SIwave內做[Compute Near Field]時,選取以下[Export near field data],會輸出一個矩形(六面體)表面每個頻點的E/H近場值(.and/.nfd)。

請注意這boundary box的絕對座標,寫在.and檔案的檔頭

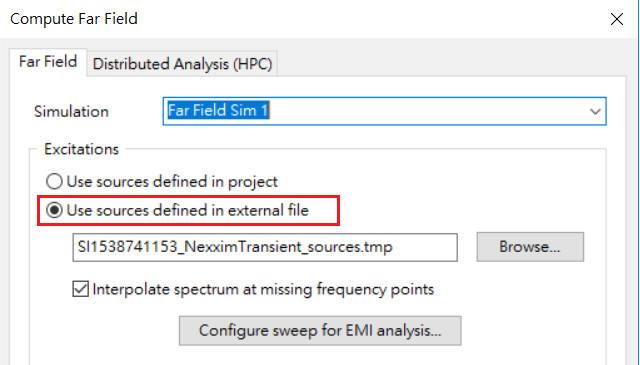

在HFSS相同座標位置,畫一個同樣大小的矩形盒子,使用Assign Excitation \ Linked Field \ Near Field \ Create External Data Design (*.and),把SIwave輸出的.and/.nfd近場定義指定到此矩形盒子,然後就可以在HFSS做Far-filed分析,輸出3米EMI遠場結果。

新版HFSS,只要執行匯入*.and動作,就會自動把其他相關設定都設好,直接可以分析

336MHz H-Field

200MHz E-Field

從上圖模擬可知,即使沒有CPM、沒有IBIS、沒有封裝模型,只要IC供應商能提供從模擬軟體輸出的IC近場E/H模型(.and/.nfd),系統端用戶即可把IC EMI輻射行為重現(EMI頻點完全一致)。

EMC實驗室的遠場EMI,相當於HFSS內的Emission Test Report with Cylinder Plot,這會比Sphere Plot結果會再好一點(3~5dB)。

10.3 透過量測資料來重組(組建)EMI源 ![]()

在不知IC行為下,如何透過近場掃描所得到的資訊,建立IC的EMI模型,也就是"IC輻射源重建"(EMI source reconstruction)?

其觀念很直覺:微觀上用許多小的電場源(electric dipole, current segment)+磁場源(current loop)透過適當的位置配置,合成出IC輻射場的效果。[12]

要怎麼開發出一套演算法找出一個最佳的電場源+磁場源組合方式,最接近實際的IC近場/遠場輻射行為? 人工智慧/機器學習也許是答案。

"IC輻射源重建"這幾年陸續有學界在探討,但一直未達可商用化水平。

由於EMI near-field scaner的掃描結果並不含相位資訊,故只有IC上方1mm高度的2D E/H-filed,也不足以還原IC EMI source。至少要有兩個不同平面高度的近場資訊才能。[13]

由於IC是時變的電磁輻射源,所以就算可以量兩個不同高度的平面電磁場資訊,由於不是同一時間取得,也是無法還原相位。

DesignCon 2022 APREL(一家測試供應商)的CEO以量測資料,認為單以Hx, Hy兩正交角度不足以充份的表現IC EMI行為,必須考慮360度得到的資訊。[15]

也就是說,[12][13][14]這樣的"IC輻射源重建"技術,用來評估IC造成的遠場也許可行,但並不足以用來找出IC的EMI問題點與解決方法,後者需要更精細的模型。但電磁場的近場量測技術,在量測的靈敏度與空間解析度,彼此間是trade-off的。如本文的IEC 61967-6的磁場探棒所示。

另外,"IC輻射源重建"與本文10.2介紹的方法有同樣的限制,無法反映出同一顆IC放在不同接地條件的板子上(不同的系統外在電流迴流條件),該顆IC的EMI輻射是不同的。

要解決以上兩瓶頸,目前最好的做法就是:CPM (IC current+PDN) + SPICE/IBIS (IO model) + Package model。

11.1 CECM模型測試 ![]()

11.1與11.2節CECM使用的ESD元件(Power clamp/Diode)模型,是採用I-V curve描述的簡單行為模型,其元件導通行為是以導通/順向電壓(Vf=0.51V)加上Ron=0.01 ohm貢獻的IR drop壓降描述,而b2b diode則是直接以0.0001 ohm短路表示。這樣的好處是便於觀察一些基本現象。

真實ESD保護元件的行為在平時(穩態)就像是很好的開路電路(可隔離P/G兩端),ESD雜訊出現時則呈現低阻抗短路行為。而簡單的行為模型僅能表現ESD保護元件導通時的特性,無法反映沒有ESD雜訊時的穩態開路特性,所以筆者會建議用電晶體模型(SPICE)取代行為模型(I-V curve),如本文11.3採用作法。

1KV ESD所注入的電流峰值,不管負載是1 ohm或CECM model,都約3.76A

雖然由此可知靜電槍確實是一個電流源模型(電荷傾倒的概念),但如果附載阻抗變化太大(1 ohm-> 10 ohm-> 100 ohm),還是會看到ESD Gun注入的電流波峰有點不同。

+1KV ESD注入IO端的電壓峰值ESD_inj_V1=(0.51+3.78*0.01)+(0.51+3.78*0.01)=1.096V如上圖紅線所示

11.2 IC ESD (off-power)抗擾測試,含CPM+CECM模型 ![]()

11.2.1 ESD 1KV discharge from DQ0 to VSS

從VDDIO-VSSIO的電壓0.5~0.6V可知clamp between VDDIO-VSSIO有起作用,橘色放電路徑是導通的。

暫態分析的時間步長(time step)與ESD元件模型對模擬收斂與否有很大影響<

DQ0 pin端的ESD_inj_V電壓為何沒被限制在0.51+0.51=1.xV,而是7.53V?

Ans : 筆者用transistor level model做這例子也是同樣情況,估計是IC PDN在DQ0 pin端有貢獻歐姆級的阻抗

疑兇如下所示:在DQ0往下(n-diode)有串1.96 ohm電阻,往上(p-diode)有串0.61 ohm電阻

11.2.2 ESD -1KV discharge from DQ0 to VSS

11.2.3 ESD 1KV discharge from DQ0 to VSSIO

11.2.4 ESD -1KV discharge from DQ0 to VSSIO

DQ0 pin端的ESD_inj_V電壓為何沒被限制在-0.51V,而是-10.74V?

Ans : 除了已知的在DQ0往下(n-diode)有串R0_2438=1.96 ohm電阻,n-diode接到VSSIO串了大電阻R0_2486, 同樣地,如果把這兩顆電阻改小,就可以得到比較小的ESD_inj_V。

11.3 系統ESD (on-power)抗擾測試,含CPM+CECM與封裝模型 ![]()

13.1 如果拿不到IBIS I/O模型怎麼辦? ![]()

Ans:建議上美光或Altera官網,下載速度對應的DDR2/3/4或USB/Ethernet I/O模型,或以軟體內建的pattern source (V_PRBS/EYESOURCE/AMISOURCE)近似。

也有一些成熟的商用IBIS模型產生器(如SPISim),可以 只輸入簡單的系統規格或SPICE模型以產生IBIS模型。(ANSYS於2020合併SPISim)

不建議以逆向工程去量出I/O的上升與下降波形,自行刻出IBIS I/O模型。主要原因是量測的I/O上升與下降波形通常含封裝與PCB寄生效應,大部分的人也不熟悉IBIS內除了定義上升下降波形的條件外,還須有其他資訊。可能搞半天你做出一個很不準或語法檢查都過不了的IBIS I/O模型。

13.2 影響HFSS與SIwave遠場EMI模擬差異的來源? ![]()

Ans:

先比較9.4.1與10.2的遠場EMI結果,這兩個求解條件主要的差異是解遠場的技術不同,前者靠SIwave後者靠HFSS。SIwave解出的低頻112/200/224MHz三個頻點的EMI值明顯比HFSS解出的高出許多(10~15dB),其餘則高出一點(5dB)。

再比較9.4.1與9.5的遠場EMI結果,這兩個求解條件除了解遠場的技術不同,整個PCB extraction與下port的方式都不同。SIwave解板子上數位訊號(高速走線)帶出的EMI,與HFSS相比準度是蠻高的,但對於P/G平面帶出的EMI,則是SIwave解的值較高(worse)。相較於我們2016年做的EMI SIwave與HFSS比較,此例SIwave的結果與HFSS更貼近。

HFSS解P/G帶出的遠場EMI比SIwave低,部份原因是HFSS下field port時,無可避免地要在上下多加PEC plane,這對EMI也有一定程度的遮蔽(shielding)效果。

13.3 為何9.4.3沒有I/O toggle的EMI,並沒有比較好? ![]()

Ans:9.4.1/9.4.3遠場EMI所看到的112/224/336/448/562/674MH頻點,並不是IBIS I/O toggle帶出來的(200/400/600/800MHz),而是CPM內定義的IC P/G電流透過P/G plane帶出來的(as 9.1 CPM current spectrum show)。

此例近場H明顯看到336MHz一枝獨秀,但遠場則顯示112/224/336/448/562/674MH頻點都很強,為什麼?

-- 本文SIwave所示的近場,都是以0~1GHz取101掃頻點所得到,如果增加掃頻密度(改成1001頻點),9.4.1的近場H會變成以下

EMI分析時, 不論是近場或遠場,掃頻頻點的取樣密度很關鍵,本文的例子0~1GHz取1001掃頻點比較好

現在我們看到近場H顯示112MHz是最強的頻點了,其諧波112/224/336/448/562/674MHz...的近場H強度在400MHz以後快速遞減,但為何遠場看來1G以內都一樣強?

-- 實務上我們常遇到近場明顯最強的頻點,不一定遠場也最強。

低頻點的近場能量,若無夠長的輻射路徑,即使近場最強,遠場看到的能量不一定最強。(無法輻射出去)

13.4 如何在指定距離的平面上,以頻譜方式輸出近場最大值? ![]()

Ans:

先在指定距離(比方待測物上方3mm) plot E/H field,然後利用Field Calculation定義一個該平面上最大近場值的變數,掃頻繪出該變數值即可。詳情請參考video

13.5 為何少數CPM會看到.inc內所描述的不只有電流源,還有電壓源加一些奇怪的東西? ![]()

Ans:目前可提供IC CPM model的EDA軟體公司,除了ANSYS與Cadence外,還有第三家。

以下這CPM model不是ANSYS的,冤有頭債有主,有問題請找對人負責喔。(軟體產生的模型一般不會有問題,常是使用者自行編輯修改拼貼後出問題,真是被打敗

)

13.6 為何9.2單在SIwave做的near/far-field與9.4.3用Designer Circuit+SIwave

push excitation做的完全不同? ![]()

Ans:9.2與9.4.3的條件都一樣,唯一激發EMI的來源就只有定義在CPM內的電流源

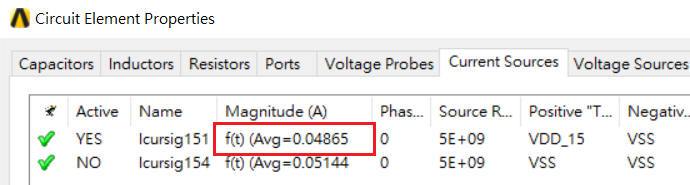

但9.2內的EMI來源是直接以SIwave吃進CPM時自動產生的current source,搭配SIwave解遠場的技術(process cross section)產生,這裡的current source被"平均了"(avg)

9.4.3內的EMI來源是以Designer push excitation to SIwave自動產生的current source ,此電流源是搭配SIwave SYZ真實求解板子後得到的真實電性響應,會更準確。故建議以此模擬手法為準。

13.7 仿10.2手法,我們可以把EMI scanner掃到的IC表面E/H (real, imag)資料,輸入HFSS當IC

EMI模型嗎? ![]()

Ans:不行

EMI scanner能取得的只有一個面的E/H近場資訊(且不含相位),而不是一個空間上六個面組成的立體E/H近場邊界條件,這不足以決定整個空間的輻射行為。如果想這麼做,至少要上下兩面的E/H近場邊界條件 [13]

如果您對於以3D近場模擬EMI的技術有興趣,可以參考 [14]

13.8 為何IC EMC法規IEC62433-早就定義,至今業界還是很少看到CPM model?

(僅大型IC設計公司有,系統廠都拿不到) ![]()

Ans:CPM描述了IC耗電特性(power consumption),與內嵌電容值(embedded de-coupling capacitor, de-cap)。

這兩項特性是IC競爭力的關鍵,IC設計公司非必要當然不會隨便給,所以系統廠、代工廠一般拿不到的。但從今年開始,由於ADAS/AI/比特幣/5G等產業應用的推升,設計挑戰(高速/高耗電)實在增加太快,產業鏈上游的公司(封測廠), 漸漸有機會可以從IC供應商端拿到這CPM,以加速板子的開發時程,並滿足系統SI/PI設計要求。

[1] IC-EMC Homepage

[2] Generic IC EMC Test Specification - ZVEI

[3] Michele Perotti, "A Test Structure for the EMC Characterization of Small Integrated Circuits", IEEE Trans. on Instrum. Meas., vol. 67, no. 6, June 2018.

[4] Introducing IC Immunity Test, such as ESD and Latch-up

[5] IEC 62215, https://webstore.iec.ch/preview/info_iec62215-2%7Bed1.0%7Den.pdf

[6] IEC 62433, http://www.ee.cityu.edu.hk/~emc/20130502P1.pdf

[7] EMC of ICs Model (good)

[8] IEC 62014, https://www.sis.se/api/document/preview/554616/

[9] "INTRODUCING ICIM-CPI TO MODEL THE IC IMMUNITY TO CONDUCTED PULSES", EMC Europ 2017

[10] Ji Zhang, Jayong Koo, "Modeling Injection of Electrical Fast Transients Into Power and IO Pins of ICs", IEEE Trans. on Electromagn. Compat., vol. 56, no. 6, Dec. 2014.

[11] Ji Zhang, "Determining Equivalent Dipoles Using a Hybrid Source-Reconstruction Method for Characterizing Emissions From Integrated Circuits", IEEE Trans. on Electromagn. Compat., vol. 59, no. 2, Apr. 2017.

[12] Qiaolei Huang, "Machine Learning Based Source Reconstruction for RF Desensitization Analysis", DesignCon 2018.

Jun Fan, "Accurate and Fast RFI Prediction Based on Dipole Moment Sources and Reciprocity", DesignCon 2018.

[13] Ji Zhang and Jun Fan, "Source Reconstruction for IC Radiated Emissions Based on Magnitude-Only Near-Field Scanning", IEEE Trans. on Electromagn. Compat., vol. 59, no. 2, Apr. 2017.

[14] Hanen Shall, "A 3-D Near-Field Modeling Approach for Electromagnetic Interference Prediction", IEEE Trans. on Electromagn. Compat., vol. 56, no. 1, Feb. 2014.

[15] Stuart Nicol, "Magnetic Near-field Evaluation Methodology for Integrated Circuit In-package Coupling Assessment", DesignCon 2022.