線上影音

Home > ANSYS Designer 教學 > ESD Gun Model and ESD Simulation

本文始於2011年,並於2013, 2019與2022年更新,分別介紹三種使用Designer電路層級與HFSS電磁場層級實現靜電槍的方法,以及遵循IEC61000-4-2標準的間接式接觸放電環境模擬(這應該是您第一次見到這樣的模擬展示與討論)。

![]() 過去HFSS暫態求解模式(時域求解器)是需要另購的選項,從2018年R19開始變成是產品默認內含的標準配備。

過去HFSS暫態求解模式(時域求解器)是需要另購的選項,從2018年R19開始變成是產品默認內含的標準配備。

-- 更新3.1 與3.2圖於2022.11.10

-

Designer Circuit 2019 R1 實現靜電槍模型

-

HFSS 2019 R1 實現靜電槍模型

-

系統靜電放電模擬

4.3 系統靜電放電模擬

4.3.3 垂直式間接放電模擬 with HFSS 2019 R1

-

問題與討論

5.3 為何一開始"Transient"解完卻看不到場(Field)?

5.4 Lumped RLC boundary可以用在solid的物件上嗎?

5.5 HFSS可以模擬CDM(Charge Device Mode)測試嗎?

5.9 靜電放電時,看H-field與E-field,靜電槍接地端會不會有亮點?

5.10 HFSS暫態求解模式下使用"Lump port"或"Voltage Source"有何不同? (重要)

5.11 如何偵測因靜電放電造成的軟體失效(Class B),與發現根因問題加以改善?

5.12 HFSS暫態求解模式的"Composite Excitation"與"Network Analysis"有何差異?

5.13 靜電槍是以電壓源充電,但放電尖端的波形應該以電壓來定義,還是以電流來定義? (重要)

5.14 靜電放電模擬環境的modeling size (含靜電槍/待測物/接地迴路ground strap),對模擬結果有何影響? (重要)

5.15 靜電放電影響的頻寬範圍是多少? 是300M~1GHz嗎?

5.16 同樣的結構,為何若放電波形從80~100ns放大到80~100ms,求解正常結束後看不到E/H場?

![]()

-

關於系統ESD的EMC法規

1.1 IEC-61000-4-2 or EN-61000-4-2 p.19

從這張圖可以看出,法規是以電流波形來定義靜電槍的輸出。又輸出能量分兩波段,第一段的上升時間很短(0.7~1ns),但電流峰值極高(3.75A/KV),反映的是HBM (Human Body Mode)放電時,手臂累積的電荷瞬間釋放的結果;第二段(10~60ns)則反映身體累積電荷的釋放結果。

注意要點有三:1. 第一根Ipeak=3.75A/KV. 2. 第二波放電的高點出現在30ns前. 3. 60ns處的電流值為30ns處電流值的1/2。

1.2 靜電槍模型

1.2.1 法規定義的基本模型(EN-61000-4-2, p.17)

從這張圖可以看出,靜電槍模型除了由RLC等效電路所組成,還需要兩個時序錯開的開關,實現充電與放電控制。

這兩個"開關"在實作上是以繼電器(relay)實現,而這會引入一些額外的RLC寄生效應。

1.2.2 國外教科書的(放電路徑)模型

雖然以上模型,對負載的放電路徑涵蓋了空氣放電的電弧,但這電弧(arc)的RLC放電模型只能算是behavior model,並不能真的反應空氣放電時,高電場讓空氣中水分子瞬間解離的電弧現象。refer to 4.1, 5.18

1.2.3 法規定義放電電流數學方程式(IEC-61000-4-2 , Part 4-2)

- Designer Circuit 2019 R1實現靜電槍模型

2.1 以兩級RLC模擬身體(135~150pF)與手臂(12~15pF)的兩波放電模型,輸出端以V_probe與I_probe觀察

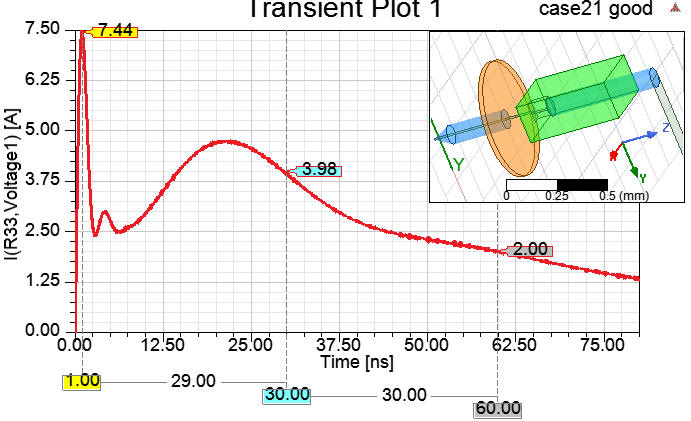

驗證此結果是否滿足法規所定義的放電電流波形:

2KV :Ipeak=7.5A, I=3.9A at 30ns, 第一電流高點出現在1.2-1=0.2ns,且第二波的電流高點出現在30ns前。

(C21,R24)直接影響第一根Ipeak的大小,(L31,R7)直接影響第二段放電(25ns)的波峰大小與出現的時間前後。而充電電容C3到地路徑的寄生RLC,則影響第一電流峰值與第二電流峰值間的凹陷特性,這部分對ESD Gun的影響很關鍵。[4]

此處驗證靜電槍模型的負載條件是低阻抗1 ohm,而不是取50 ohm (IEEE paper[3]也是取低阻抗2 ohm)。靜電槍本身是一種會隨負載(放電迴路阻抗)而異的非理想電流源。

2.2 從法規所提供的基本模型,加上靜電槍對地迴路所引入寄生RLC的放電模型[3][4]

使用I_probe驗證 (2KV放電)

上圖兩個開關在5ns同時導通,可以下載本站附件練習,了解電路如何運作。

2.3 依paper[2][6]所建的靜電槍等效模型

這model雖然是IEEE Trans.的論文,但實際模擬結果卻發現其電流輸出波形與法規所定義略有差異:

第一段電流高點出現時間較慢2.7-1=1.7ns(大於0.7~1ns),且Ipeak=8A (大於7.5A)

第二段電流高點出現時間較慢(30ns之後),且Ipeak=3.6A on 30+1ns (小於4A)

將靜電槍對地的(L215,C200)從(3.5uH,20pF)改成(2uH,12pF),以及把充電電容C191從110pF改成135pF,波形就較理想了。

在[2]內有提到,實際ESD Gun內的充電電容150pF,但模擬/量測重建用的值卻是110pF,為的是讓電流衰減速度fit量測值

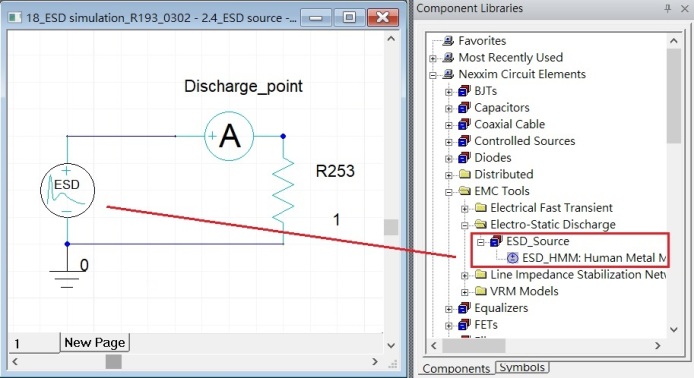

2.4 Designer R19.0內建的靜電槍模型

Designer circuit自R19.0起,把ESD與EFT source都內建了,所以使用者不需要再辛苦的自行兜出SPICE等效電路,可以直接拿來用。

HBM (Human Body Mode)與HMM (Human Metal Mode)這兩種說法都有人用

-

HFSS 2019 R1實現靜電槍模型

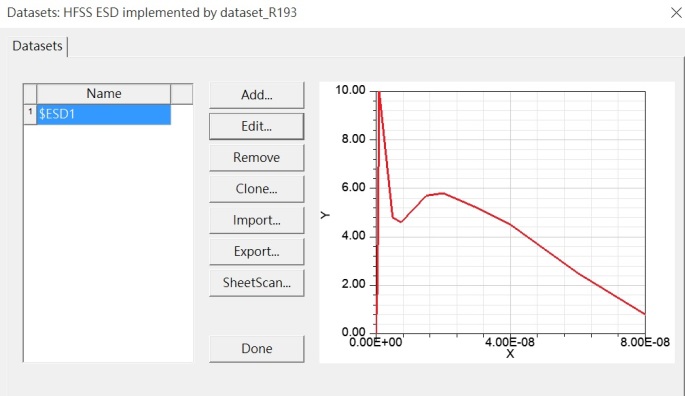

3.1 使用"Dataset"定義的Current Source

[Project] \ [Datasets]

添加"current source"當激發

雙擊 terminal of "current source"以指定樣式 (這操作必須是在Composite Excitation mode of solution type下)

Dataset可以用於lump port/voltage source/current source全部, 但使用lump port/voltage source效果不同。refer to 5.10

由於含低頻能量成份,靜電放電模擬的外圍邊界條件建議以球型取代我們一般SI常用的立方體或Auto-Open option (即使有些例子取Auto-Open option看來也ok)

| 使用auto-open當外圍輻射邊界 | 使用球形的radiation當外圍輻射邊界 (推薦) |

3.2 使用"Lumped RLC boundary"實現靜電槍等效電路

HFSS內無可控制的開關元件(relay), 但可以用Voltage Source引入2KV step waveform當開關元件,通過Lumped RLC boundary組成的靜電槍等效電路(2.2)後放電。

HFSS Transient裡的implicit solver純粹是FETD,hybrid solver則是DGTD(主要)和FETD(次要)的組合。本文範例全部都使用[Implicit solver],因為它的時間步長不受網格裡最小電尺寸的元素限,所以一般消費性電子的題目跑起來會比[Hybrid solver]快。

-

系統靜電放電模擬

4.1 系統靜電放電模擬 know-how

想靠模擬來對沒有抗靜電干擾(ESD immunity)經驗的新設計系統,做事先預防或判定並不容易。不只是ESD,其實EMI亦然。這是因為模擬結果要準確的先決條件是,必須清楚知道想觀察什麼現象,相關範圍內的IC/材料/元件/機構...是否可以拿到模型,或者 有方法可以建近似模型。

首先必須先經過系統分析,將問題範圍收斂,列出最可能的EMC三要素範圍(雜訊源模型、耦合路徑/干擾路徑、接收者/被干擾者),試著以模擬複製出問題現象,接著就可以用模擬來找出根因(root cause)與解決方法。所以靠模擬來做EMC事前的預防性設計,或是事後的問題分析,絕對是可行的,而且也是許多大公司(如Samsung、Apple、Google...)累積研發能量、提升競爭力的方法。

現有的模擬技術,只能做接觸放電(contact discharge),而無法做空氣放電(air discharge),因為目前各家的電磁模擬軟體還沒有人可以模擬空氣因高壓解離所致的電弧放電現象。所以如果要模擬不同的機構卡榫彎折改善ESD竄入的能量差異,目前還做不到。

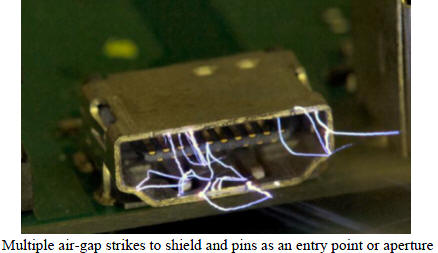

也許有人還有疑問,因為靜電槍離待測物1mm進行電磁模擬,是可以看到能量傳遞效果的[20]。進一步解釋,這只是模擬兩導體間的電容性/電感性耦合的效果,而不含空氣中濕度(水分子)電離所產生的電弧放電(跳火)效果。下圖取自Industry Council on ESD Target Level, White Paper PartII [10]

4.2 系統靜電放電論文[8]

讀者如果是三年以上的EMC資深工程師,或是五年以上的資深硬體工程師,可能有此經驗:某些PCB割地可以增強系統ESD耐受(常見於connector下方與機殼有連接的PCB),但某些PCB割地後反而系統ESD與EMI測試都變差(傳輸線下方離機殼遠的PCB)?

請參閱[8]本站論文導讀,或next section 4.3以模擬來驗證這些現象

4.3 系統靜電放電模擬

4.3.1 ESD打在地平面上,平面阻抗高者(有slot或EBG),抗ESD能力較好。因為阻抗會衰減ESD能量。 simulate by HFSS v15

4.3.2 ESD打在傳輸線(microstrip)上,return path連續者(特性阻抗連續, loop inductance小),抗ESD能力較好。simulate by HFSS v15

分割地可以提高平面的阻抗,理論上會改善ESD抗性,但這如果同時造成訊號線跨不同參考平面,那反而系統的SI/PI/ESD/EMI會變差。另外,地分割還會造成ESD瞬間洩電路徑改變,與系統不同區域彼此之間瞬間電位差較大,這也是造成系統ESD變差的原因。

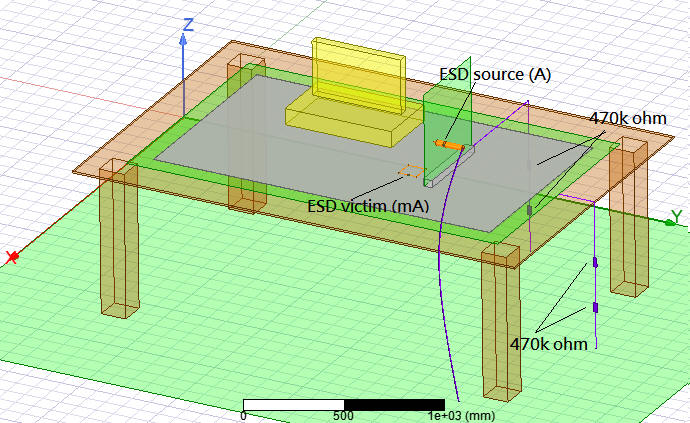

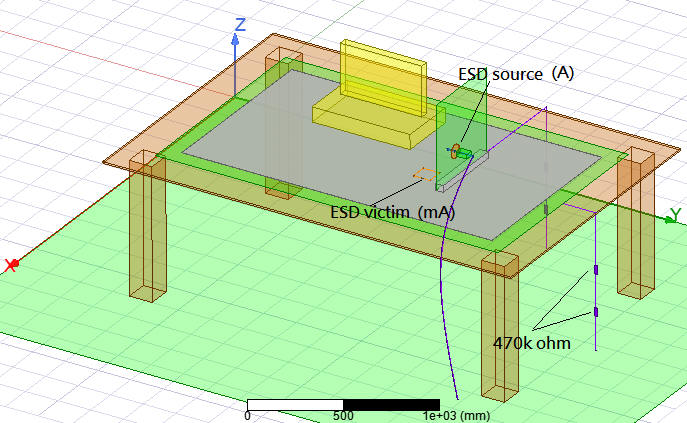

4.3.3 垂直式間接放電with 2019 R1 HFSS

4.3.3.1 使用3.1的靜電槍模型

|

|

當方形金屬環(ESD victim)距離垂直金屬板0.1m (defined by IEC)時,2KV ESD在該金屬環路徑上引起的感應電流/電壓峰值約38mA/38nV。

上圖左在70~80ns時,VCP上仍維持1~5e+4V/m高電場,這是因為VCP接地路徑上有串兩顆470k ohm。對比上圖右邊就衰減的比較快

4.3.3.2 使用3.2的靜電槍模型

跟4.3.3.1非常接近,但I(ESD_tip)最大值 較小(6A),這值小於7.5A筆者反而覺得是比較合理的結果。

13ns時不同的靜電槍模型做的I(ESD_tip)都會突然上升,觀察H場可以看到靜電槍的接地線(ESD ground strap)上有電流往返流動,單方向傳遞時間大約6ns,往返週期12ns正好反應在4.3.3.1的I(ESD_tip)從1ns開始大約每隔12ns有一個小電流上下波動 。refer to 5.9

-

問題與討論

5.1 IC ESD與系統ESD有沒有關係?

Ans:Reference [10] 2012那篇的p.17有一張比較表Fig.1,想說明系統ESD與IC ESD是沒有直接關係的,認為系統ESD要考慮的因素較多,所以IC ESD做好,不代表系統ESD就會好。請注意,這樣的論點與比較是大有爭議的:1.其IC ESD只看HBM沒看MM與CDM,且沒看IC Latch-up. 2.其比較方式也沒有在同樣的系統設計環境下。試想,對於低階的消費性產品,增加一顆0.1uF電容都斤斤計較的前提下,對手的IC直接放到板子上replace,系統設計條件一模一樣,用你家IC的系統ESD表現(雜訊耐受力)就是比較弱,而你還覺得跟IC無關,那你就等著被淘汰吧。所以,這問題應該換個方式問:同樣的系統設計條件下,IC ESD與系統ESD是否直接相關?

筆者完全同意:"系統ESD要考慮的因素較多,所以系統ESD要好,不只是IC要夠強壯、FW robust、strong WDT(watch dog timer)、system level PCB layout and components selected...這些都很重要。我想只要各位有幾年實際的IC量產經驗,不難發現好的IC ESD耐受能力,對IC市場競爭力是有絕對幫助的,但回頭來,同樣要有本事增加IC ESD(含HBM,MM,CDM)與Latch-up能力,但盡可能不增加IC成本,那才會gain到競爭力。否則大家只是在對於雜訊耐受度這件事上,爭論是靠IC cover還是靠系統cover。答案很簡單,誰做到利潤就歸誰,你把責任往外推,你就等著被幹掉。

IC ESD為何要有三種測試HBM、MM、CDM,因為這三種測試能分別qualify不同的放電模型與放電路徑,尤其是CDM能抓出IC內訊號跨不同pwr/gnd domain之間所造成的抗雜訊能力變差的問題。

也許有人還是質疑筆者的說法:認為IC ESD在意的是IC damage,而系統ESD在意的是system downgrade,兩者是不同的,為何筆者說兩者相關? 解釋這原因要從IC內是怎麼做ESD防護來說,其實也是宣洩雜訊(RC推MOS的暫態路徑)、clamping voltage ...,跟系統防護的觀念是一樣的。所以系統ESD不好,有可能是系統功能downgrade,也有可能是IC功能downgrade,你不會知道量產時不同的model遇到問題,何者是系統面dominate、何者是IC面dominate,所以兩者都要做好。

爭論IC ESD與系統ESD有沒有直接關係,所衍伸的廣義討論即是"IC的雜訊耐受能力"與"系統的雜訊耐受能力"有沒有直接的關係。目前定義系統雜訊耐受測試主要有ESD, EFT與雷擊測試。

5.2 如何在HFSS暫態(時域)分析下得到S參數?

Ans:只有"Transient" solve + "Network Analysis"可以在[Report Rectangular]時,把[Transient]切換到[Spectral]看S參數

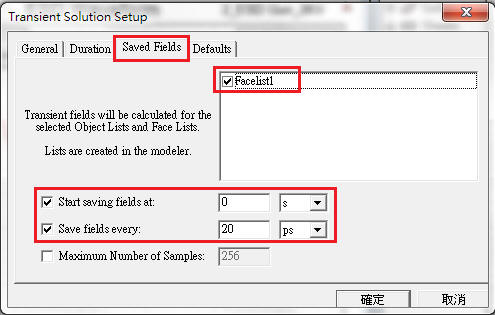

5.3 為何一開始"Transient"解完卻看不到場(Field)?

Ans:在Transient mode要看場,必須先設定

-- 選擇要觀察的面,從 [Modeler\ List\ Create\]增加list,並於下方設定視窗內勾選該"face list"

-- 在setup設定視窗第一頁,勾選"save field"

5.4 Lumped RLC boundary可以用在solid的物件上嗎?

Ans:對於HFSS頻遇模擬,是可以的,但對於時域模擬引擎,"Lump RLC boundary"只能放在矩形無厚度平面(sheet)

5.5 HFSS可以模擬CDM(Charge Device Mode)測試嗎?

Ans:只使用HFSS不行,因為HFSS無法描述電荷累積在非導體(介質)上,瞬間因空氣放電而流動的現象,但HFSS+Circuit model則有人做[21]

CDM是靜電荷先透過高電場耦合累積在裝置上(非導體+導體的整個裝置,如封裝),瞬間大量的靜電荷對鄰近的導體/接地點進行放電(屬空氣放電, 電弧arc),導致帶電體本身有瞬間大電流流動,對自身造成靜電破壞。所以不管是充電模式的行為或放電模式的行為,都不是單純馬克斯威爾方程式所描述的範疇。

5.6 本文所介紹的三種靜電槍模型,其個別優劣為何?

Ans:sec. 2.1的方法,是筆者以手臂與身體兩段式放電的概念所建立,其行為與sec. 2.2的方法[3][4]差不多,Ipeak的出現都又快又尖。Section 2.3的方法,雖自2003年起在IEEE一直被引用([2][6][7]同一批研究團隊),但其Ipeak的出現時間較慢也較粗。

5.7 哪些因素會影響HFSS暫態分析的求解速度?

Ans:

暫態分析有兩個過程,一是mesh solve,二是transient sweep。前者時間與3D geometry大小與複雜度有關;後者跟求解題目能量場隨時間變化的特性有關。短時間內能量變化劇烈的問題(寬頻的問題,求解需要較小的time step),transient sweep時間會較長。

對於HFSS暫態分析,其delta error可以設0.1~0.01,值設越小模擬時間越久。筆者的習慣是至少讓它refine mesh三~五次,避免時域模擬出現震盪(不收斂)。

5.8 觀察ESD電壓分佈與電流流動,要觀察電場還是磁場?

Ans:電壓(落差)越大處,電場越強,又電荷的流動產生磁場。所以ESD電壓分佈看電場,ESD電流分佈看磁場。

看電壓亮點分佈與電流亮點的分佈是具有不同意義的,而系統元件是死在過電壓(EOS)還是過電流(ESD)則是另一個問題;一般ESD測試中,元件損毀(Class D)常是因為瞬間短暫過電流擊穿IO,或是ESD觸發CMOS IC內Latch-up而導致IC發燙燒毀。

5.9 靜電放電時,看H-field與E-field,靜電槍接地端會不會有亮點?

Ans:以3D EM tool做ESD模擬分析時,看E-field(電壓)時,只有ESD Tip放端有亮點;看H-field(電流)時,則會看到放電端與接地端都有亮點。

在HFSS內不論是以哪一種方法實現靜電槍模型,在做系統ESD模擬時都會看到在靜電槍打出能量的同時(at 1ns),也會有一股電流從靜電槍透過接地線往參考地迴流(at 1ns~7ns)。原因是:實際的靜電槍是透過繼電器(relay)與直流電壓源對150pF電容作兩階段充/放電時序切換,而在FEM環境內則是把本文2.2的等效電路中的前級開關(V114)直接以一個2KV step waveform取代,這造成C3(150pf)一端電壓瞬間拉高,連帶也把C3另一端電壓也拉高,造成我們看到在ESD strap上有電流流動。

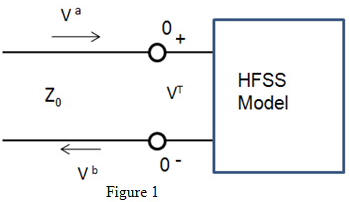

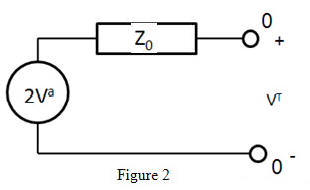

5.10 HFSS暫態求解模式下使用"Lump port"或"Voltage Source"有何不同?

Ans:HFSS Help有說明暫態(時域)模擬可以使用Wave port/Lump port/Voltage Source/Current source/Incident wave,且在HFSS driven terminal下使用dataset定義的voltage source,模擬結果會與電路模擬引擎(as Designer circuit)結果相同。但若以同樣的dataset定義的lump port則模擬結果會明顯較大。

關於這問題,查看HFSS Help內[Excitations in Time Domain]有詳細解釋:下圖1是driven terminl lump port時暫態模擬做法,經過柯西赫夫定律電路等效成下圖2,也就是voltage source或電路模擬引擎的做法。所以,如果在HFSS暫態使用Terminal Port (as lump port in driven terminal),那dataset輸入電壓要*0.5才會與voltage source或電路模擬結果相同。

One needs to be careful when comparing results with a circuit tool or textbooks using the voltage source shown in Figure 2. If one volt is used for the voltage source in the circuit simulator, this should be compared with a HFSS transient simulation with edit sources set to 0.5 volt. |

另外,Lump port必須透過Perfect_E與Lumped RLC boundary連接,才能抓到terminal,而Voltage Source則沒這限制。

若把原lump port的design複製,改成voltage source excitation,會發現原"Max. Delta Energy"從0.01自動改成0.1。

5.11 如何偵測因靜電放電造成的軟體失效(Class B),與發現根因問題加以改善?

Ans:三星於2011年發表一篇IEEE Transaction paper[9]. 如筆者先前所言,模擬EMC的重點在於:必須先經過系統分析,將問題範圍收斂(如step5或下圖所示),然後再模型化題目與試著以模擬複製EMC問題。

5.12 HFSS暫態求解模式的"Composite Excitation"與"Network Analysis"有何差異?

Ans:

5.12.1 對於"Composite Excitation",不同port可以有不同激發源。激發源的型態,可各別在Excitation屬性內設置(彼此可不同定義),模擬時同時計算。

5.12.2 對於"Network Analysis",所有激發源都是一樣的。激發源的型態,移到Solution Setup內一起設置,彼此的激發定義都一樣。

只有"Composite Excitation"可以使用[Dataset]當激發,其不能輸出S參數也不支持差動對,只支持 "Discrete sweep",不支持"Interpolate sweep"。

"Composite Excitation"解寬頻的場較快(尤其對於多port激發源的例子),但如果同時需要看S-parameter或differential pair就不行。

5.13 靜電槍是以電壓源充電,但放電尖端的波形應該以電壓來定義還是以電流來定義?

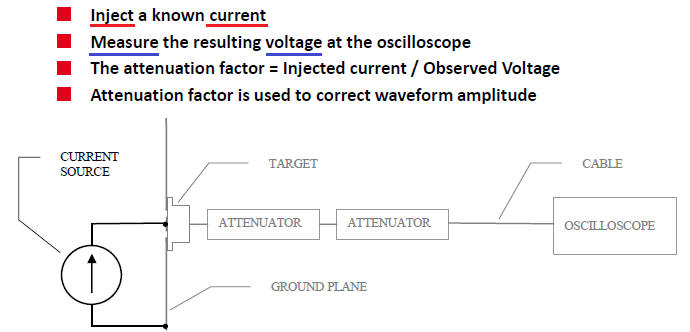

Ans:靜電槍打出的是電流脈衝(電流源),法規定義的也是放電電流波形(如本文sec. 1.1, 2.3),但儀器設備廠商或量測中心在做ESD Gun的校正時,其實是透過衰減器,直接用示波器量電壓的,電流脈衝經過30dB衰減後進入示波器,量測上升時間[14]。

上圖的TARGET是一個很關鍵的裝置,它實際樣子如下圖所示,中間是電流輸出點而周圍被一圈接地點環繞,本身是一個coaxial connector。

測試系統的配置如下圖所示:把靜電槍輸出透過TARGET與衰減器後,接到示波器[14]

5.14 靜電放電模擬環境的modeling size (含靜電槍/待測物/接地迴路ground strap),對模擬結果有何影響?

Ans:

本文step3的ESD模擬系統3D尺寸很小,大約只有7mm*7mm*7mm,所以看H-field時只看到靜電槍放電點與ground strap接地點幾乎同時亮起來,也看不出ground strap上的電荷是如何流動的。只要試著re-scale from mm to meter(放大10~100倍),即可觀察到能量隨時間擴散的現象。

當把3.2 ESD Gun單位放大10倍(re-scale from mm to cm),ESD current profile的第一根峰值下降且波形上會載一個ringing,這主要是整個放電迴路的阻抗與電感都增加了。

| 10x times scaling | 100x times scaling |

Reference [3]有整理一個很不錯的表格:

5.15 靜電放電影響的頻寬範圍是多少? 是300M~1GHz嗎?

Ans:No.

首先說明的是:ESD源波形與頻譜,跟ESD打到PCB上,傳遞到IC端最後看到的波形與頻譜是不同的。另外,接觸放電與空氣放電的波形/頻譜也有差異。

第二個重點:ESD放電能量頻譜是寬頻的。我們可以從模擬的結果,與2010 IEEE paper [15]清楚了解此事。

所以旁路電容(去耦合電容),並不是有效的ESD防護元件。好的ESD防護元件要能夠快速宣洩從極低頻到高頻(數百MHz)的電流雜訊,且本身要對被保護電路貢獻最小的寄生效應。所以筆者不認為也不清楚何來ESD是300M~1G雜訊的說法。

2010 IEEE paper [15]

以本文2.1為例(with 1.1KV),得到的ESD source波形與頻譜模擬結果

5.16 同樣的結構,為何若放電波形從80~100ns放大到80~100ms,求解正常結束後看不到E/H場?

Ans:

雖然是同樣的結構,但當輸入訊號波長變大1e+6倍,此結構的電尺寸(electrical size)等效變成小1e-6倍。對於HFSS時域求解器,面對這樣的特殊情況(極小電性尺寸且含接近DC的能量傳遞),建議做法是使用zero-order搭配solver inside。

5.17 有沒有實際產品從IC到板端的全系統級靜電失效分析成功案例,最好還有模擬與量測比對?

Ans:本論文是韓國蔚山大學自2017年首篇以HFSS做PCB板系統ESD快速分析[16],至2019年進一步以HFSS搭配HSPICE從IC電路到系統PCB完整的ESD電路失效分析[17]。

非常好的一篇實踐型論文,沒有特別艱深難懂的理論基礎,就是把IC電路與系統寄生效應老老實實模擬與量測比對。看似簡單的一篇論文卻是目前為止筆者認為最好最完整的系統級ESD失效分析(可以看到IC內每個邏輯閘受ESD雜訊干擾時的狀況)。

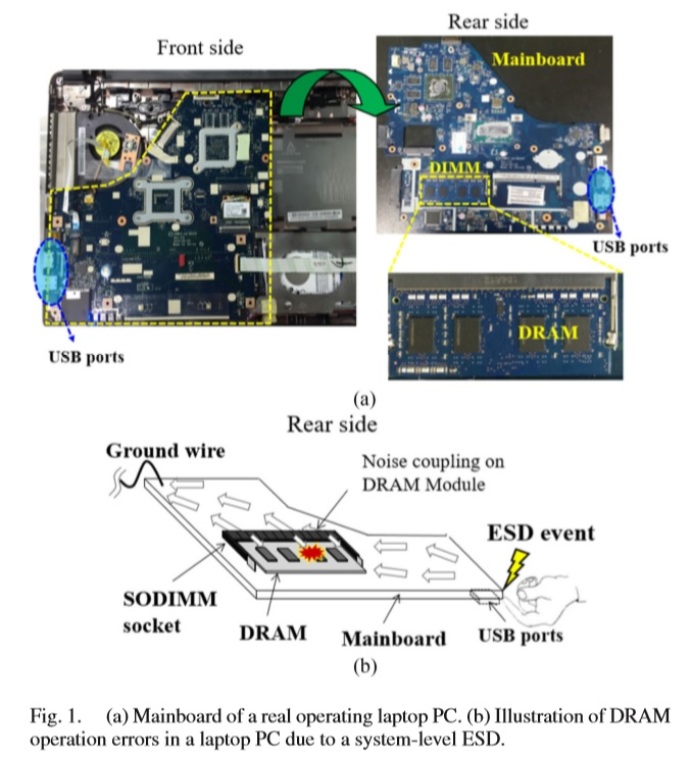

原系統(筆電)電路板,USB接口靜電測試會導致DRAM失效

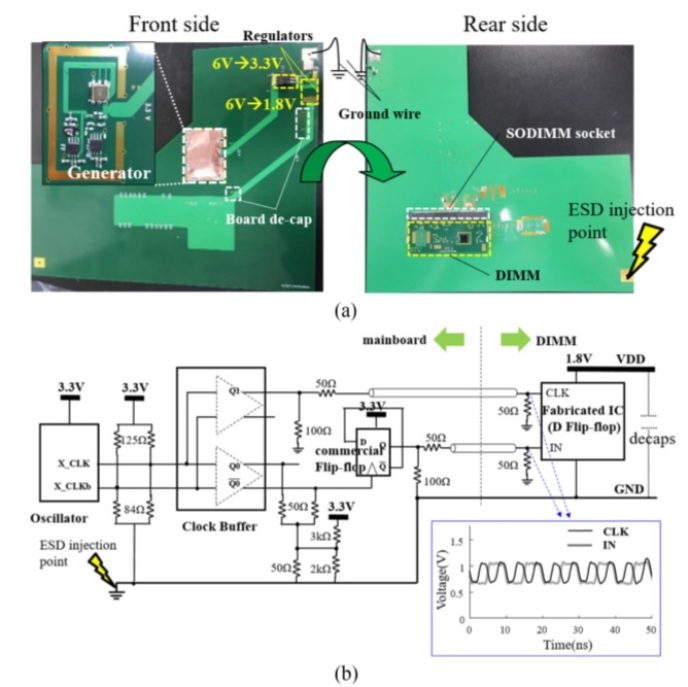

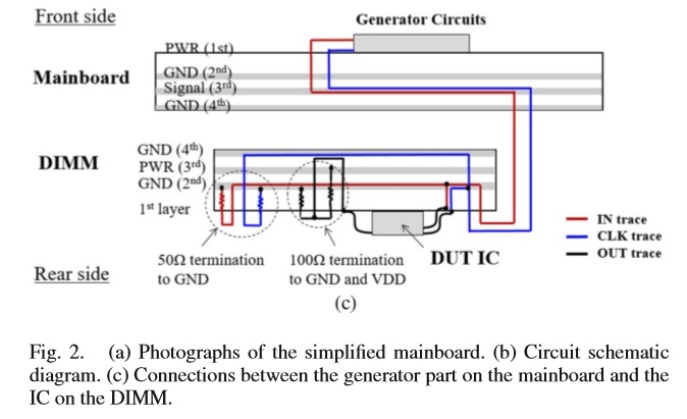

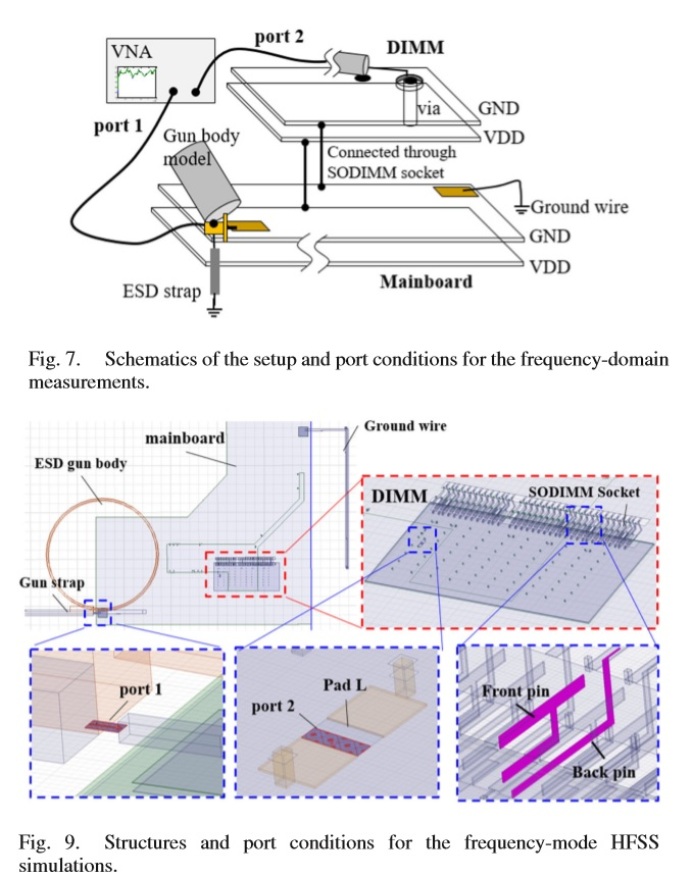

用於做模擬與量測的簡化電路板與測試IC(只有CLK與D Flip-Flop)。雖然有簡化,但維持PCB尺寸、佈件相對位置 、主板與DIMM子板的socket連接...等關鍵特性,以確保準度足以分辨ESD對策的有效性。

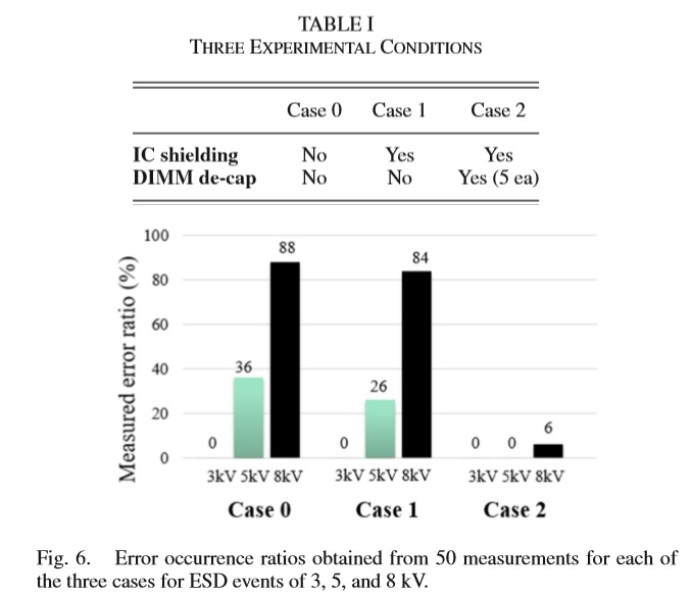

有下對策(case1, case2)與沒下對策(case0)比較,打ESD 50次統計結果

HFSS模型

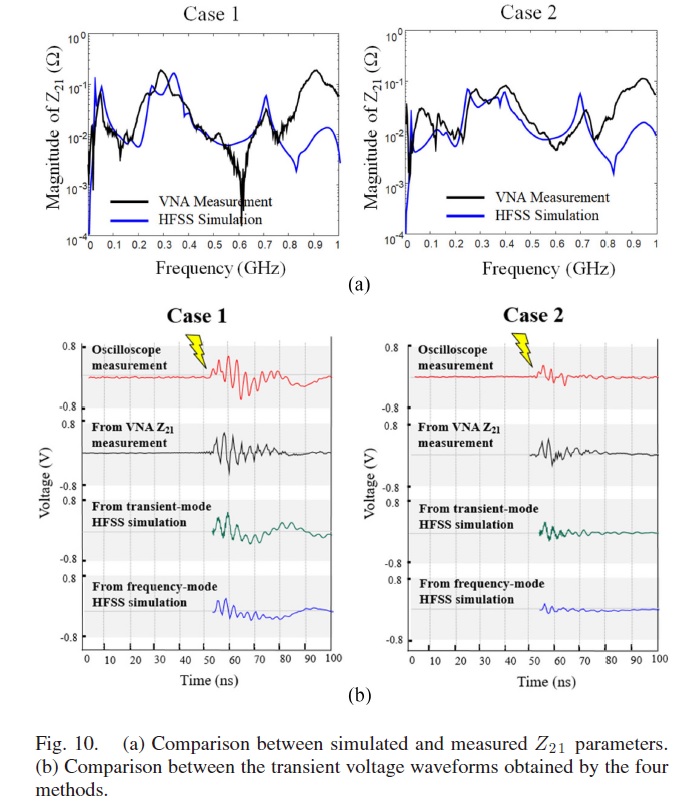

- 模擬與量測結果對照(with HFSS)

5.18 本文4.1強調全波電磁場模擬不能做空氣放電,為何2011年IEEE有一篇期刊論文就是這麼做?

Ans:

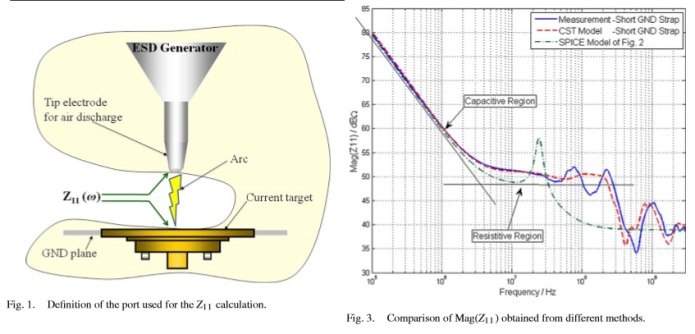

該論文[20]首先以全波電磁場求解器萃取出整個放電路徑模型,並以量測與SPICE模型驗證其Z11

關鍵是其SPICE等效電路模型定義了一個時變的電阻R_arc (Fig2 in paper)來作為模擬空氣放電行為的依據。也就是說要模擬空氣放電不是單靠全波求解器就能辦到,必須搭配等效電路模型R_arc.

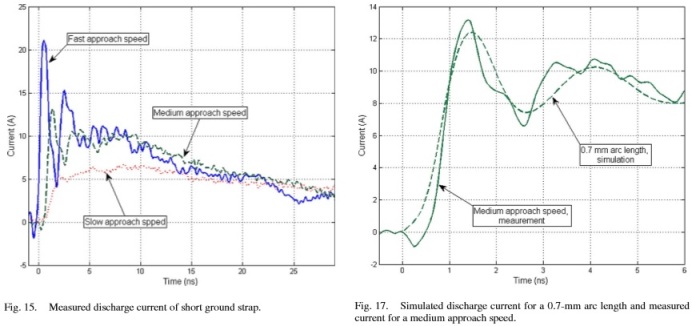

接著模擬靜電槍分別放三個距離0.3mm/0.7mm/1.1mm,接收端看到的放電波形,與量測做比對。值得一提的是:以控制靜電槍在空氣放電時靠近帶測物的速度來對比不同空氣放電距離。

[1] IEC-61000-4-2 or EN-61000-4-2

[2] K. Wang, D. Pommerenke, "Numerical Modeling of Electrostatic Discharge Generators", IEEE Trans, Electromagn. Compat., 2003. (推薦)

[3] F. Centola, S. Caniggia, "ESD Extraction Model for Susceptibility Study", 2003

S. Caniggia, F. Maradei, "Circuital and Numerical Modeling of Electrostatic Discharge Generators", 2005. (推薦)

S. Caniggia, "Circuit and Numerical Modeling of Electrostatic Discharge Generators", 2006.

S. Caniggia, "Numerical Prediction and Measurement of ESD Radiated Fields by Free-Space Field Sensors", 2007.

M. Borsero, S. Caniggia, "A New Proposal for the Uncertainty Evaluation and Reduction in Air Electrostatic Discharge Tests", 2008.

[4] 邱冠銘, "Simulation and Measurement of ESD Test for Electronic Devices", 中山大學碩士論文, 2004 (推薦)

[5] "Modeling the Susceptibility of Enclosures to ESD and the Effect of Attaching Cables". CST, 2012

[6] J.koo, Q.cai, "Frequency-domain measurement method for the analysis of ESD generators and coupling", IEEE Trans. on Electromagn. Compat., 2007.

[7] F. zur Nieden, D. Pommerenke,"A Combined Impedance Measurement Method for ESD Generator Modeling", EMC Europe, 2011

[8] D. C. Smith, Ed Nakauchi, "ESD Immunity in System Designs, System Field experience, and effects of PWB layout", EOS/ESD Symposium Proceeding, 2000 (推薦)

[9] K. H. Kim, Y. Kim,"Systematic Analysis Methodology for Mobile Phone's Electrostatic Discharge Soft Failures", IEEE Trans. on Electromagnetic Compatibility, 2011. (推薦)

[10] System Level ESD Part I : Common Misconceptions and Recommended -- 2010

System Level ESD Part II : Implementation of Effective ESD Robust Designs -- 2012[11] Characterization, modeling, and design of ESD protection circuits (book)

[12] Jing Li, Jun Fan, "The Application of Spark gaps on Audio Jack for ESD Protection", IEEE EMC Society, 2013. (推薦)

[13] R. Myoung, "Chip-Package-System ESD Simulation Methodology with Chip ESD Compact Model", DesignCon2014. (推薦)

[14] Greg Senko, "ESD Simulator Verification", p.34,48, EMC Society 2010

[15] Janusz Baran and Jan Sroka, "Distortion of ESD Generator Pulse Due to Limited Bandwidth of Verification Path", IEEE Trans. Electromagn. Compat., 2010.

[16] Junsik Park, Jongsung Lee, "Fast and Accurate Calculation of System-Level ESD Noise Coupling to a Signal Trace by PEEC Model Decomposition", IEEE Trans. Electromagn. Compat., 2017.

[17] Myungjoon Park, Junsik Park, "Measurement and Analysis of Statistical IC Operation Errors in a Memory Module Due to System-Level ESD Noise", IEEE Trans. Electromagn. Compat., 2019. (推薦)

[18] Ahmad Hosseinbeig, Omid Hoseini Izadi, "Methodology for Analyzing ESD-Induced Soft Failure Using Full-Wave Simulation and Measurement", IEEE Trans. Electromagn. Compat., 2019.

[19] Darwin Zhang Li, Shubhankar Marathe, "Full-Wave Simulation of System-Level Disruption During Secondary ESD Events in a Smartphone", IEEE Trans. Electromagn. Compat., 2019.

[20] Dazhao Liu, Argha Nandy, "Full-Wave Simulation of an Electrostatic Discharge Generator Discharging in Air-Discharge Mode Into a Product", IEEE Trans. Electromagn. Compat., 2011.

[21] Dolphin Abessolo-Bidzo, "CDM Simulation Based on Tester, Package and Full Integrated Circuit Modeling: Case Study", IEEE Trans. on Electron Device, 2012.

[22] CDM Circuit Model

[23] ESD相關技術 by 柯明道