# Chip-Package-System ESD Simulation Methodology with Chip ESD Compact Model

Robert (Soung Ho) Myoung\*, Norman Chang\* Byong-su Seol\*\*

January 28-31, 2014 | Santa Clara Convention Center | Santa Clara, CA

# Agenda

- System level ESD Testing

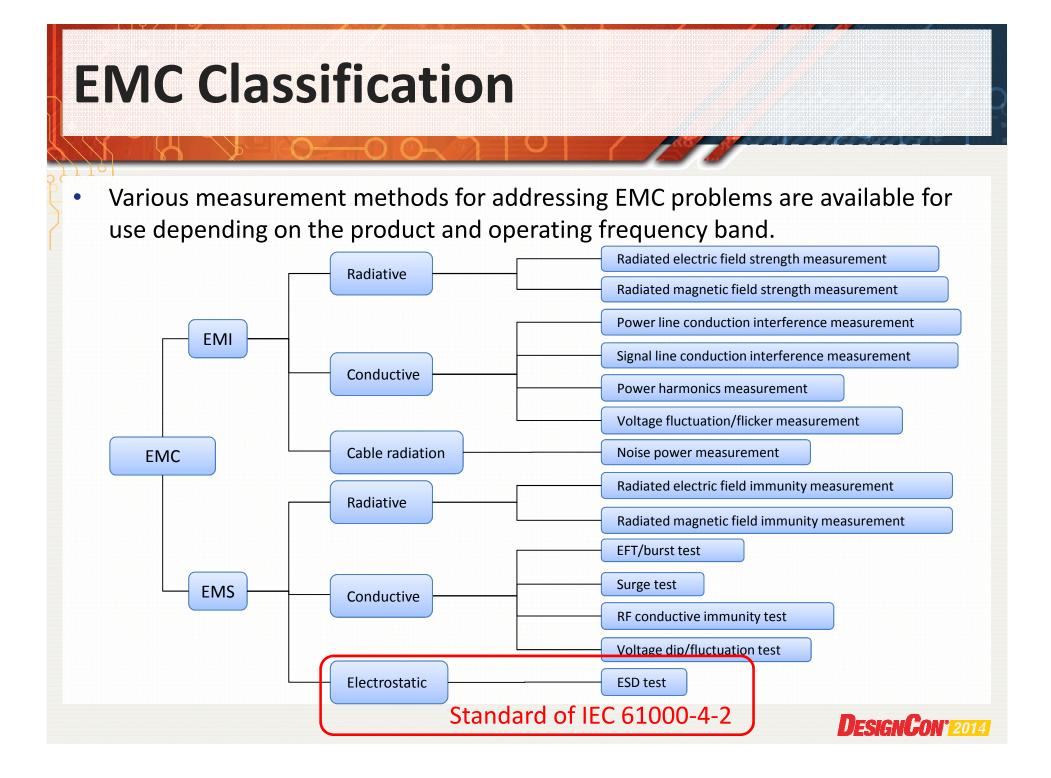

- EMC Classification

- What is ESD?

- CPS ESD Simulation Methodology

- A comprehensive Chip-Package-System (CPS) ESD dynamic methodology

- Modeling for CPS ESD Simulation

- ESD and ESD Modeling

- Chip ESD Compact Model

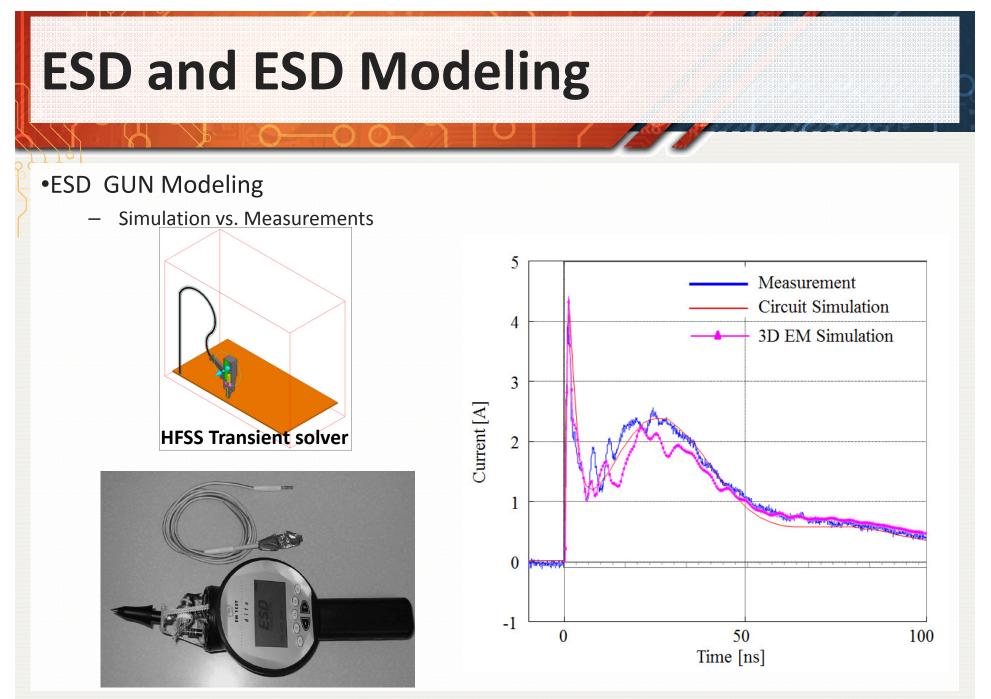

- ESD Gun Modeling

- Equivalents Circuit ESD Gun

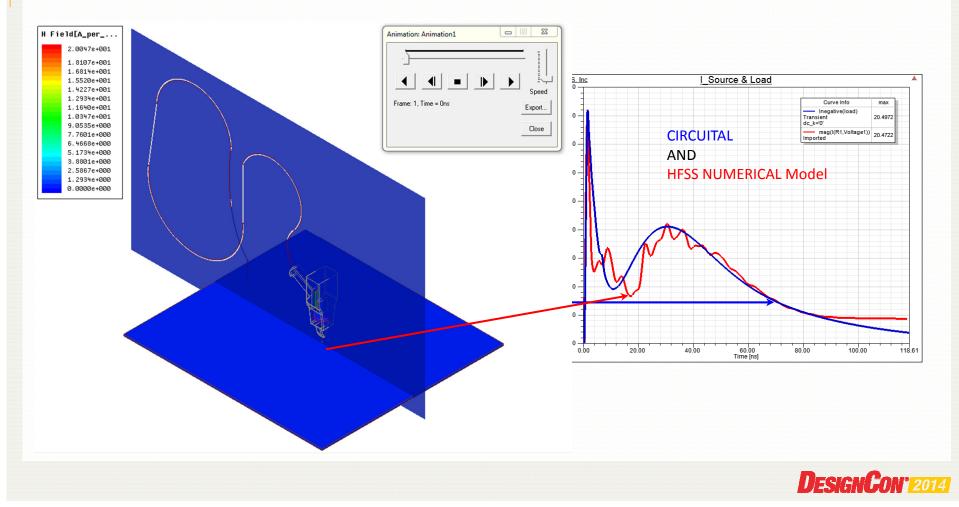

- Full 3D ESD Gun with HFSS Transient Solver

- TVS Diodes, CMF/EMI/ESD Filter

- Connector and PCB Modeling

- Full 3D Mobile Device ESD Simulation

- Case Study 1; Micro USB Connector Device on Mobile PCB

- Understand ESD Propagation on Complex PCB with Connector

- Case Study 2; Mobile System-level ESD propagation modeling

- Predict Chip pin V(t) ,ESD propagation Prediction

- Conclusion

#### **System level ESD Testing** The Mobile system ESD test platform that incorporates • All major components of a converged Device — Chip/Package PCB, Connectors ANSYS Housing Battery Components Etc... Cells

DESIGNCON<sup>®</sup> 2014

## What is ESD?

#### • Answer is;

Electrostatic discharge (ESD) is the sudden and momentary electric current that flows between two objects at different electrical potentials...unwanted currents that may cause damage to electronic equipment. (from *Wikipedia*)

#### • Various mechanisms can contribute to the EMS problem

- ESD is multi-physics issue

- Time & Frequency

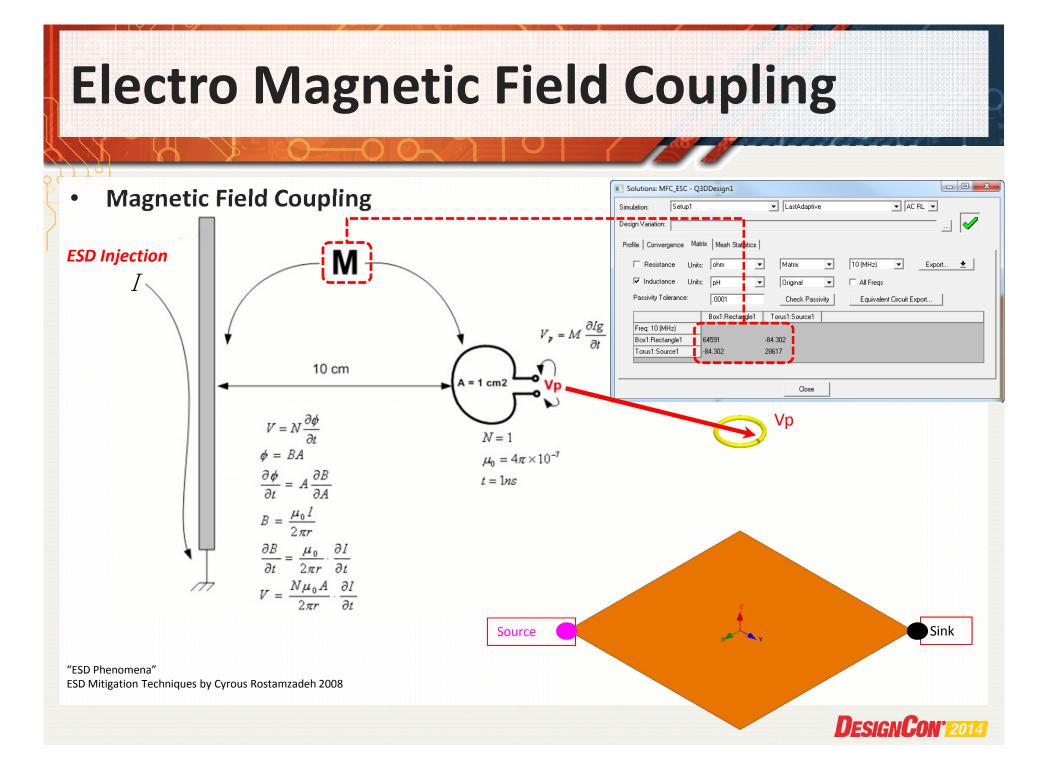

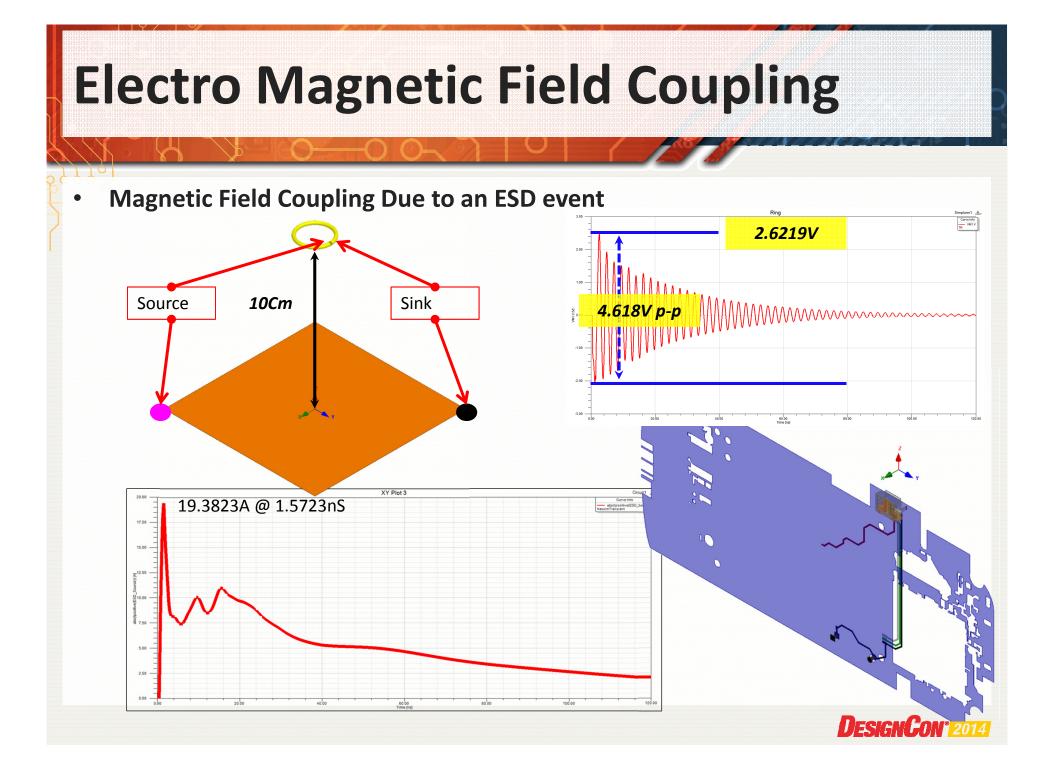

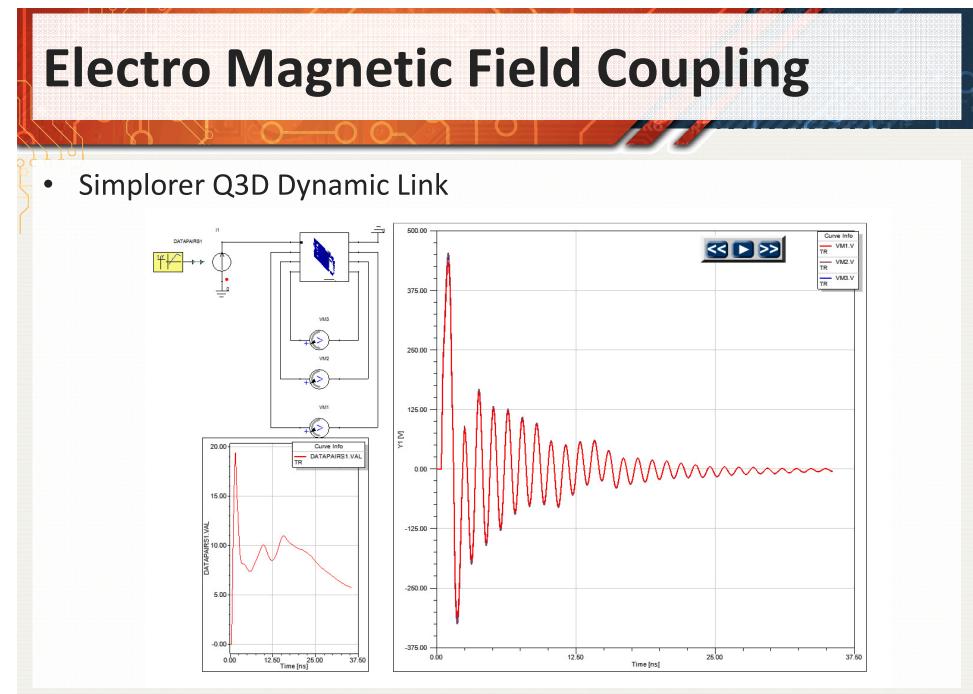

- Electro Magnetic Field Coupling

- magnetic induction, conduction etc.

DesignCon<sup>®</sup> 2014

## **Electro Magnetic Field Coupling**

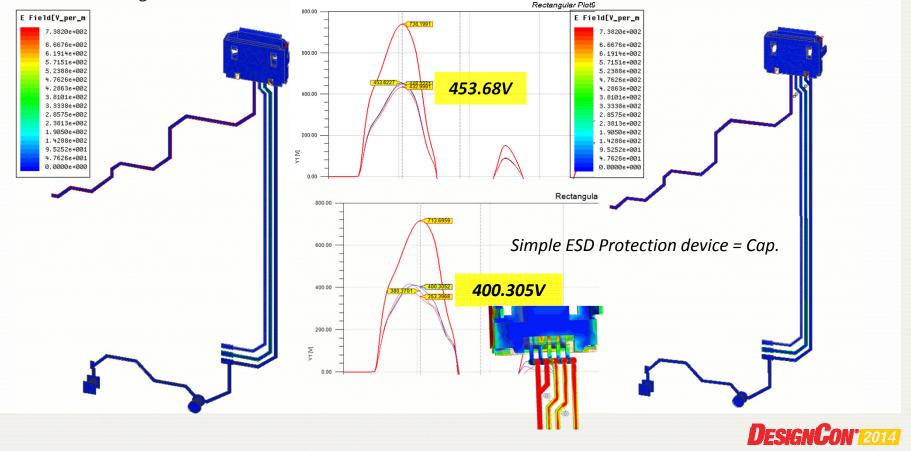

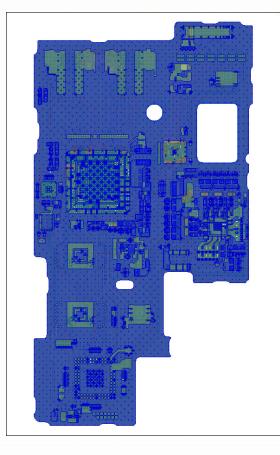

- ESD susceptibility map on printed circuit board trace with ESD Protection device

- ESD susceptibility map for printed circuit board is presented and the mechanisms that the ESD event couples into the digital devices is demonstrated.

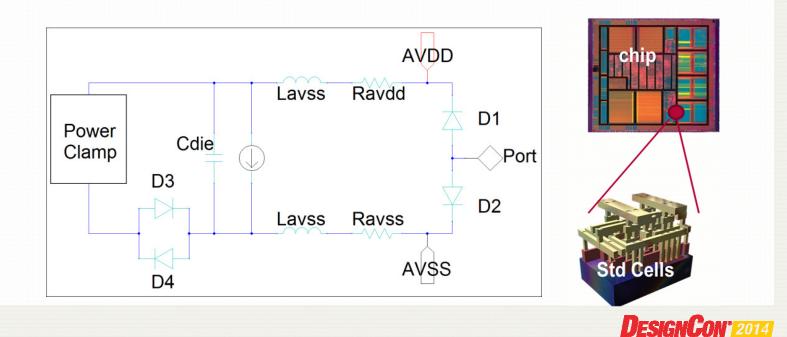

#### Chip ESD Compact Model

- Chip ESD Compact Model (CECM) provides a reduced RLC network among ports and per port demanding current for the chip power-on status with a chosen chip operation vector

- On-chip decaps are modeled including intrinsic device decap, power/ground cap, intentional decap, and effective loading cap

- On-chip diodes/clamps can be included in the model when generating from RedHawk Pathfinder-S which is on-chip ESD analysis tool

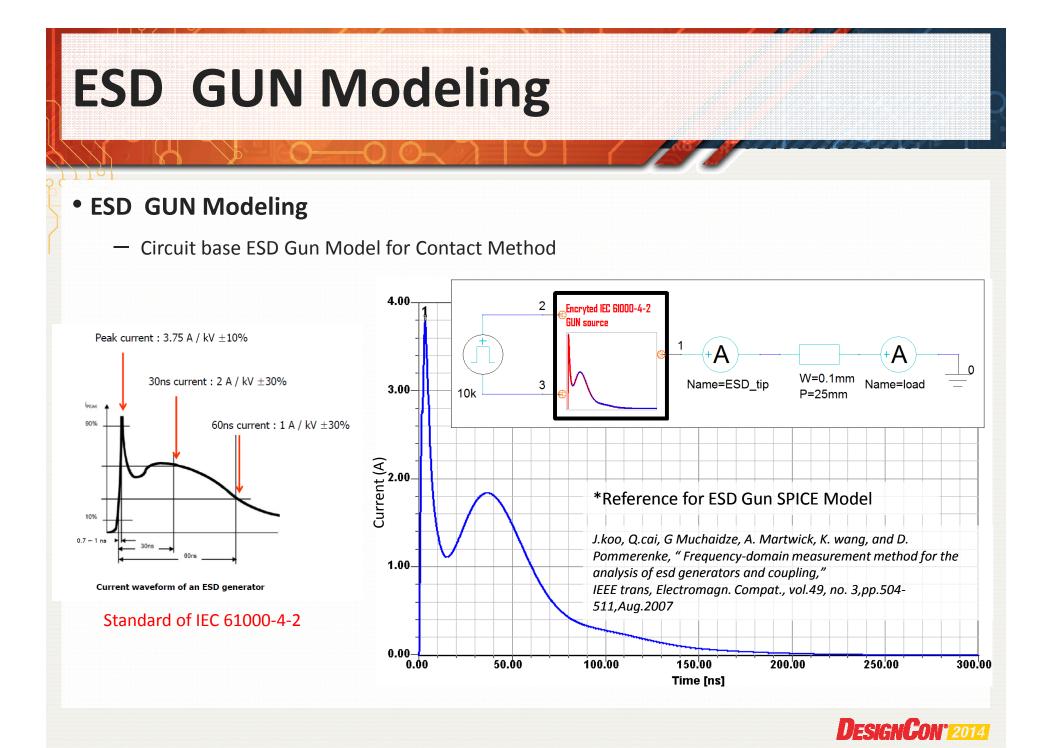

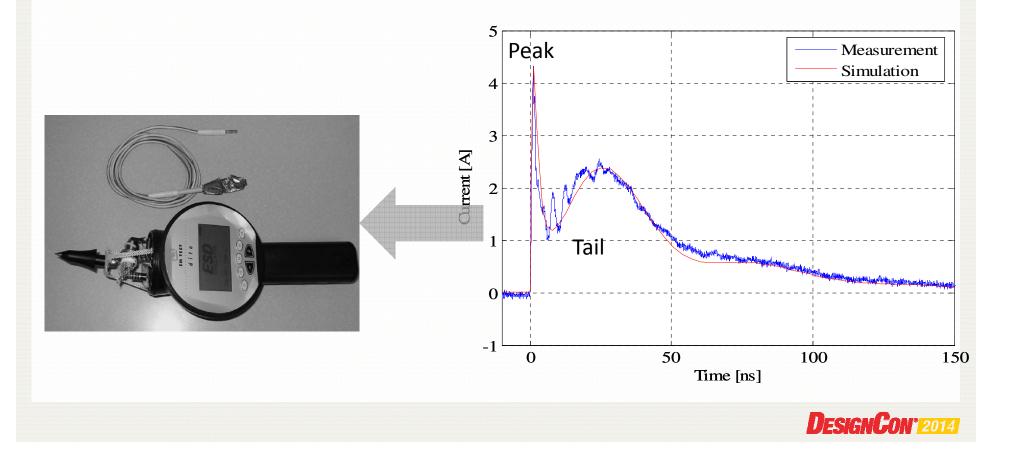

#### •ESD GUN Modeling

Circuit base ESD Gun Model for Contact Method

(Between EM test DITO and SPICE model in DesignerSI)

DESIGNCON<sup>®</sup> 2014

#### • ESD Gun

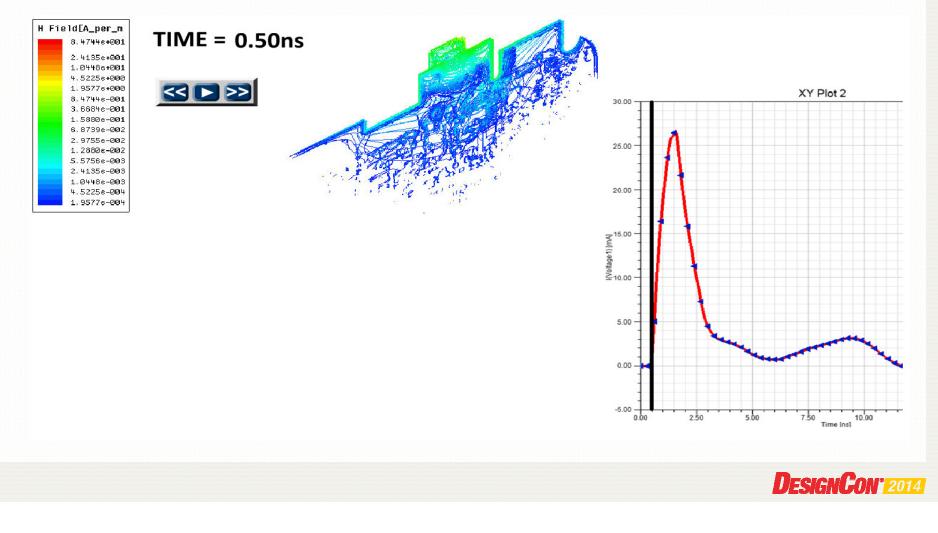

- Time-varying Magnetic Field with Discharge Current waveform

0

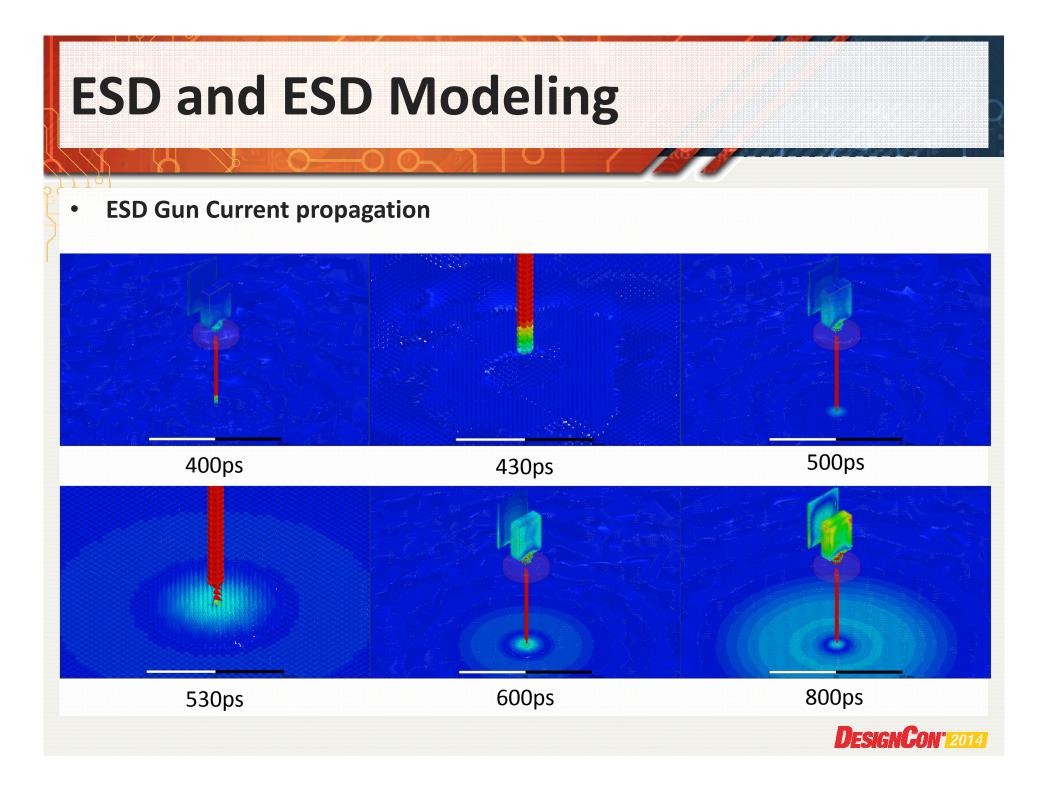

• ESD Gun Current propagation

ESD Current propagation; Ops to 5ns 10ps frame

250

500 (mm)

DESIGNCON<sup>®</sup> 2014

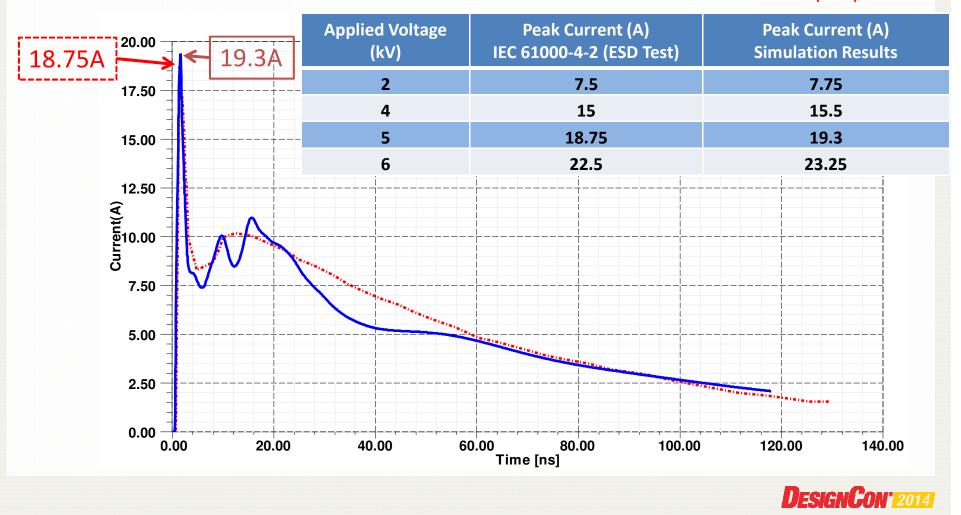

#### • 5KV ESD Discharge Current waveform

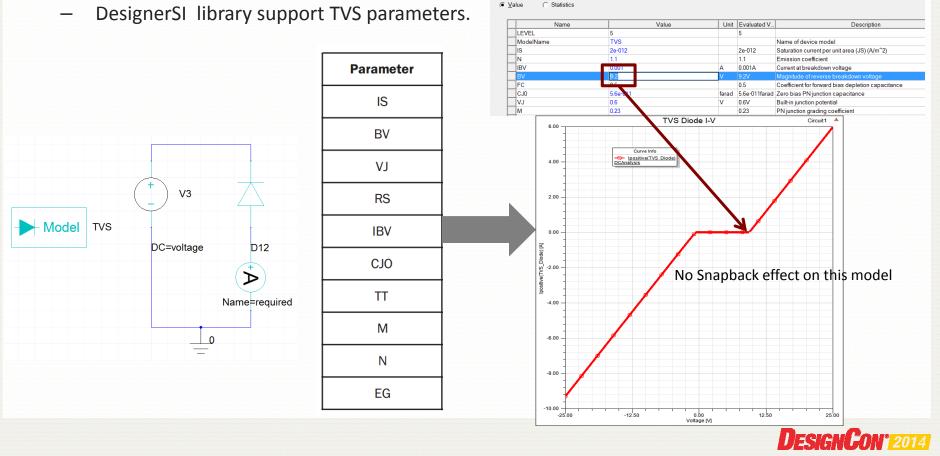

#### **TVS Diode Modeling** •

- TVS(Transient Voltage Suppressors) diode modeling parameters

- DesignerSI library support TVS parameters.

Parameter Values General Symbol Property Displays C Statistics

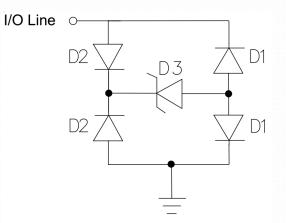

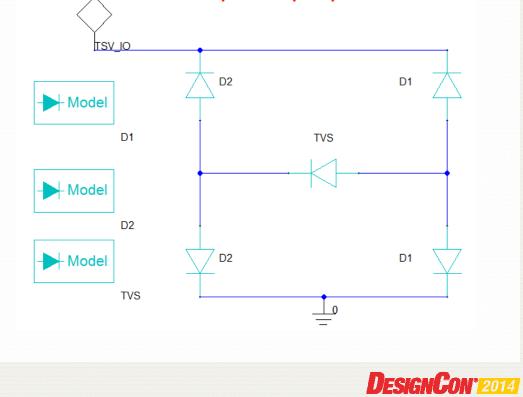

#### TVS Diode Modeling Example

Panasonic Rclamp0821p Spice Model

#### RClamp0821P Spice Model

| Table 1 - RClamp0821P Spice Parameters |       |           |           |          |

|----------------------------------------|-------|-----------|-----------|----------|

| Parameter                              | Unit  | D1 (LCRD) | D2 (LCRD) | D3 (TVS) |

| IS                                     | Amp   | 1.0E-20   | 1.0E-20   | 2.0E-12  |

| BV                                     | Volt  | 100       | 100       | 13.7     |

| ۲۸                                     | Volt  | 0.7       | 0.7       | 0.6      |

| RS                                     | Ohm   | 0.458     | 0.89      | 0.8      |

| IBV                                    | Amp   | 1E-3      | 1E-3      | 1E-3     |

| CJO                                    | Farad | 0.4E-12   | 0.4E-12   | 56E-12   |

| TT                                     | sec   | 2.541E-9  | 2.541E-9  | 2.541E-9 |

| М                                      | -     | 0.01      | 0.01      | 0.23     |

| Ν                                      | -     | 1.1       | 1.1       | 1.1      |

| EG                                     | eV    | 1.11      | 1.11      | 1.11     |

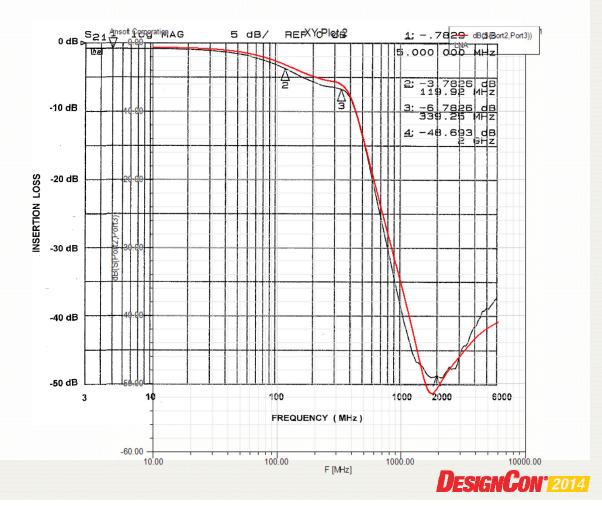

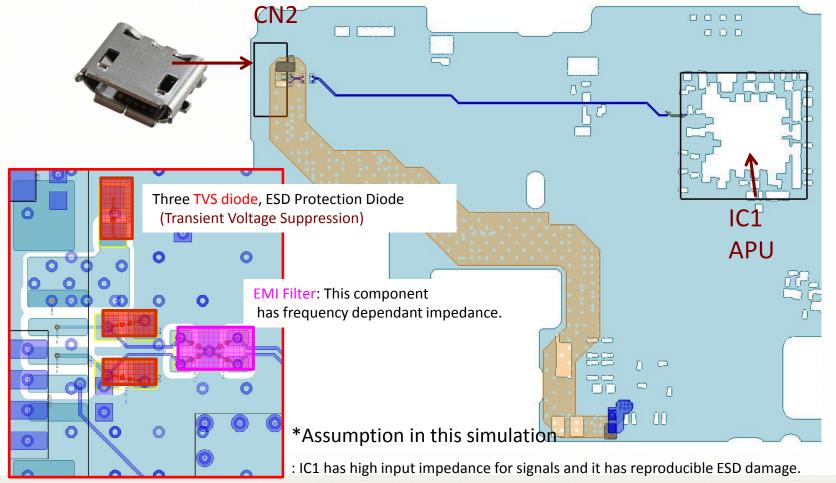

- ESD Filter Modeling

- CMD ESD Filter : Full (Triple) LC block with substrate & diode effects

• ESD Filter Modeling

1101

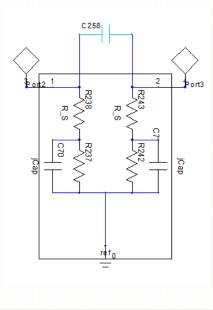

- Simulation vs. ESD Filter Measurement

Common mode EMI/Noise Filter Modeling

- EMI Filter in this simulation will have frequency - dependant equivalent circuit.

## **System-level ESD design**

#### • System-level ESD design

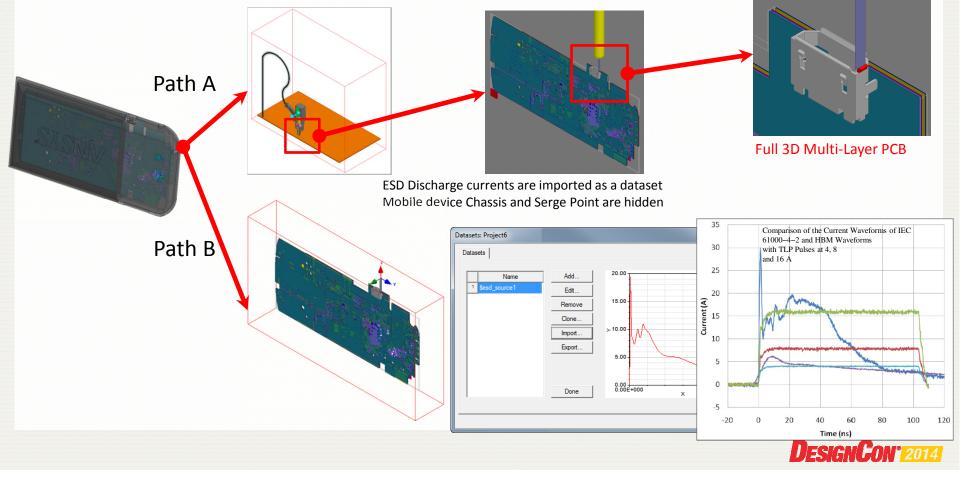

- Design Path A: with ESD Gun Model

- Design Path B: import ESD Source File from ESD Gun Model

#### **Micro USB Connector Device on Mobile PCB**

#### • Micro USB Connector Device on Mobile PCB

- ESD injection on Micro USB Connector

Mobile System-level ESD propagation modeling

VBAT, VCC1.2v, VCC1.8v, VCC2.9v, VCC3.3v, VAP's & Memory Power, VUSB And Ground

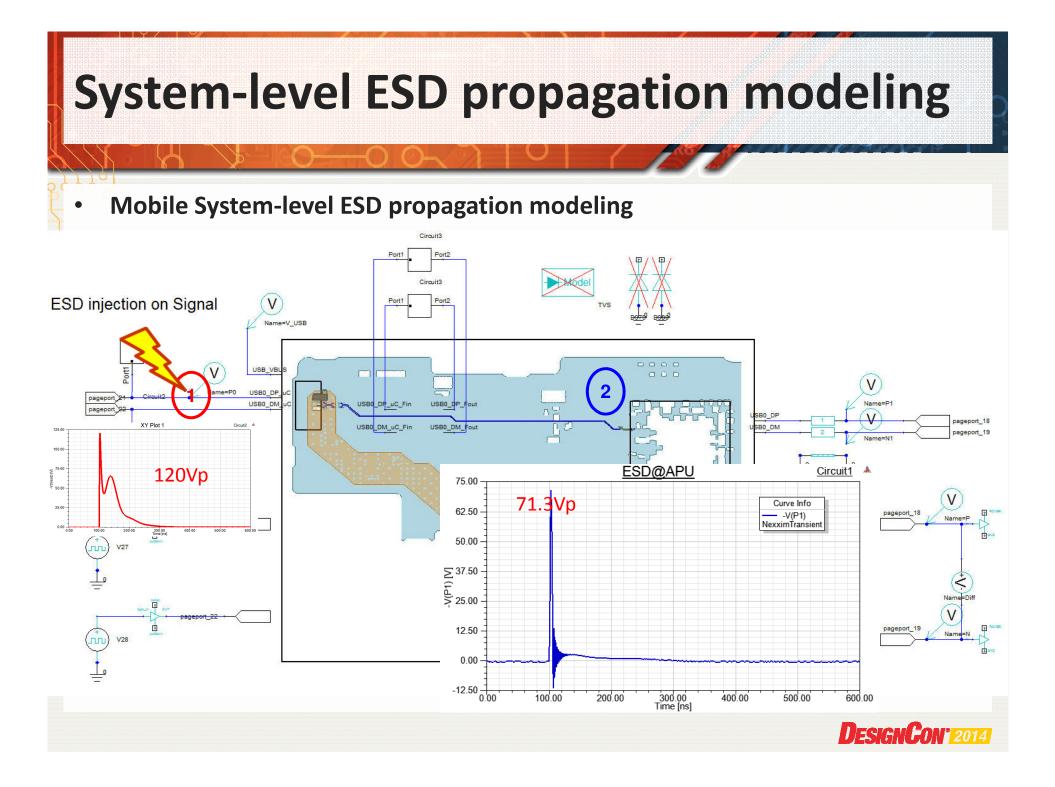

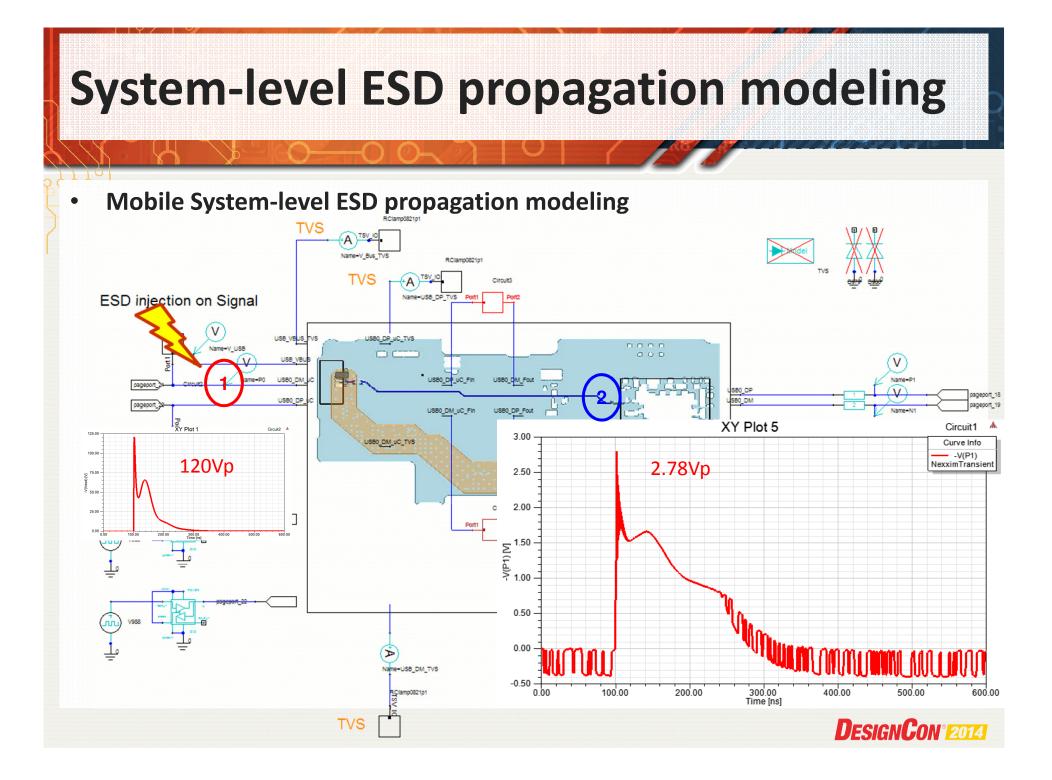

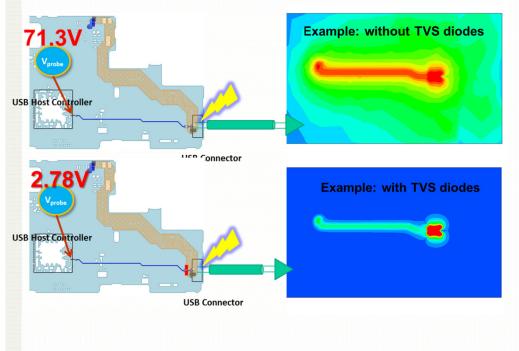

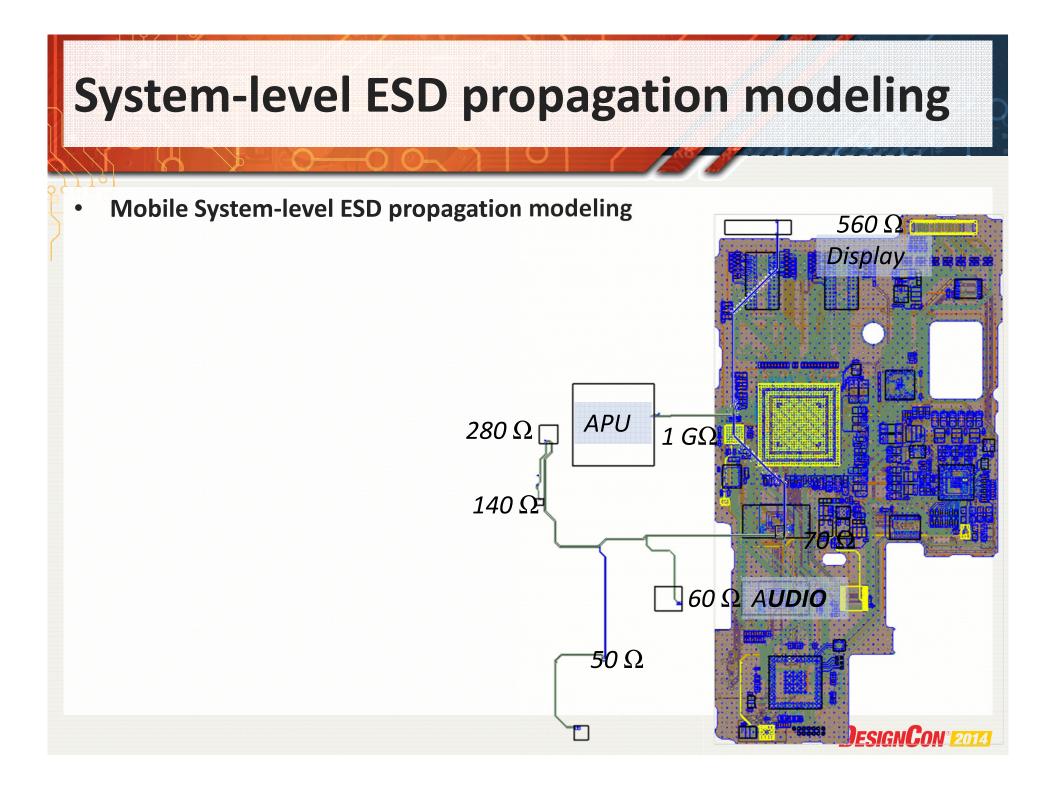

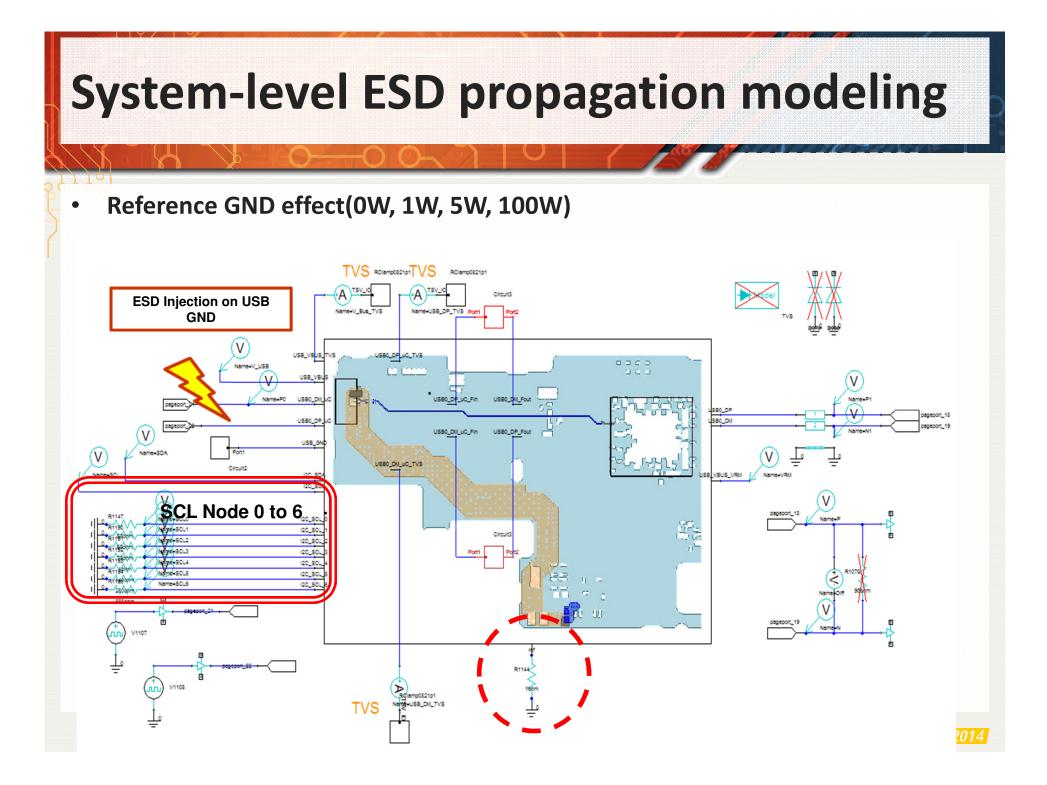

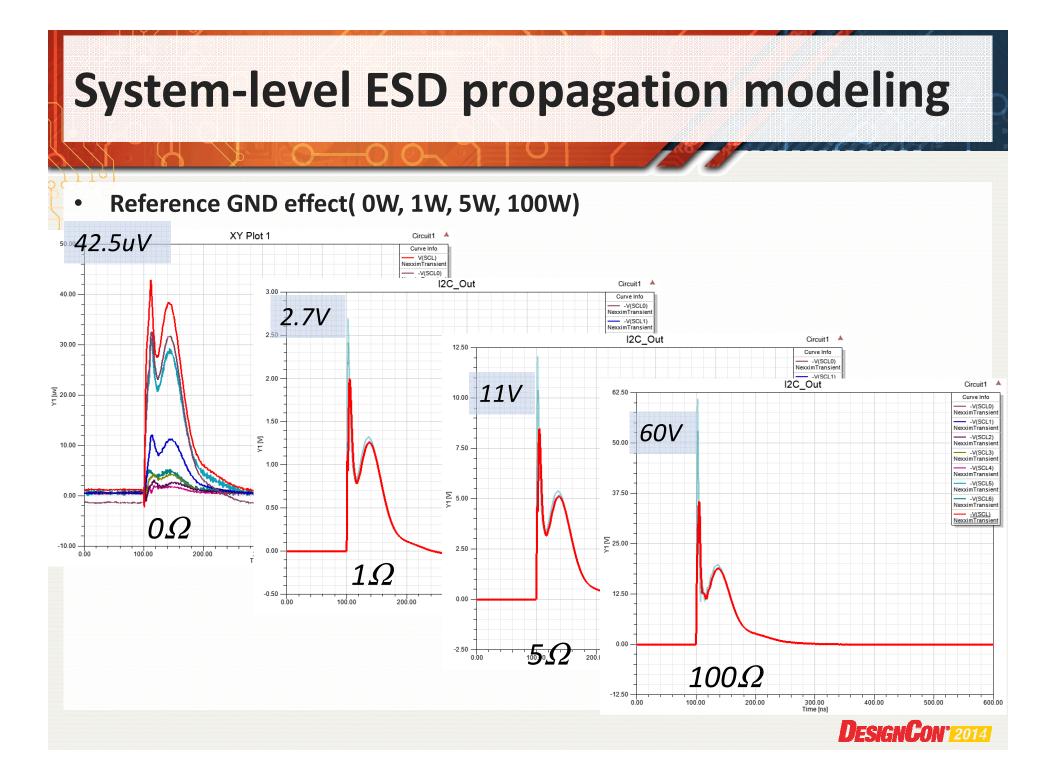

# **System-level ESD propagation modeling**Mobile System-level ESD propagation modeling

#### Mobile System-level ESD propagation modeling

- ESD effect on Signal

- Soft Error

#### - Any error that can be cured by resetting the system (Logical errors: bit error, false reset)

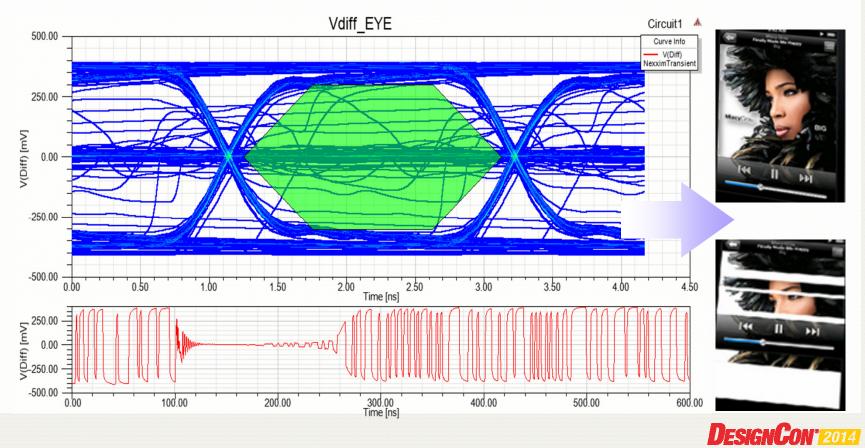

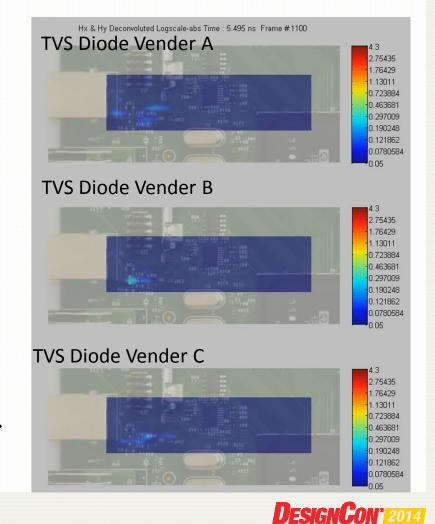

• TVS Diode Effect on High-speed USB Signal

NF scan Simulation Results

NF Scan Measured Example  $\rightarrow$

#### Mobile System-level ESD propagation modeling

Outline a comprehensive Chip-Package-System ESD simulation methodology that particularly addresses the interface modeling between the ESD gun and system, and the interface modeling between the system and IC chip(s) are very important.

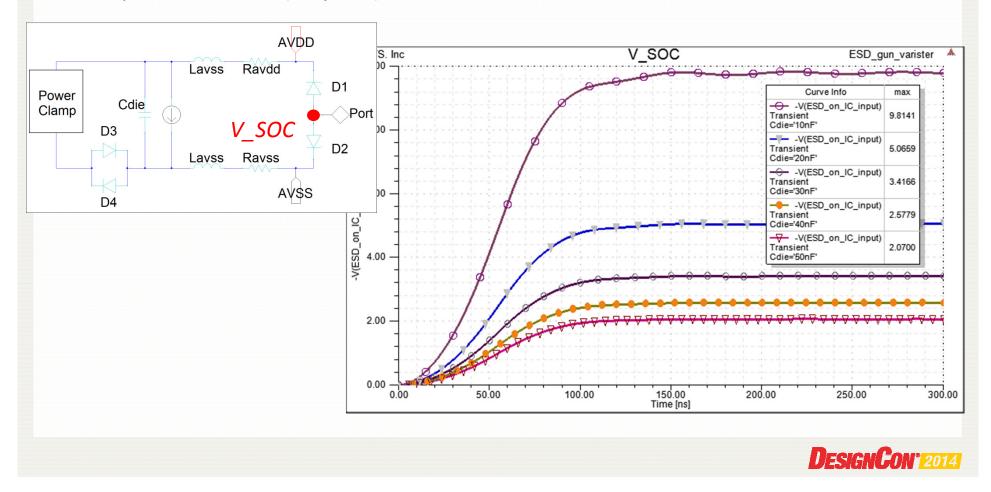

#### Chip Pin V(t) Response w/ Different Cdie

Chip pin V(t) response with different chip Cdie to provide guidance on the effectiveness of ESD protection on PCB (or system)

## Conclusion

- Comprehensive study for ESD events by using "Chip-Package-System ESD Analysis "

- "Frequency dependent component such as Common Mode Filter & TVS Diode with

I-V characteristics" can be modeled and used as a part of system-level ESD simulation.

- Chip pin V(t) and I(t) curve are identified based on chip Cdie, Rdie value in CECM Model.

- □ 3D EM solver provides the robustness in analyzing transition of spike current with visualization.

- ESD zap gun measurement result correlates well with simulated zap current waveform