線上影音

Home > ANSYS SIwave教學> Differential Pair Quick-Eye Analysis

本文最早始於2009,而後於2011、2013、2023陸續更新內容。示範以SIwave 2023R2匯入PCB、檢視與設定堆疊/材質、選定nets裁切與設埠(port)、檢查圖檔與設定模擬條件,模擬後匯出S-parameter,在Designer circuit 2023R2內使用Quick-Eye Analysis,完成整個USB2.0 (480Mbps)模擬流程。

請先學習完兩份SIwave內附的官方快速入門手冊,再接著本文程序操作學習

本文step1~3的PCB圖層處理與匯入方式,僅適用於"古董級"的PADS版本,目前大部分的讀者可以直接跳過前三步驟。較新版的PCB佈局軟體設計匯入方式,請參考 12.6

-

眼圖分析討論

-

問題與討論

12.2 Designer link SIwave有幾種方法? 彼此間有何差異?

12.3 本文範例的Designer附檔是.adsnz,這種檔案該如何打開?

12.4 USB2.0傳輸速率是480Mbps,其相當於訊號頻率多少? 480MHz嗎?

12.5 Quick-Eye analysis與Transient analysis的技術差異在哪裡,為何可以快很多?

12.6 SIwave匯入Mentor PADS、Cadence SPB (Allegro)、Protel (Altium Designer)設計檔的流程? (重要)

12.7 即使按照建議流程import layout,為何有些例子還是會出現掉layer/掉pad/pattern變形...等問題? (重要)

12.8 某些.mcm/.brd,用Sigrity與R17.x SIwave-Alink匯入ok,但用R18.x SIwave-Alink匯入卻看不到via? (重要)

![]()

- SIwave匯入.asc與儲存.anf檔案

- [Compute exact DC point]表示以SIwave-DC解DC值,再將Compute SYZ解出的AC值與此DC值結合成準確的寬頻結果。

-

強烈建議一律以上圖的三段式掃頻設定法:DC取一點,1Hz~100MHz "by Decade"取20~30點,剩下取"Linear Step"。這樣的設定方法可以加強低頻取樣,避免後面抽出來的S-parameter模擬遇到不收斂的問題。

-

[Q3D(auto-detect region)],其代表的是SIwave會呼叫Q3D(3D quasi-static solver)來處理部分小的slot或地不連續的區域,以提高SIwave 2.5D solve在高頻(10G~)的準度。這功能限制較多,只處理trace下方的小洞,且有1/10波長的頻寬限制。

-

[HFSS(user-defined regions)],其代表的是SIwave可以呼叫HFSS(3D full-wave solver)來處理2.5D hybrid sover不擅長的地迴路不連續的區域,比方BGA或連接器下方,沒有任何限制,只是求解區域必須使用者指定。

如果要提取SPICE model,記得勾選[ Set FWS generation parameter],means [Full-wave SPICE] model。只要這項勾選,Start frequency會自動/強制設成0 Hz,因為SPICE model需要全頻帶(含DC)的資訊。

- 輸出模擬結果(S-parameter)

當SIwave求解完成後,如下選擇[Export Touchstone file]即可輸出S參數模型。

輸出模型的最後一個步驟,如下右圖可以選擇要不要對埠端阻抗Renormalize,如果原先同時有設signal port Zo=50與P/G port Zo=0.1(不同埠端阻抗值),那就選[Do not Renormalize Solution]。

Designer不是只能靠匯入S參數模型與SIwave求解結果連結。

這步驟就算沒做(直接跳過)也沒關係,後面step 12.2也可以透過"Dynamic Link"來做Designer link SIwave。

這步驟就算沒做(直接跳過)也沒關係,後面step 12.2也可以透過"Dynamic Link"來做Designer link SIwave。 - 以Designer circuit繪製眼圖

-

眼圖分析討論

-

問題與討論

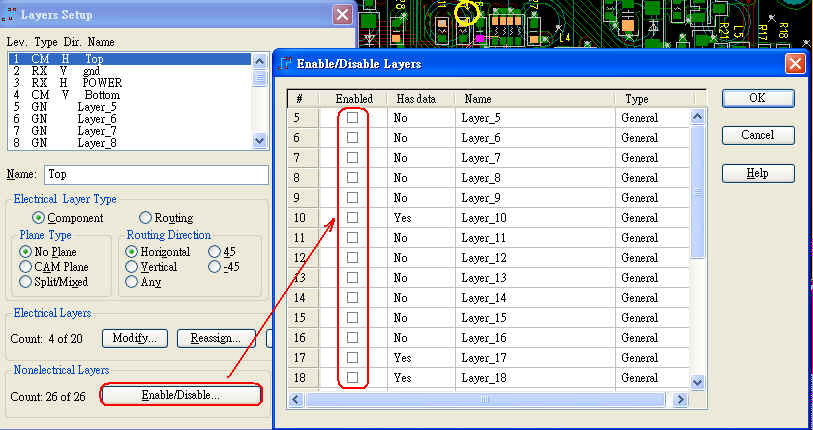

1.1 在PADS內Disable沒有用的層面:[Setup] \ [Layer Definition]

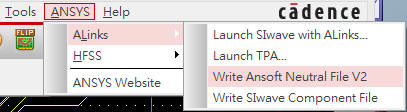

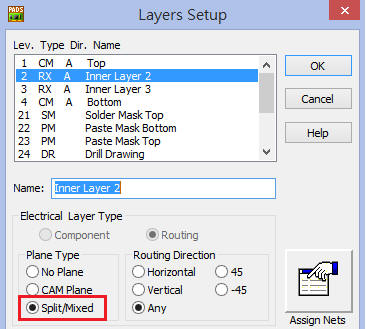

![]() 還必須檢查Plane Type的各層屬性是否正確:沒鋪銅的訊號層指定"No Plane",有鋪銅的power/ground plane則要設定成"Split/Mixed"

還必須檢查Plane Type的各層屬性是否正確:沒鋪銅的訊號層指定"No Plane",有鋪銅的power/ground plane則要設定成"Split/Mixed"

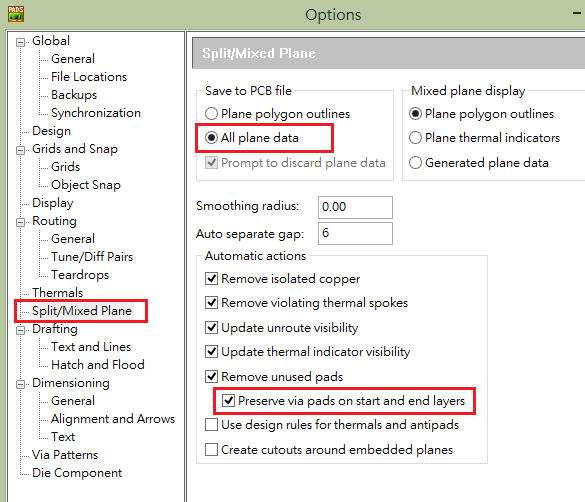

1.2 Split/Mixed Plane設定:[Tools] \ [Options] \ [Split/Mixed Plane]

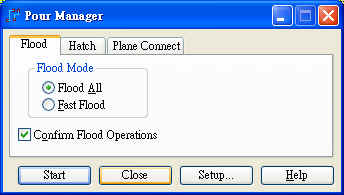

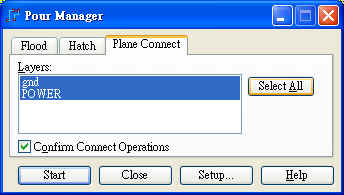

1.3 訊號層鋪銅:[Tools] \ [Pour Manager] \ [Flood] 標籤 --> Flood All --> 按Start

1.4 Power/Ground層鋪銅:[Tools] \ [Pour Manager] \ [Plane Connect] 標籤 --> Select All -->按Start

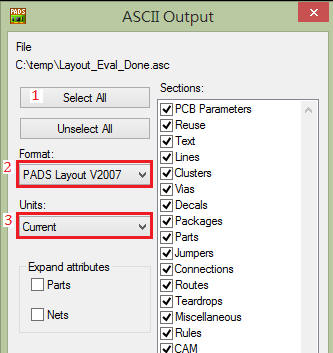

Export .asc:[File] \ [Export]

Select all nets匯出

對於PADS 2007以前的舊版.pcb,建議export .asc (ASCII import flow)

對於PADS 9.4以後的新版.pcb,建議export ODB++給SIwave/Alink import

[Import] \ [Mentor PADS Design]

SIwave指定匯入.asc後,會自動跳一個另存.anf的視窗,只要輸入檔名與路徑,就會自動轉存一個.anf檔。

![]() 工作路徑,不可有中文,否則SIwave與Design crcuit會抓不到。另外,工作路徑+檔案名稱的總長避免超過128位元

工作路徑,不可有中文,否則SIwave與Design crcuit會抓不到。另外,工作路徑+檔案名稱的總長避免超過128位元

4.1 匯入siwave_board.anf 與元件檔siwave_board.cmp

4.2 檢視/修改Layer Stackup

4.3 新增材料:導體設導電率,介質設Dk、Df

介質是一種會隨頻率變化的材料特性,新版的SIwave對於介質材料會自動套用D-S (Djordjevic-Sarkar) model,使用者無須再像過去選擇設定使用D-S或Debye Model。(避免誤用到Debye Model)

4.4 從[Advanced]標籤下,[Trace Cross Section]可設定走線的橫切面形狀

5.1 選擇要模擬的nets (本官方範例.anf中,並沒 真有差動對設計,此處僅以兩條相鄰走線示範操作)

5.2 裁切出局部設計

依"Options For Clipping Design"對話框的說明操作,可以選擇方框分割或是多邊形進行分割。區域選定後按"Clip"

軟體就會自動把其他部分刪去,接著要做整理的動作,清除切割後所衍伸的不完整parts。

![]() 這步驟很重要,除了可以加速SIwave執行[Validation Check]與[Compute S-,Y-,Z-parameters],還可以縮短Designer

circuit吃進.snp file後的模擬分析時間。

這步驟很重要,除了可以加速SIwave執行[Validation Check]與[Compute S-,Y-,Z-parameters],還可以縮短Designer

circuit吃進.snp file後的模擬分析時間。

[Simulation] Tab \ [Validation Check]:可以自動清理因裁切所產生的破碎結構/net (Disjoint Nets)

6.1 project內有bond wire layer的結構,validation check中與bond wire相關的兩個檢查項目才會enable

6.2 在"Nets to be checked"內有一段描述,其主要意思是:SIwave默認只對the nets which are selected, or the nets which are connected to the selected nets by components做檢查,如果你有默認條件以外的nets需要模擬時被考慮進來,則需要在8.1的設定畫面內另外設置。

6.3 [Strict Disjoint Net Checking]默認沒有核選,其意指要不要對於已經定義成"Power / Ground"的net做"Disjoint Net Checking"。SIwave默認是不需要做這項檢查的,因為破碎的P/G net並不影響SIwave solver分析求解。

6.4 如果Validation Check的結果有錯誤,有些軟體可以自動修正(Auto. fixed),有些則需要使用者自行修正layout處理。

-- "Self-intersecting Polygons" Error,指的是PCB Tool自動鋪銅後,有些地方會有鋪銅不完整的情況。雙擊(double-click) Error messages所顯示的座標,即會跳到layout錯誤處,使用"Draw Rectangle" 在merge mode把縫隙補齊就可以。

請選擇"Rectangle"補鋪銅,不要選trace補,因為SIwave視兩者的屬性是不同的,前者才是plane

-- "Disjoint Nets" Error,選Auto. fixed.

-- "DC-Short" Errors,可能是有些Net沒拉好,修正或刪除即可。

-- "Overlapping vias" Error,可能是有些via重疊,刪除即可。

-- "Misalignments" warning,選Auto. fixed.

![]() Validation Check的Error message,其所顯示錯誤位置處的座標,是採用使用者在做Validation Check當下的系統單位設定,所以如果unit有變更過,要double-click讓軟體能正確指到layout錯誤處,必須把單位設定改回去或重做Validation Check才可以。

Validation Check的Error message,其所顯示錯誤位置處的座標,是採用使用者在做Validation Check當下的系統單位設定,所以如果unit有變更過,要double-click讓軟體能正確指到layout錯誤處,必須把單位設定改回去或重做Validation Check才可以。

先指定GND net為深綠色

[Home] Tab \ [Circuit Elements] \ [Add Port] ![]()

Port擺放的過程中,會出現一個對話框,設定port的 兩端分別放在哪一層。positive terminal放在訊號層,negative terminal放在reference ground layer (GND net),小心不要設錯。

![]() 下圖右所示的negative terminal擺放位置,因為正好layer1, 2都是GND net,所以放哪一層都可以

下圖右所示的negative terminal擺放位置,因為正好layer1, 2都是GND net,所以放哪一層都可以

然後輸入port name。

記得在trace的IC端與Connector端都要設port,且用不同名稱以利區分(e.g. xxx_U38, xxx_U54)。

如果設完port後若看不到port,請把各層layer的檢視Circuit Elements核選就可以看到。

以同樣的步驟,在differential pair兩端,分別在net UN1622...PIN20/PIN30的U38、U54端共設四個port。

8.1 SIwave options 可以全部用默認設定

如有買HPC要設定超過4核心求解者,上圖請切到[Multiprocess] Tab下設定

8.2 有兩種方式以選定模擬要看的Nets。下圖是使用默認讓軟體自動選有下port的net做模擬

有選定模擬的nets,比起沒被指定,只是有耦合關係的,前者會被考慮的較仔細(by MoM)

8.3 [Simulation] Tab \ [Compute S-,Y-,Z-parameters]

New a circuit design in AEDT:[Project] \ [Insert Circuit Design]

會跳出一個對話框,可以選擇一些基本的PCB Stack,或是如下所示,直接選None。

10.1 加入元件S-Parameter model (由SIwave所萃取的PCB參數.s4p) ![]()

Add Nport Model後,它除了會出現在主電路編輯視窗,在Project Manager視窗的Definitions \ Compoments路徑下,也可以看到匯入的SNP。

10.2 Add Eye Source and Probe ![]()

從Project Manager視窗Components頁內的Nexxim Circuit Elements路徑下,選擇Independent Sources下的"EYESOURCE_DIFF"。

EYESOURCE是Quick-Eye Analysis專用的pattern source,且做QuickEye Analysis一定要用EYESOURCE與EYEPROBE。

設定EYESOURCE_DIFF:Double-click會跳出properties視窗。因為USB Differential Impedance=90歐姆,所以在"Parameter Values"頁內的"resistance"設90。USB 2.0定義傳輸速率480Mbps,相當於每個bit time 2.08ns,raise time=500ps,振幅正負400mV。

雙擊電路元件會跳出Properties視窗, 選[Component] Tab最下面會有一[Info]列,按右邊按鈕會出現Help說明 。

從Project Manager視窗Component頁內的Nexxim Circuit Elements,選擇Probes目錄下的"EYEPROBE_DIFF",並在D+\D-端各加一個45W終端電阻負載。

輸出端放負載電阻R78,R79=45W,是為了特性阻抗匹配,避免訊號反射,不過也會改變訊號振福。另一種做法是把high-impedance input IBIS model放在接收端,如step 11.1。

10.3 Set Quick Eye Analysis ![]()

10.4 Run Simulation ![]()

有兩個方式可以開始執行模擬分析

10.5 Plot Eye Report ![]()

以滑鼠右鍵點Project Manage視窗內的Project頁內的Result icon,選擇 Create Eye Diagram Report \ Rectangular Plot

跳出Report視窗,什麼都不用設定,直接按"New Report"就可以看到眼圖結果

Plotting Range中的"Time Stop"最好與Analysis setting中的"Unit Interval"對應,可設Time Stop大約是UnitInterval"的數百到數千倍。如果在EYESOURCE的[BitPattern]有輸入編輯好的bit pattern file,那"Time Stop"會自動由bit pattern file內容長度決定,一般常用PRBS11~PRBS13。

得到輸出的模擬眼圖如下,振幅只有正負200mV,Why? 參考11.1

本文僅以ANSYS Designer內建的EyeSource,示範簡單的QuickEye Analysis,概略評估USB differential pair SI。如果要嚴謹的模擬,需用Transient Analysis配合USB 2.0 IBIS model。這部分的做法,我們留在延伸閱讀02,再進一步的說明。

Transient Analysis只需SIwave Premium license,Quick Eye Analysis則需完整的Enterprise license。

對於QuickEye Analysis模擬的程序,想進一步學習者,可以參考以下連結

![]() How to Calculate Eye Pattern of High Speed Signal with QuickEye

How to Calculate Eye Pattern of High Speed Signal with QuickEye

11.1 電壓源與電流源的差異 ![]()

大部分高速傳輸介面,如USB2.0/1394/HDMI是current drive的,其輸出振幅是由驅動電流與接收端阻抗所決定(V=IR)。

Designer circuit內所提供的EYESOURCE是電壓驅動(電壓源),所以需要輸入voltage level(400mV);但step10.5所得到的振幅卻是較小的(200mV),這是因為終端附載45W會與Diff. Source內的90W形成分壓的效果。若同時驅動兩組(含)以上的differential pair時,會發現訊號振幅變更小。

如果傳輸線的另一端是用input IBIS,如下圖所示,那EYESOURCE_DIFF的電壓振幅設多少,實際模擬出來的振幅就會是多少了。

11.2 模擬I/O驅動力不同的影響 ![]()

如果在Set QuickEyeAnalysis中,設定"Rise Time"從500ps改成100ps,模擬IO driving能力加強的效應如下:ripple振盪較明顯,其波形是reflection吃掉造成的。

11.3 模擬系統Jitter

noise的影響 ![]()

在EYESOURCE_DIFF的property中,設定"Gaussian jitter"為10ps,模擬系統或電源jitter noise所引起的效應

結果如下

若要把不同Nexxim Design的模擬波形貼在同一張圖上,按滑鼠右鍵,使用Copy Data \ Paste即可。貼圖前,原波形檔不可有任何設定改動(如改變顏色)否則會貼不過去

若線條要設定不同顏色,雙擊被貼資料的那個Nexxim Design的的顏色線段),跳出的Properties視窗,第一頁下方會有[Line Color]可供選擇顏色。

屬性視窗內選[Zoom range],就可以看到區分顏色顯示的眼圖

![]() 若想把兩個以上的模擬結果放在同一張plot,可以使用Alter Function,不用開三個Nexxim Design。

若想把兩個以上的模擬結果放在同一張plot,可以使用Alter Function,不用開三個Nexxim Design。

12.1 其他常用的眼圖模擬方法? ![]()

Ans:分析眼圖有四種方法,Verify Eye Analysis,AMI Analysis (statistical ey),Transient Eye與Quick Eye Analysis。

各有不同適用情境,詳情參閱 眼圖分析與IBIS-AMI - 總結

12.2 Designer link SIwave有幾種方法? 彼此間有何差異? ![]()

Ans:除了本文step9 export touchstone file (S-parameter model)的方法,還可以從Designer內直接link SIwave project,而這兩種方法跑出的眼圖會一樣(範例)。後者又稱作"dynamic link",可以支持"push excitation"對於EMC application特別好用。

12.3 本文範例的Designer附檔是.adsnz,這種檔案該如何打開? ![]()

Ans:從2013年起,ANSYS EBU產品R14.5的版本,提供內建整個project打包(壓縮)功能,要打開此類檔案只要從[File] \ [Restore Archive],或是在有安裝AEDT(ANSYS Electronic Desktop)的環境下,雙擊檔案本身即可啟動AEDT開啟。

12.4 USB2.0傳輸速率是480Mbps,其相當於訊號頻率多少? 480MHz嗎? ![]()

Ans:傳輸速率或帶寬(Mbps) = 訊號頻率(MHz)*通道數*編碼方式(NRZI/PAM4)

USB2.0雖然是定義480Mbps (M bit per second) = 60MB/s (M byte per second),但實際傳輸只會達40~30 MB/s。這是因為USB使用NRZI編碼,一長串的傳輸封包中一開始有同步訊號,結尾有錯誤檢核碼,僅中間一段帶實際傳輸資料,且有Error-Correction Code糾錯機制(當發現傳輸資料有誤時,封包會重新發送一次)。

參考USB 2.0 量測眼圖的結果,UI設2.08ns是合宜的。

12.5 Quick Eye analysis與Transient analysis的技術差異在哪裡,為何可以快很多? ![]()

Ans:Quick Eye其實與IBIS-AMI的技術很像,input bit-stream to convolve the step response of channel transient, assuming LTI system. (Linear Time Invariant 線性非時變系統) 參閱 眼圖分析與IBIS-AMI - 介紹

12.6 SIwave匯入Mentor PADS、Cadence SPB (Allegro)、Protel (Altium Designer)設計檔的流程? ![]()

Ans:

For Mentor PADS v2005/2007 -- export .asc 如本文步驟1~3

For Mentor PADS v9.4 or later-- export ODB++ (.tgz)

For Cadence SPB (Allegro) -- method1, export .anf (Ansoft Neutral File) from Cadence SPB directly with ECAD installed (ECAD don't need license). This way only works before 2018.

-- method2, drag and drop .sip\.brd\.mcm to SIwave(Alinks) directly with ECAD and Cadence SPB installed (call extrata, and do not need to launch any Cadence tools). This way only works before 2018.

-- method3, import .sip\.brd\.mcm from AEDT 3DL with Cadence SPB installed (call extrata, and do not need to launch any Cadence tools, but requires Cadence SPB license for SPB17.4 import).

-- method4, export IPC-2581 ver. B by Cadence SPB

For Protel (Altium Designer) -- export .anf or ODB++ directly from Altium Designer 13/14

[File] \ [Save As] , select .anf file type to export .anf

[File] \ [Fabrication Outputs] \ [ODB++ Files]

For Protel (Altium Designer) -- export EDB from Altium Designer 19

12.7 即使按照建議流程import layout,為何有些例子還是會出現掉layer/掉pad/pattern變形...等問題? (重要) ![]()

如果出問題的是Cadence的layout檔案,且你是走method2 flow,請改用改用傳統的method1 flow試試。如果只有前者有問題,那關鍵在extrata.exe,必須更新最新的Cadence version

如果出問題的是Cadence的layout檔案,且method1與method2 flow都遇到整層的layer都看不見了,那請回到Cadence tool內去檢查是否該消失層的layer屬性沒被正確定義,如下圖所示Layer2明明是metal,卻被誤定義為dielectric

[Setup] \ [Cross-section]

如果出問題的是PADS的layout檔案,雖然你已經照本文step1.2~1.4做了,匯入後還是有一整層的舖銅看不到

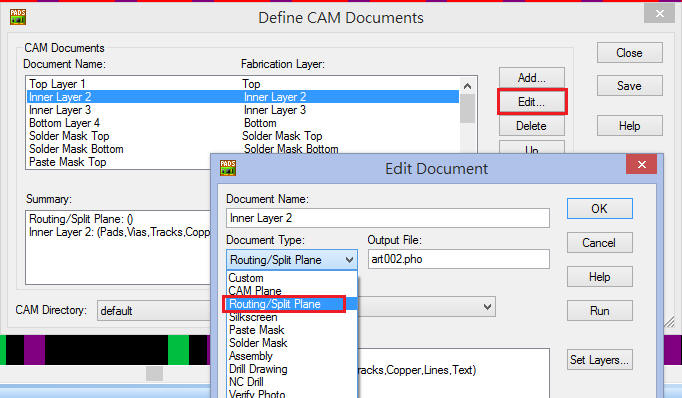

[Setup] \ [Layer Definition]內檢查該層的屬性是否被定義在Split\Mixed

[File] \ [CAM]內檢查內層的屬性

12.8 某些.mcm/.brd,用Sigrity與R17.x SIwave-Alink匯入ok,但用R18.x SIwave-Alink匯入卻看不到via? (重要) ![]()

Ans: 原因出在原始的layout檔案中對於疊構層的設定有誤(沒有定義介質層)。可以從Cadence Layout tool的[Setup] \ [Cross-section]進去檢查

Sigrity與R17.x SIwave-Alink匯入時,存在一些假設(默認)條件,填補這使用者錯誤,而ANSYS R18.x SIwave(Alink) and new version則選擇忠實呈現layout本身的訊息,如果via pad-stackup定義資訊不完整,不以默認值自動填補,避免使用著未察覺問題,模擬條件與實際結構不符,得到錯誤結果而不自知。