線上影音

Home > Icepak教學 > SIwave-Icepak Link and MTTF Analysis by SIwave

本文始於2021,並於2022更新,介紹如何在SIwave操作環境下做SIwave-Icepak電熱雙向耦合模擬[1][2]:一種讓電性工程師沒有任何困難地,可輕易從電跨到熱模擬的流程。

-- 新增8.3, 8.8, 8.9 -- 2022.01.07

-

Check Result

-

Q&A

8.3 如何從SIwave匯出AEDT Icepak 3D模型?

8.4 為何同一導體材質,在不同論文中可能使用不同的Ea參數?

8.5 本文介紹的SIwave-Icepak模擬流程,適合分析打線的熱嗎?

8.6 步驟5.2中,2019R3與2021R2的溫度分別是135.8與147oC,這差異11oC從何而來?

8.7 如何在SIwave內建立參數化的散熱片,並於Icepak模擬時考慮其對元件的散熱效果?

8.8 步驟2中SIwave-Icepak自動匯入的.sitemp熱分佈檔,可在AEDT Icepak中單獨產生嗎?

8.9 在新版SIwave options內設定,與用功能選單[Temperature Profile]匯入.sitemp,有何不同?

8.10 步驟3中,為何就算勾選了[All Bondwires/Vias]還是看不到bondwire/via/ball上的電流密度?

![]()

-

自2016起,SIwave R17操作介面內可以直接呼叫Icepack,做電熱耦合雙向分析(2-way coupling)。 [1][2]

自2021起,只要安裝SIwave,不須再裝Icepak,即可做電熱耦合雙向分析(2-way coupling)。 License required

下圖是2021R1 SIwave環境下的相關分析功能(DC IR/MTTF/Icepak)所在位置,本文將逐一介紹。

必須解過DC IR分析並勾選[Export power dissipation for use in ANSYS Icepak ...],Icepak才可以使用(功能按鈕從灰色轉彩色)

必須解過DC IR分析並勾選[Export power dissipation for use in ANSYS Icepak ...],Icepak才可以使用(功能按鈕從灰色轉彩色)

-

雖然一開始選[Set uniform design temperature to ...],當後續步驟四執行Icepak熱分析時,這裡的設定會自動切到[Import temperature map from Icepak]讓SIwave-Icepak的求解後資料可以互相傳遞,repeat simulation until DC convergence (iteration)。

-

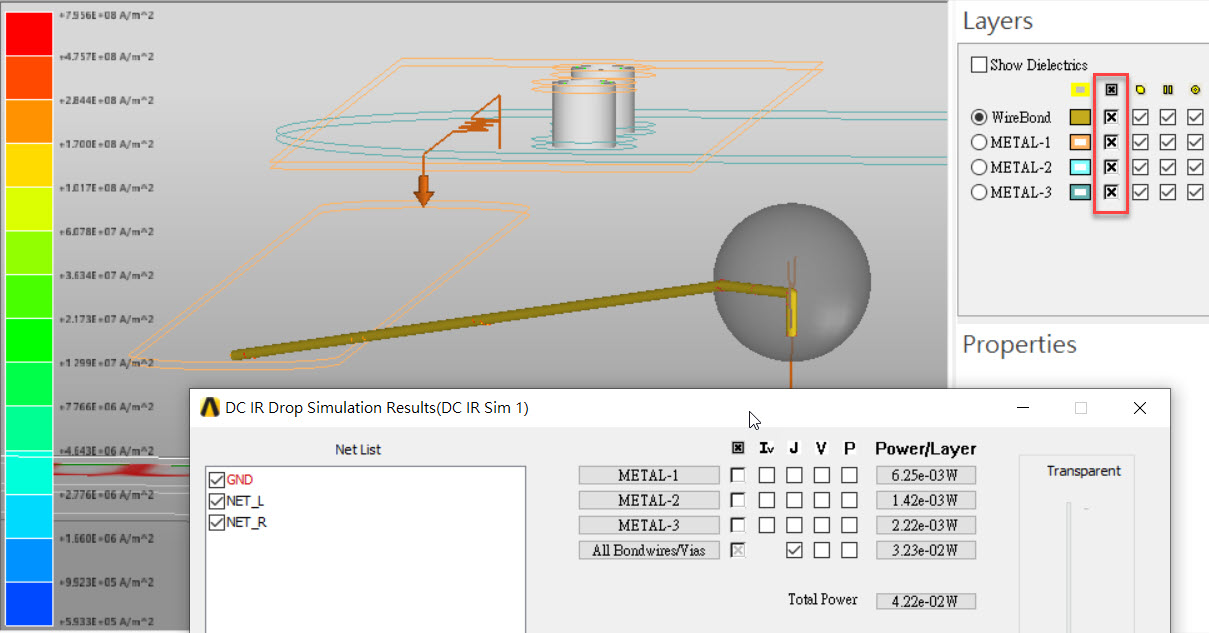

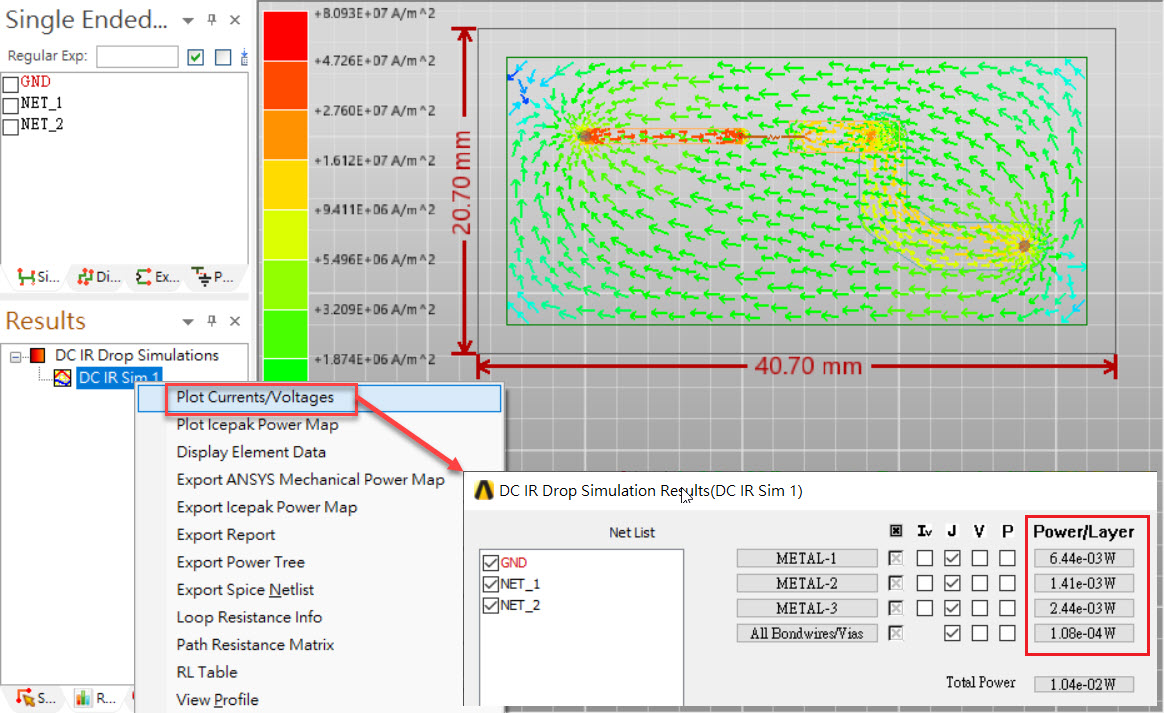

如果要色階顯示單位,必須只指定顯示Iv/J/V/P其中之一。

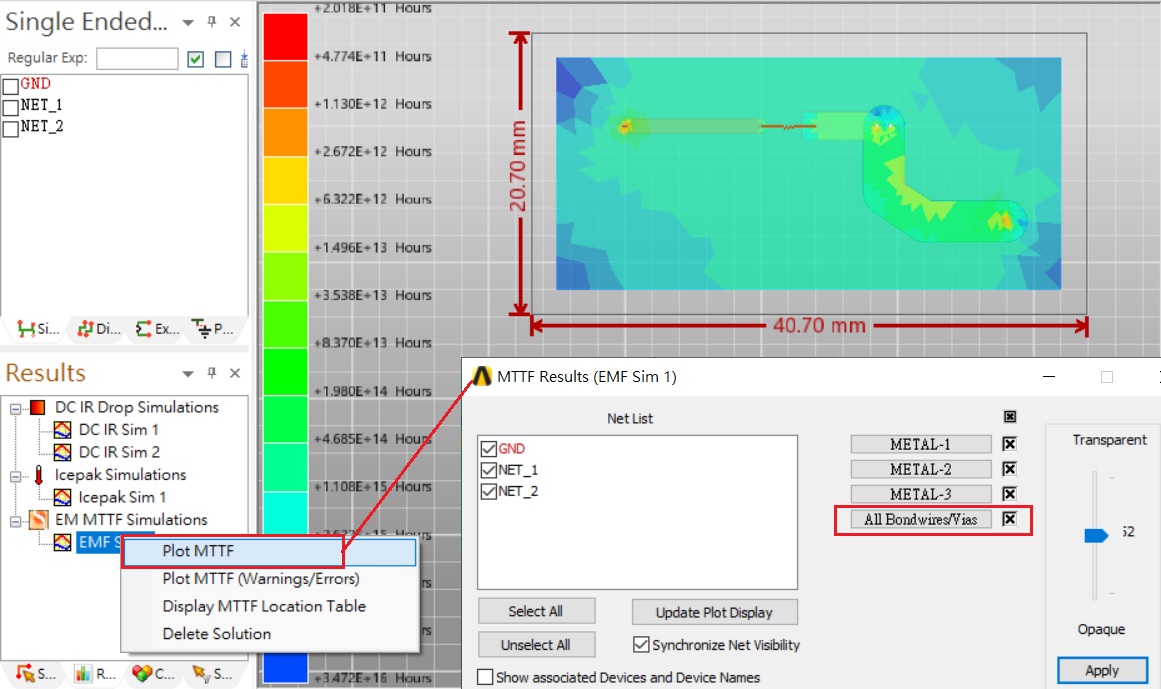

Bondwire與Via也能plot current/voltage,但必須在上圖右下的對話框內勾選顯示。

還有其他許多DC分析的輸出結果,讀者自行試試,我就不多說了:

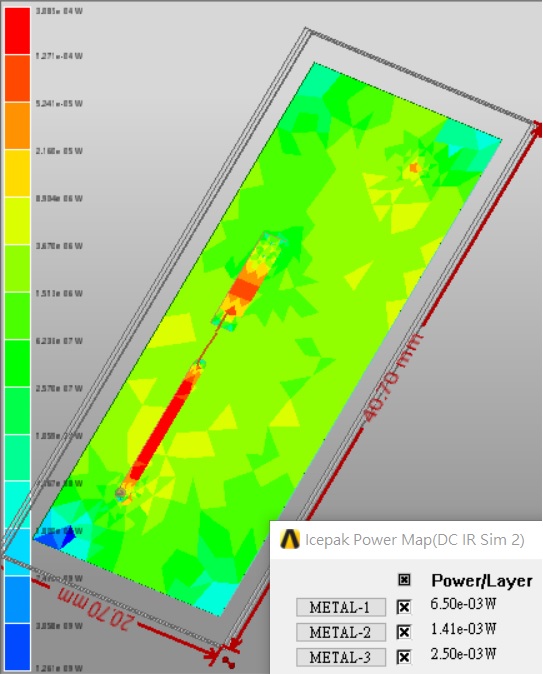

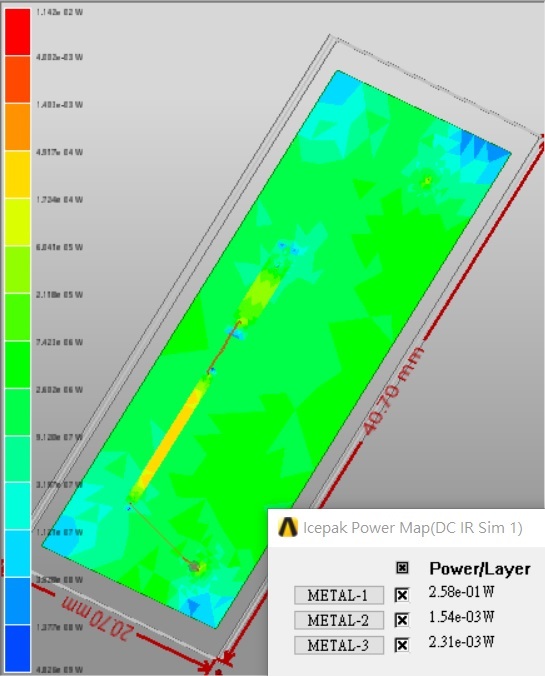

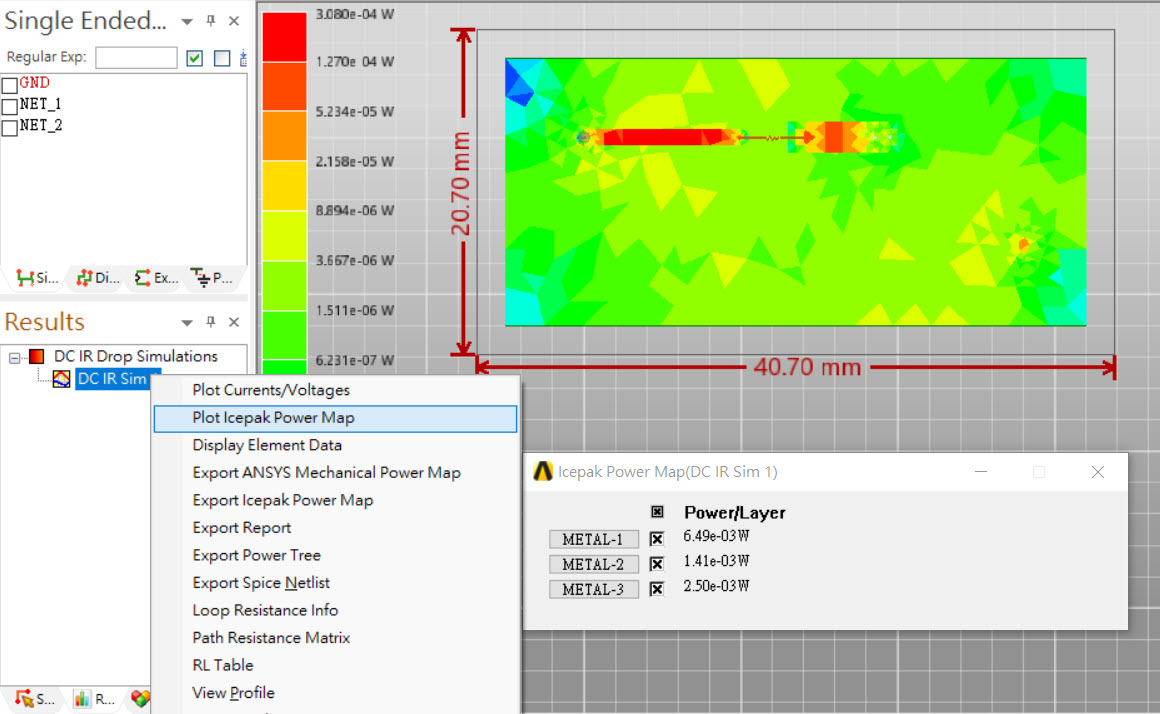

Plot Icepak Power Map ... 通過via的power被分到相鄰的layers (Metal-1, Metal-2)計算

Display Element Data ... 可以看每個bondwire/via的個別阻抗,還有電流是否超過安全耐流質

Export Power Tree ... 以樹狀分支的方式顯示每一條power path的電流與IR drop狀況

Loop Resistance Info.

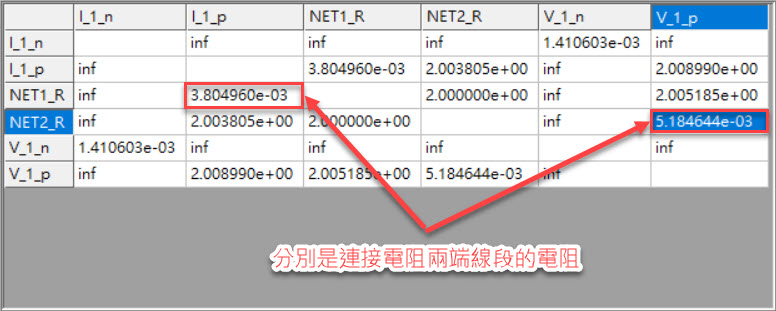

Path Resistance Matrix ... 看這裡的結果就了解為什麼一開始要在電阻兩端加terminal (NET1_R, NET2_R)的原因

-

Thermal Analysis Setup

- Check Result

5.1 Conduction (PCB Only - no components)

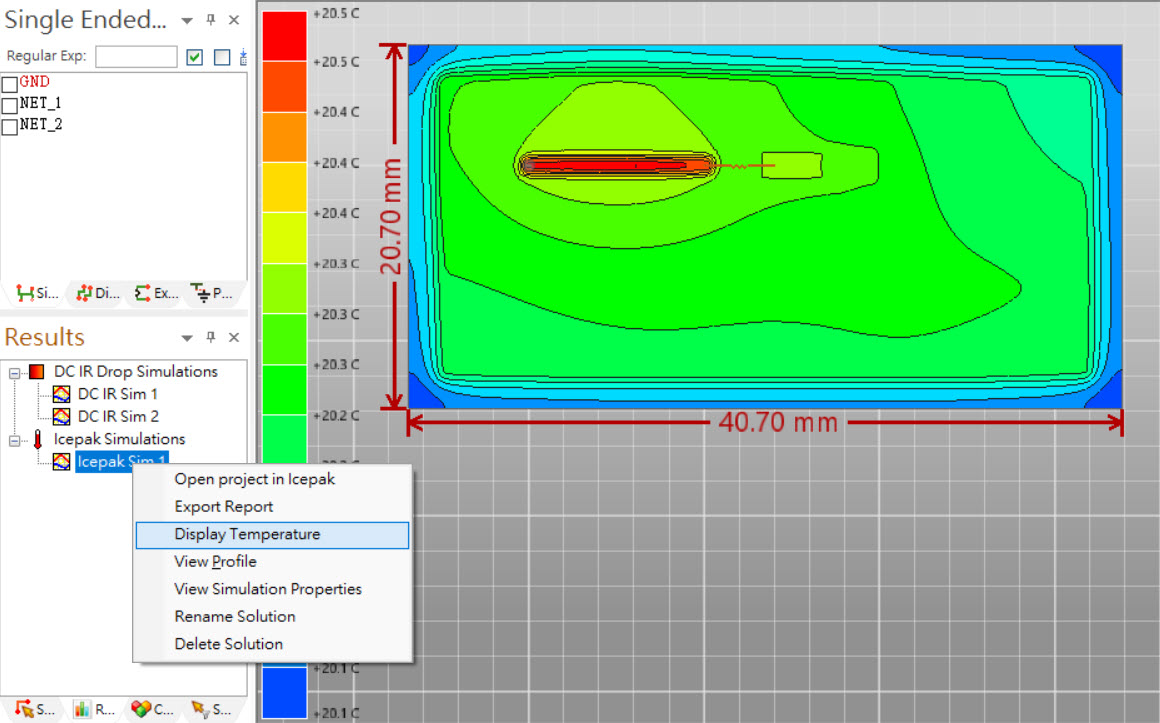

Temperature Plot (2D)

5.2 Convection (Components optional) 模擬時間較長

5.2.1 Icepak Setup

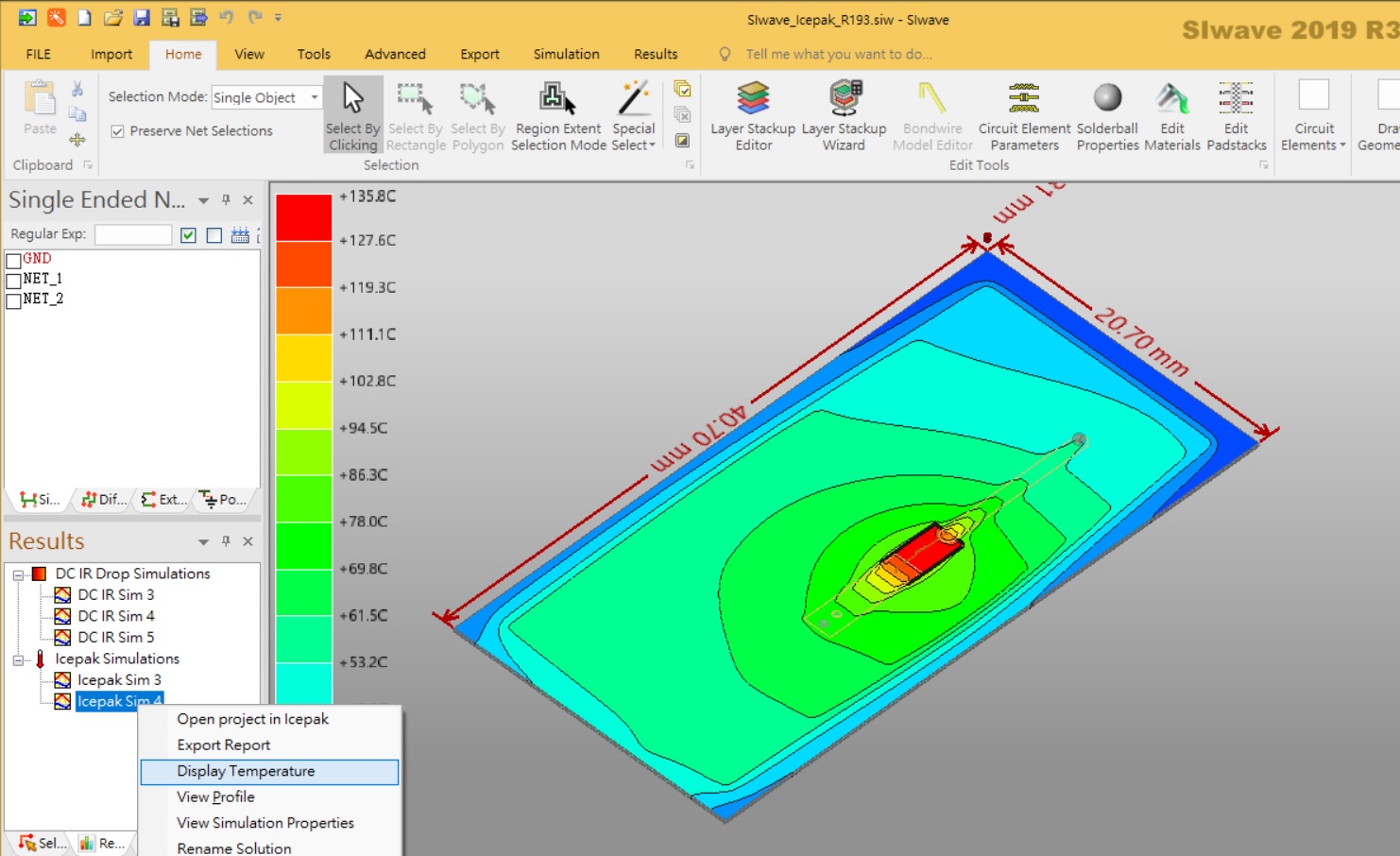

5.2.2 R19.3與2019R3版本的輸出下圖所示:最高135.8度

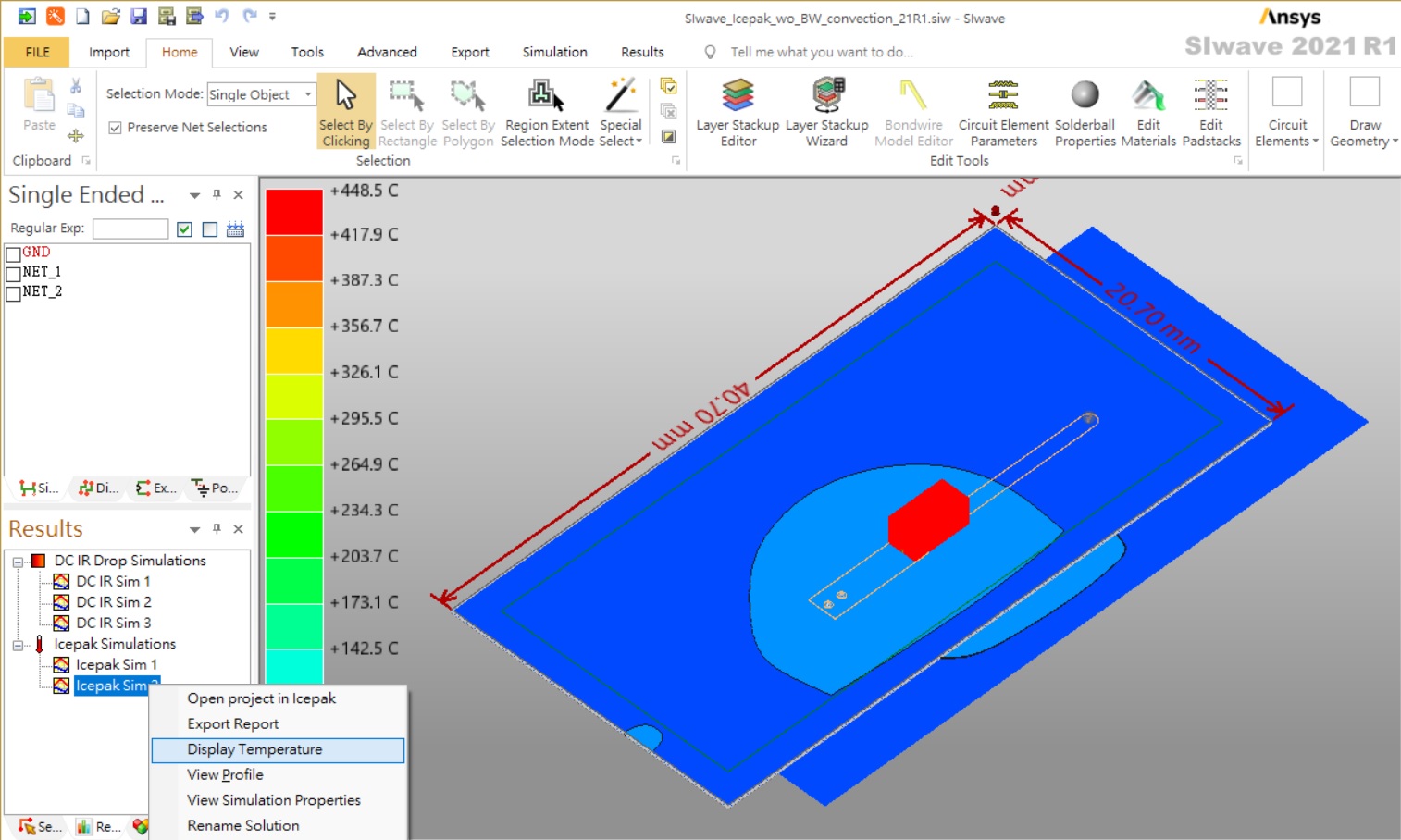

5.2.3 2020R2與2021R1的輸出:最高448度 (這是錯的,有workaround方法,且2021R2已修正)

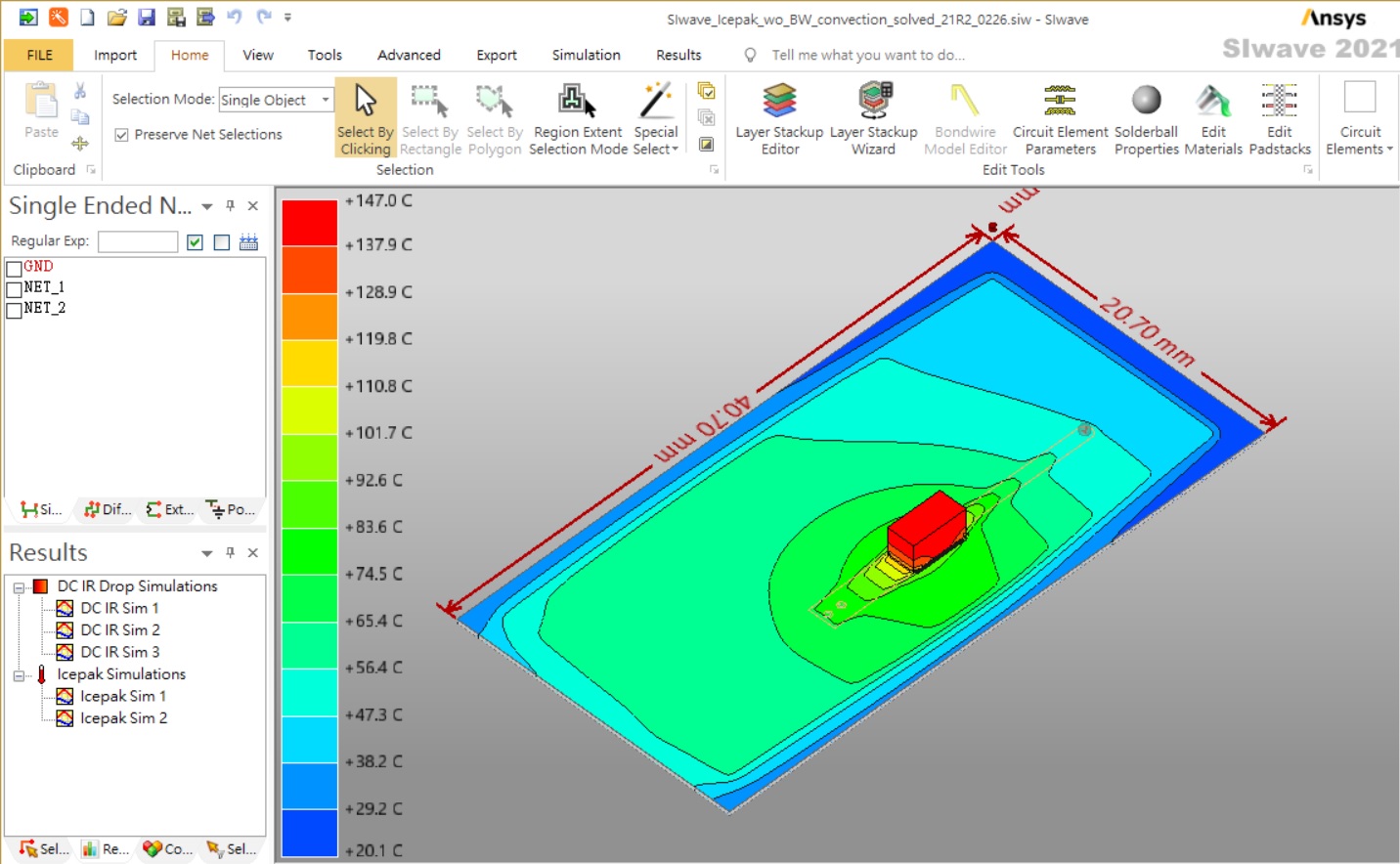

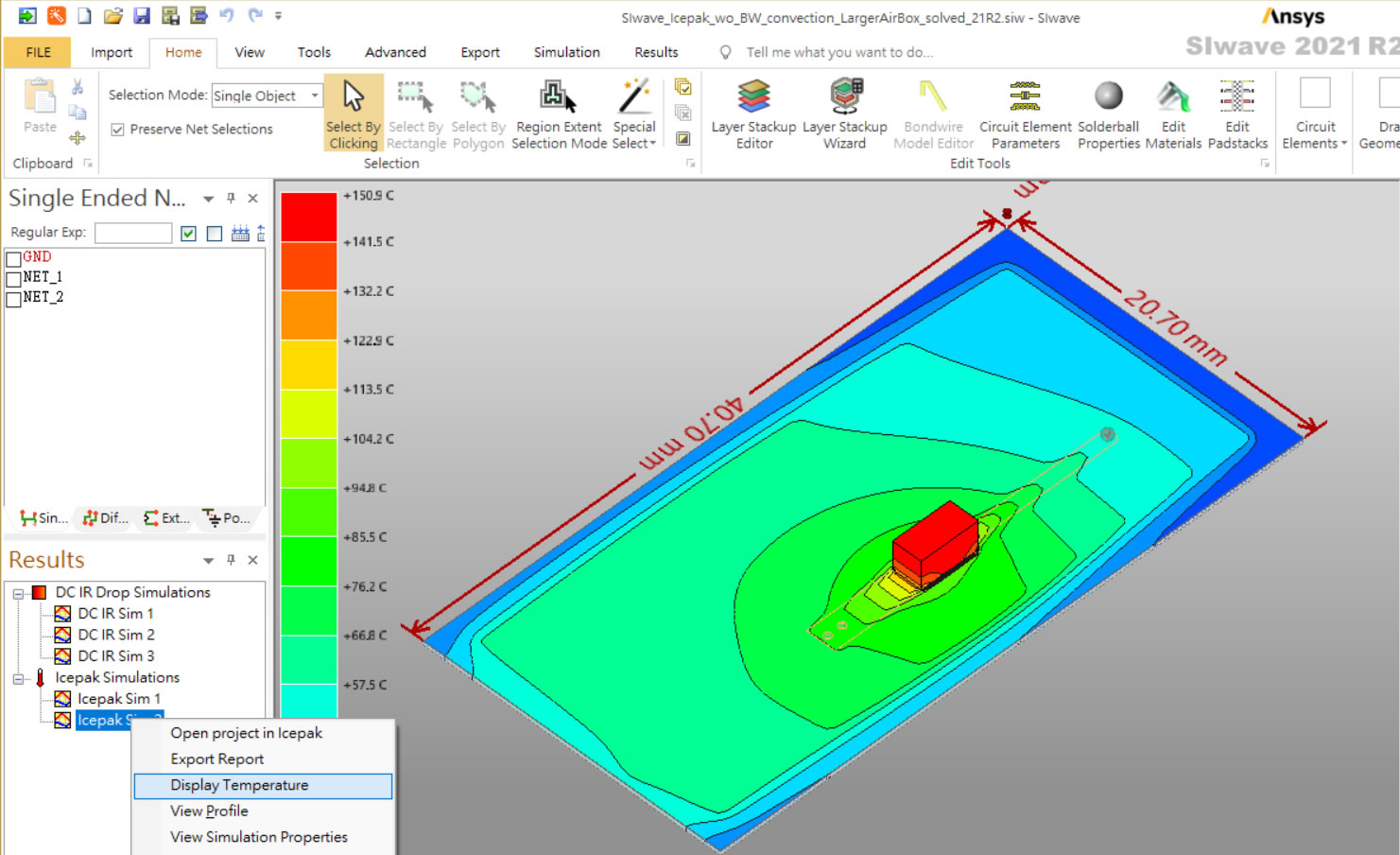

5.2.4 2021R2輸出結果:最高147度 ... why 135.8 vs. 147 difference ? Refer to 8.6

[Convention]求解結果的最高溫度135/147oC明顯大於[Conduction] 20.5oC,這是因為前者才有考慮1A流過串聯電阻R_1(2 ohm)的2W功耗所造成的熱,而這功率損耗遠大於Metal-1/2/3各層的功率損耗(約1000倍)。

- EM MTTF Setup

MTTF(Mean Time to Failure)也就是產品使用壽命預估,又稱電遷移分析(Electromigration Analysis)。

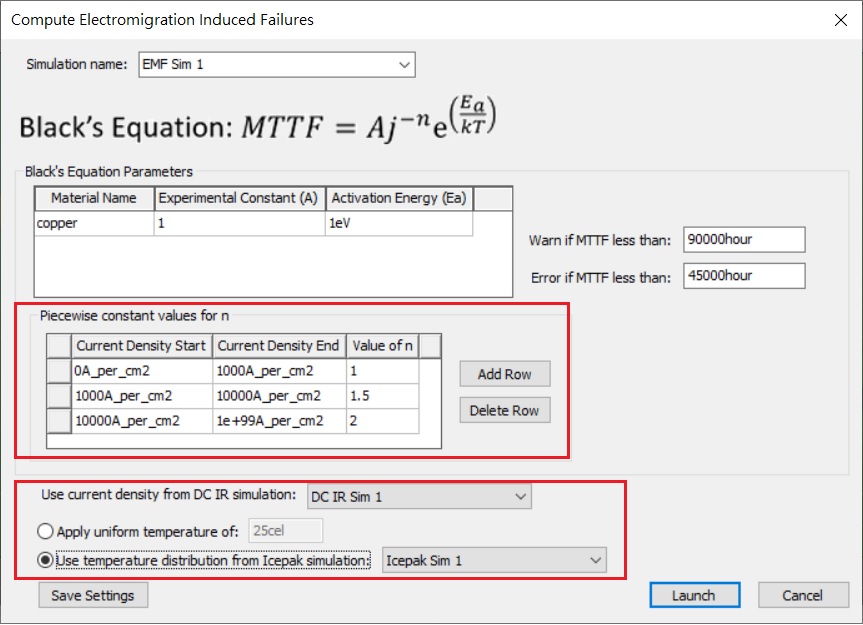

雖然這是SIwave 2019新功能,但其背後所依據的Black's Equation卻歷史悠久,最早源於1969 [3],其後有很多的研究,在此推薦參考[4], [6]。以下是SIwave HELP內的說明:

Black's equation說穿了就是以考慮導體上的"(DC)電流密度"J,與"溫度"T這兩個參數,透過Ea (activation Energy活化能)與n(經驗係數)估算出導體會發生電子遷移(導體損壞、產品掛掉)的預估使用時間(lifetime)。

SIwave-Icepak僅計算DC電流(穩態電流/平均電流),對應到MFFT估算的是"平均"失效時間。

必須解過DC IR分析並勾選[Mesh Bondwires]、[Mesh vias],MTTF才可以使用。

必須解過DC IR分析並勾選[Mesh Bondwires]、[Mesh vias],MTTF才可以使用。

-

Check Result

- Q&A

8.1 做電熱耦合分析需要什麼license?

Ans:需要SIwave與Icepak license 或 Enterprise license (2020新)

8.2 MTTF中Ea與n這兩個係數該如何設定?

Ans:從SIwave HELP與[4][6]可知n值設1~2之間,並隨電流密度越大而越大,參照如下默認三檔設定即可。另外,做MTTF模擬時,溫度可以是由使用者自行設定(沒有Icepak時適用),或來自Icepak的計算結果。

各種基板常用導體材料,Ea該設多少?

參考[4][8]得知銅(Cu)的活化能分別是取0.84eV與0.79eV

參考[5][7]得知金(Au)的活化能分別是取1.523eV與1.1~1.26eV

參考[6]得知鋁(Aluminum)的活化能大約0.9eV,鎢(Tungsten)的活化能大約1eV

參考[4]得知無鉛製程(Sn/Ag)的Ea、n較難估計, 其範圍大約在n=1~2, Ea=0.68~1.07eV。但有些比較特殊的,如Sn-3.5Ag的n=4.6 特高,表示EM lifetime很短(很差)

Ea(活化能)的單位依維基百科說明是[焦耳/摩爾],但MTTF論文都是用eV(電子伏特),其與焦耳的關係是:1eV=1.6e-19 J。因Black's Equation是考慮流過導體截面的電流密度(J單位是A/cm2),與讓其產生電子遷移所需的能量(Ea),故後者不需以單位體積表示。

8.3 如何從SIwave匯出AEDT Icepak 3D模型?

Ans:[Export] \ [Icepak]

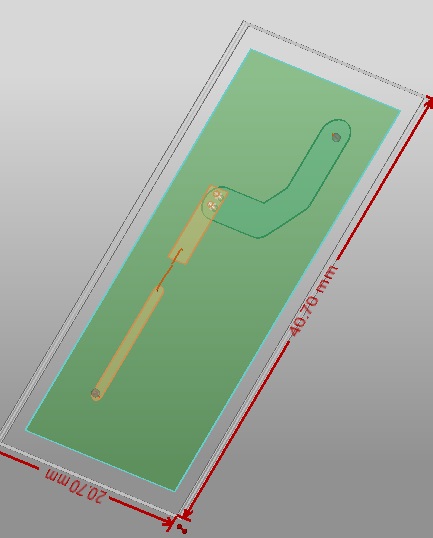

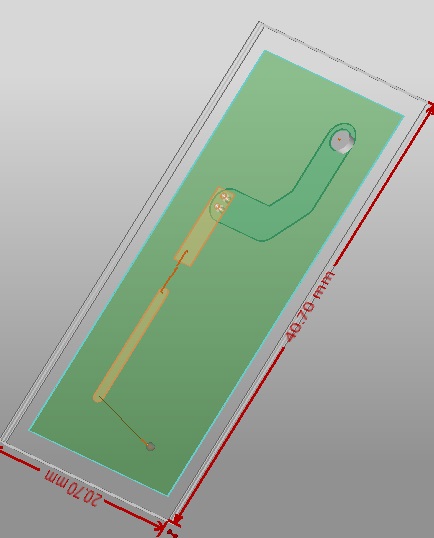

軟體會自動產生一個3D layout設計與一個Icepak設計,前者的3D模型與SIwave內定義相同,而後者則是等效簡化模型,且不含打線結構。

若要真實(無失真的)PCB 3D模型,或是需要考慮打線結構的熱模擬,請參考Q3D-Icepak模擬流程。

若要生成3D PCB時含3D元件模型(如上圖右所示),於SIwave內的Icepak模擬設定中,[Thermal Simulation Type]請選"Convection (Components optional)"

若想在此AEDT Icepak還環境下檢視原始layout,請選擇[3D Components]的該PCB,按右鍵打開[Properties]設定視窗,從[Visualization]把想看的層別打開即可。

8.4 為何同一導體材質,在不同論文中可能使用不同的Ea參數?

Ans: 導體材料的Ea,是在實驗室做長時間的可靠度測試,再以大量實驗數據與理論公式擬合(fitting)得到,故其確實會隨不同的產品結構與使用情境而不同。

8.5 本文介紹的SIwave-Icepak模擬流程,適合分析打線的熱嗎?

Ans:不行。(另文介紹bondwire/via的電熱耦合模擬該怎麼看,Q3D-Icepak或Q3D-Mechanical)

雖然SIwave內可以顯示打線(Bondwire)上的電流,但這電流跟via上的電流一樣,並無法透過SIwave傳給Icepak的power map,正確反應其熱在空間上相對的位置。

過孔的功率損耗帳會算在相鄰導體層該過孔的位置,同樣地,打線的功率損耗帳會算在打線落點(finger)位置。由於打線一般比起過孔長度長很多(貢獻功率損耗影響熱分佈較大),這種以2.5D近似的方式反映PCB的熱分佈還行,但若碰到要分析打線的熱分佈狀況就不行。

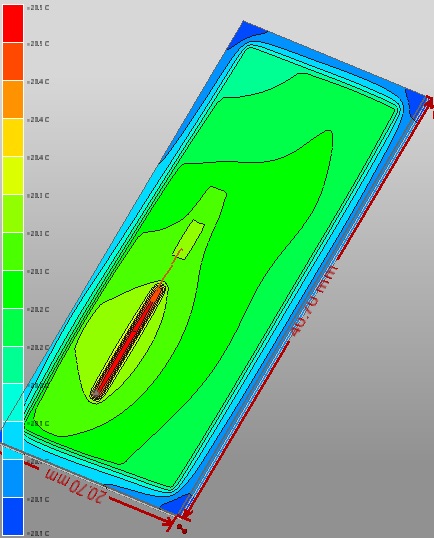

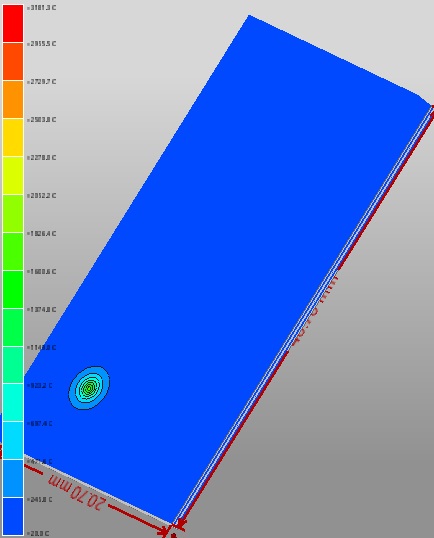

下圖左邊是本文沒有打線的例子,下圖右邊是多加一段8.2mm長的打線的例子(同樣抽1A電流負載)

做[conduction]模式下的電熱耦合分析,power map如下。可以看出右邊metal1的功率損耗大大增加

Icepak算出的熱分佈完全不同,原因就是:Icepak考慮右邊bondwire的熱都集中在打線落點處

(下圖左20.5度,下圖右卻是3181度完全不對)

上圖右不只整個熱點分佈不對,還會遇到兩個問題(雖然可以display temperature):

求解過程會遇到以下錯誤訊息,警告Icepak在[conduction]求解模式下所考慮的背景空間天花板沒有辦法涵蓋打線

還會遇到以下訊息:警告解出的溫度超過1000

大部份封裝的散熱分析透過考慮等效導熱率、疊構、錫球密度與位置,即可做得很好。

8.6 步驟5.2中,2019R3與2021R2的溫度分別是135.8與147oC,這差異11oC從何而來?

Ans:有兩個原因,但主要是網格分佈的質量

- 2019R3針對元件的溫度只以2D顯示,但2021R2針對元件的溫度則是以3D顯示

- 同一檔案R19.3與2019R3解完Archive後的檔案大小都是201M,但2021R2的檔案大小卻是138M。

新版不但求解後的檔案較小,求解速度也較快。透過與Q3D-Icepak的測試比對,135.8度比147較為準確,因為只要多佈一些網格,溫度就會下降。這其實就是在提供一個怎樣的默認求解環境(條件)給電性工程師做熱模擬,在速度與準度間的平衡。

SIwave-Icepak模擬流程採用"trace mapping"技術,以等效導熱率的方式簡化PCB幾何結構的複雜度。

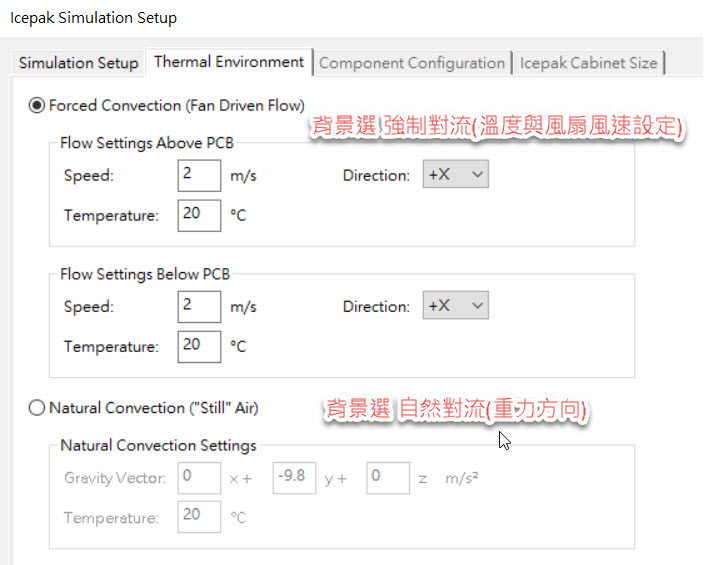

另外,5.2.1步驟中[Cabinet Size]背景空間的大小設定,對SIwave-Icepak影響不大,但對於Q3D-Icepak卻可能影響很大(如果Mesh沒設定好)。例如我們把[Padding Perpendicular Flow]從25%改成300%,因為Flow設定方向是+X,所以代表Y/Z方向的空間擴展會加大。

這樣在SIwave內看到的最大溫度只會略為不同:Z方向背景空間距離近(25%)的情況最大溫度147度,Z方向背景空間距離遠(300%)的情況最大溫度150.9度(只增加3.9度)。

SIwave-Icepak的[Simulation Setup]內的Meshing Detail設定,請設定[Detailed]即可,不需要設到[Exaustive]

使用SIwave-Icepak默認的Mesh設定,不論有沒有考慮元件熱的題目,得到的溫度都不會太離譜,這對初次接觸電熱模擬的電性工程師來說是友善的,但在SIwave介面下無法很有彈性的調整網格至最佳。使用Q3D-Icepak時,如果有考慮元件熱,Mesh必須加強,或背景空間不能太大,否則得到的溫度會過高,但對於有經驗的工程師,此環境下有機會透過指定網格得到更精確的結果。

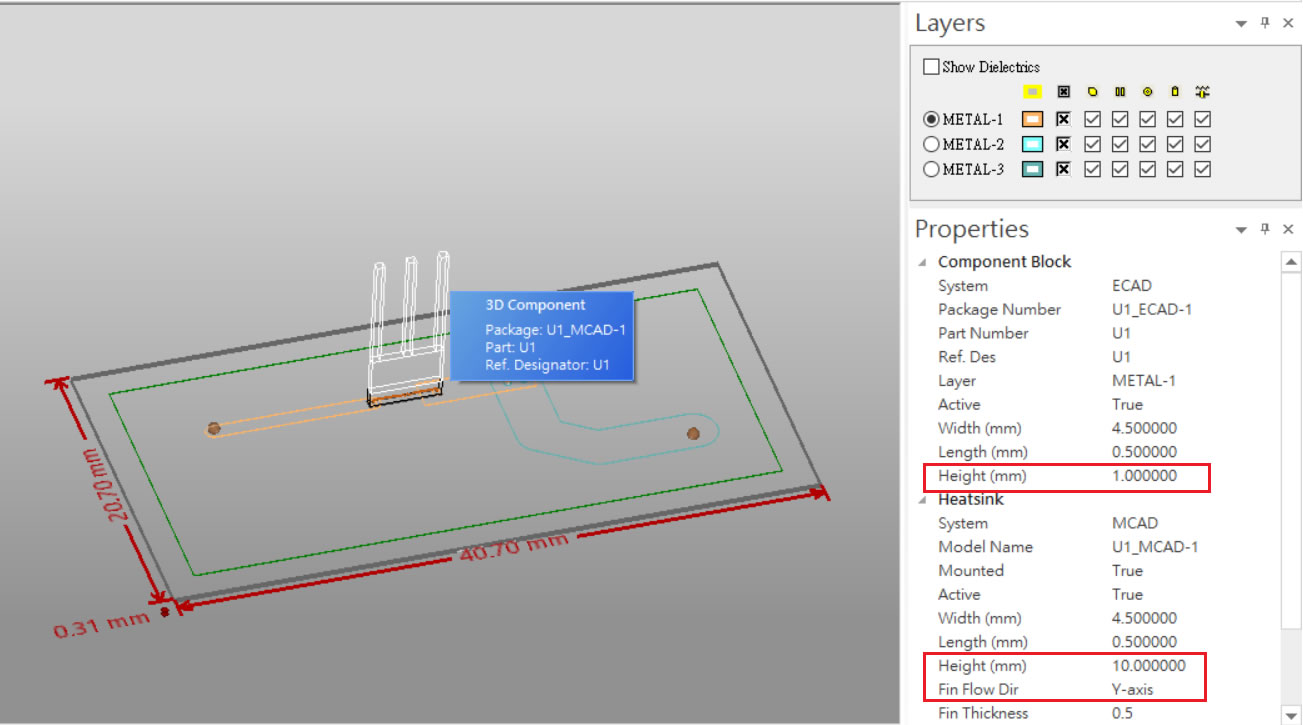

8.7 如何在SIwave內建立參數化的散熱片,並於Icepak模擬時考慮其對元件的散熱效果?

Ans:PCB上必須先有建立元件(component),才能設定(放)散熱片,因為散熱片是加在元件上的。

在SIwave的[Advanced]標籤頁下選擇[Heatsinks]

上圖按[確定]後,就可以在SIwave操作畫面下看到(默認大小的)3D元件與散熱片(Heat Sink)模型貼在U1上面。

當DC IR模擬完,接著進行Icepak模擬時,於步驟四選擇Convection (Components optional),然後[Component Configuration]此頁的設定就可以使用,用於修改"元件"本身的3D模型大小(非散熱片大小)。

上圖中U1與R1都可以勾選[Include],但只有U1可以勾選[Heat Sink],因為只有U1才是元件(component)。

R1的power Dissipation是軟體根據1A流過2 ohm計算出2W功率損耗,我們拿這值直接填給U1。原U1的功耗軟體默認值是0.25W,該值必須靠使用者根據元件實際使用狀況輸入,SIwave會根據P=I*V自動計算電阻的功耗。而這自動估算元件功耗能力只適用於電阻,LC元件則無。

以滑鼠選定散熱片,在屬性視窗中可以修改其結構參數,得到可參數化的散熱片。

8.8 步驟2中SIwave-Icepak自動匯入的.sitemp熱分佈檔,可在AEDT Icepak中單獨產生嗎?

Ans: 不行。目前這.sitemp檔只有在SIwave-Icepak模擬程序完成後,於SIwave工作路徑下自動生成

...\xxx.siwaveresults\0003_Icepak_Sim_2\SIwaveIcepakProj\board.1.sitemp

單獨執行AEDT Icepak模擬時,並不會產生.sitemp,此檔只有在SIwave-Icepak模擬程序中用來傳遞溫度分佈的定義。

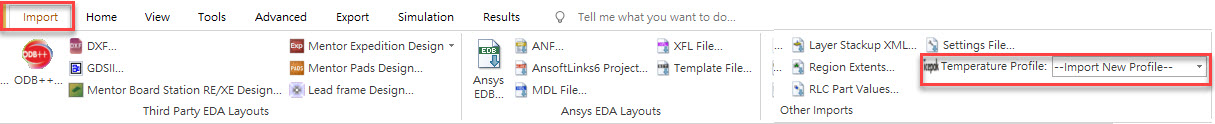

8.9 在新版SIwave options內設定,與用功能選單[Temperature Profile]匯入.sitemp,有何不同?

Ans: 在2022R1的SIwave options設定中,多了如下的[Temperature]設定標籤,1、2處使用的.sitemp格式相同

而下圖從[Import] \ [Temperature Profile]匯入.sitemp的方式,僅供SIwave"顯示"溫度分佈之用,solver並不會使用。如果是要讓DC/SYZ solver使用的.sitemp匯入方式,請從SIwave options內的設定匯入。

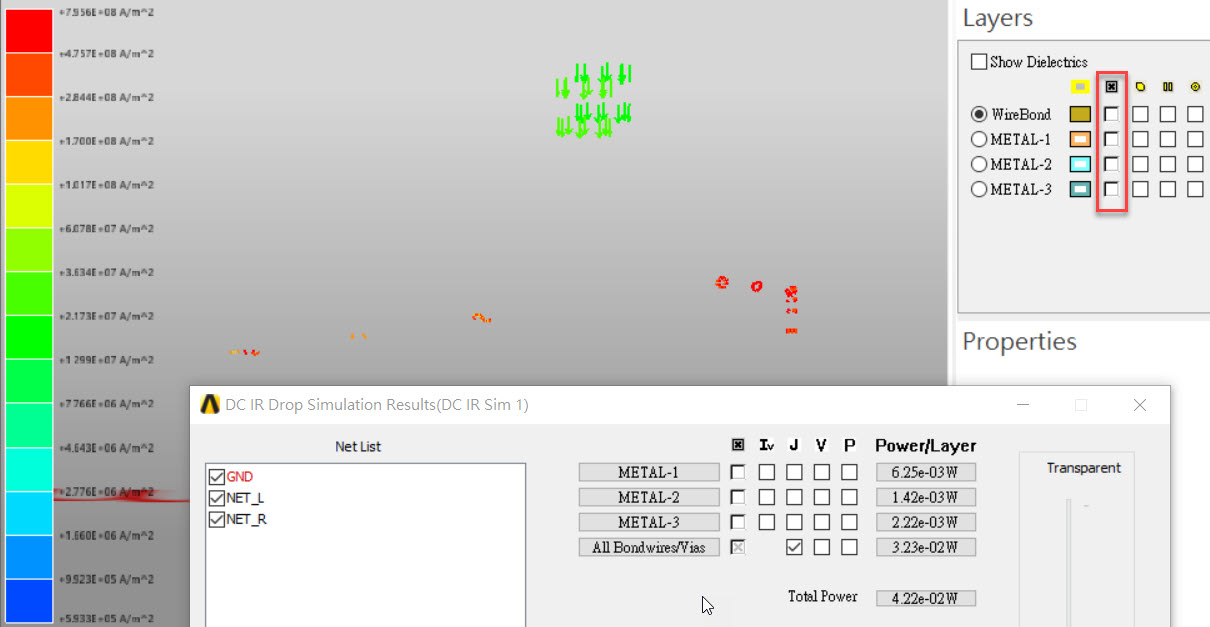

8.10 步驟3中,為何 就算勾選了[All Bondwires/Vias]還是看不到bondwire/via/ball上的電流密度?

Ans: 如果你像下圖看不到Bondwires/Vias位置的電流密度J

請暫時先取消各layout層的顯示即可清楚看到

-

[1] Electro-thermal Analyses of a PCB - Part I

[2] Electro-thermal Analyses of a PCB - Part II

[3] J. R. Black, "Electromigration-A Brief Survey and Some Recent Results", IEEE Trans.on Electron Devices, April 1969.

[4] Lou Nicholls, "Comparative Electromigration Performance of Pb Free Flip Chip Joints with Varying Board Surface Condition", Electronic Components and Technology Conf, 2009.

[5] Y. Zalaoglu, "An effective research for diffusion annealing temperature and activation energy in Au surface-layered Bi-2212 ceramic composites", Journal of Materials Science: Materials in Electronics, 2017.

[6] Xiaoxin Zhu, "Progress in the Development of an Electro-migration Modelling Methodology", 10th World Congress on Computational Mechanics, May 2014.

[7] C.L. Gan, "Reliability Assessment and Activation Energy Study of Au and Pd-Coated Cu Wires Post High Temperature Aging in Nanoscale Semiconductor Packaging", J. Electron. Packag. June 2013.

[8] C.W. Park, Activation energy for electromigration in Cu films, AIP Publishing LLC., 1991.