線上影音

Home > ANSYS SIwave教學> Merge Package and PCB

本文始於2009年,2014重新以SIwave 2014介紹如何將BGA.siw與PCB.siw結合成為BGA_on_PCB.siw,產生一個從BGA package到PCB board level的一個完整模型。這步驟在SIwave v3.5是藉由一個"pkgonpcb.exe"外掛程式來執行merge的動作,在SIwave v4.0以後則是直接在主程式內執行。

-

問題與討論

4.3 為何看起來bond wire是飄浮在空中沒有與finger pad真正接觸?

4.4 為何單看PCB與BGA的loss都不大,但兩者結合起來的loss卻增加很多(增加量不是加成的效果)?

4.5 單獨抽取PCB與BGA的model後,在Designer或HSPICE內串起來模擬,與直接把BGA+PCB 3D merge的差異?

-

參考

![]()

-

打開PCB.siw,設定單位為[mm]

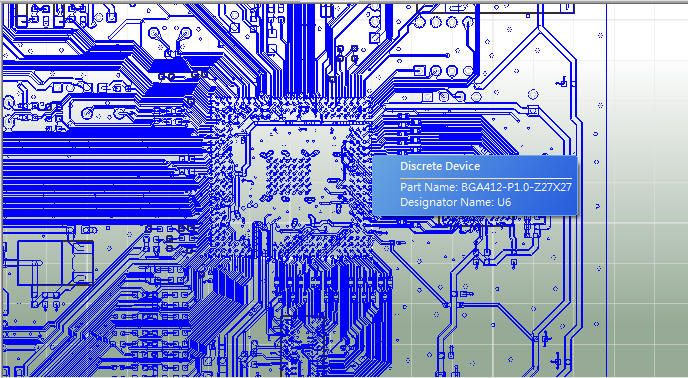

檢視並記下BGA part name與designator name (BGA412-P1.0... and U6 for the example as bellow)

-

打開BGA.siw,設定單位為[mm]

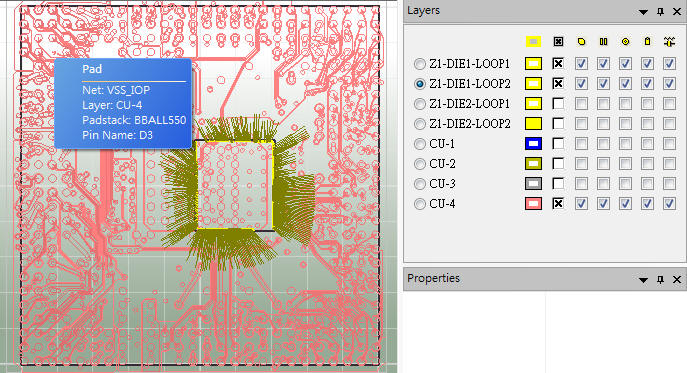

檢視並記下BGA padstack (BBALL550 for the example as bellow)

- 打開PCB.siw,然後執行[Tools] \

[Attach Package

Design]

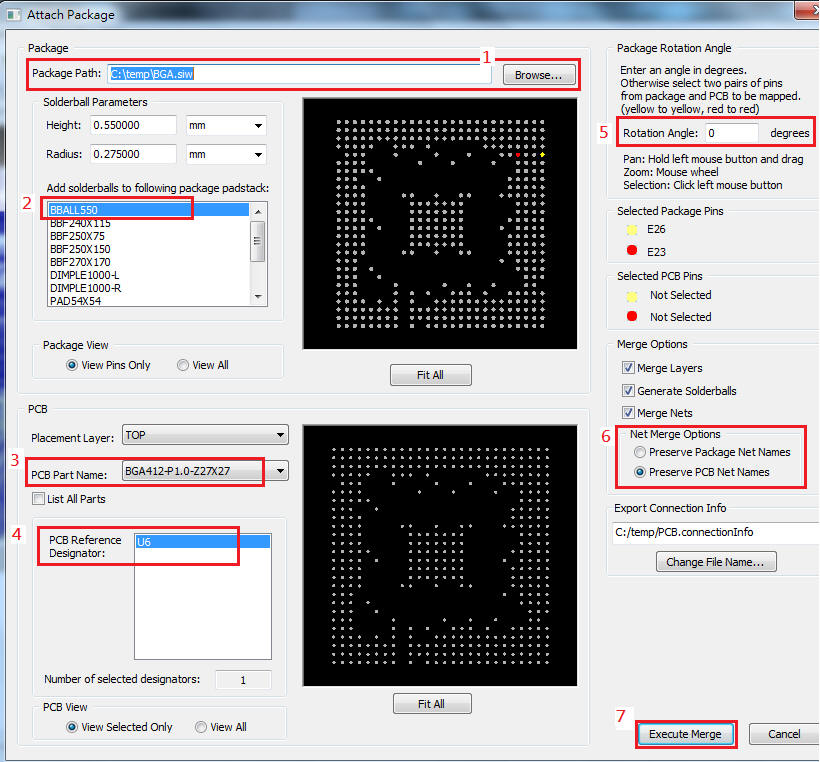

3.1 輸入由package design file(.mcm)轉出來的BGA.siw所在路徑

輸入BGA ball參數(高度、半徑),請注意錫球溶解後高度會下降,半徑會增加

3.2 選擇[package padstack]

3.3 選擇在PCB上,此顆BGA的Part Name

3.4 選定此顆BGA的零件編號 (如果同一個part name的BGA,在此PCB上不只一顆,這裡就會出現一個以上的designer name)

3.5 檢視BGA球位置與PCB pad位置,是否需要旋轉 (軟體會自動選定幾顆ball對位,for example, E23, E26)

3.6 選擇若是有遇到net名稱相同,保留哪一邊的net name

3.7 按執行 ,會跳出一個詢問視窗,直接按ok就會產生一個合併BGA+PCB的檔案

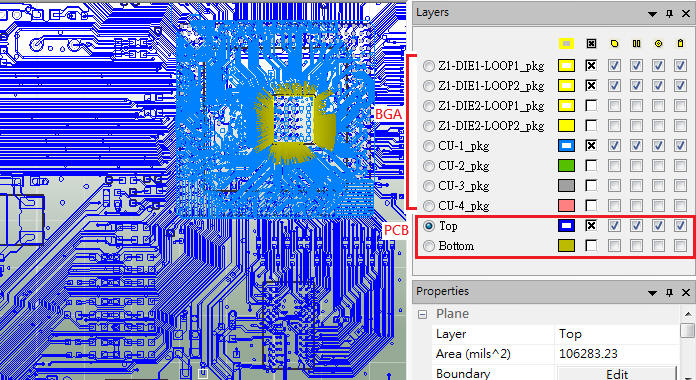

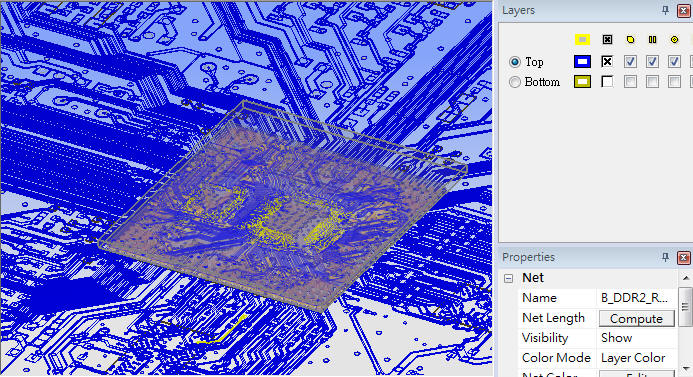

正常的合併後結果如下:

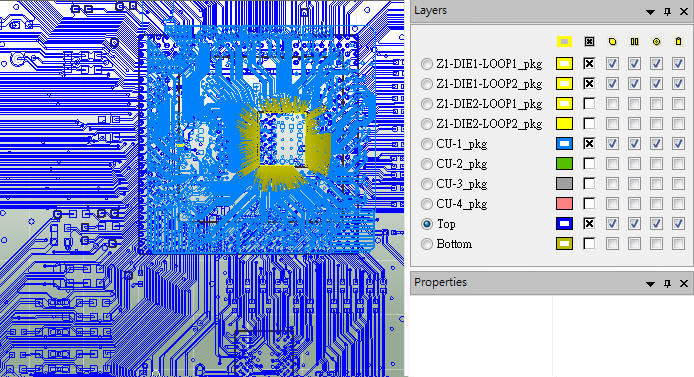

錯誤的合併結果,發生座標偏移現象:

座標偏移的原因是:[package padstack]選錯了,或BGA.siw與PCB.siw的單位不一致 ,建議都設成[mm],與ball的默認單位配合

如果merge後發現net name都不對,請注意是否忘記旋轉(step3.5)

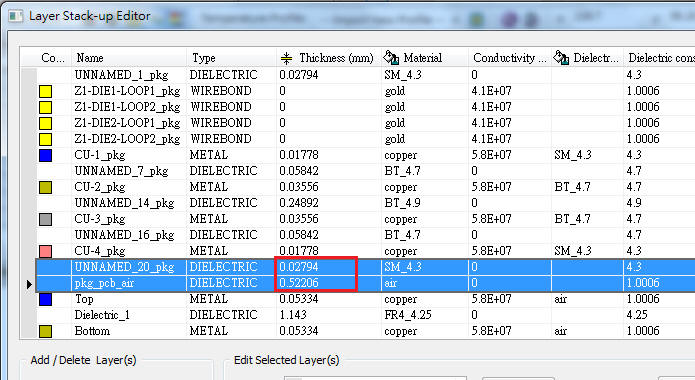

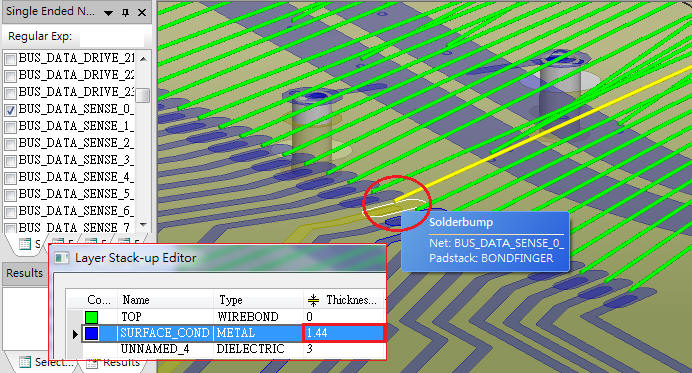

整個合併完成後的堆疊如下,錫球高度正是0.55mm

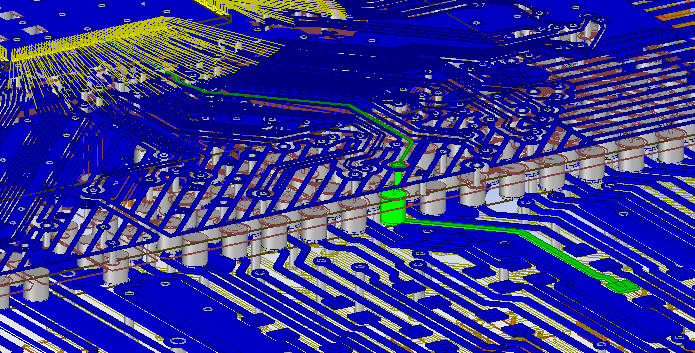

整個合併完成後的SIwave圖示如下,可以看到一條net從Die pad -> Bonding wire -> BGA Substrate top layer -> via -> BGA substrate bottom layer-> 錫球 -> PCB top layer導通

-

問題與討論

4.1 PCB上merge的package數目有限制嗎?

Ans:沒有限制數目 ,而且正面貼合與背面貼合都可以做,只要merge時相對的layer與padstack選對即可。

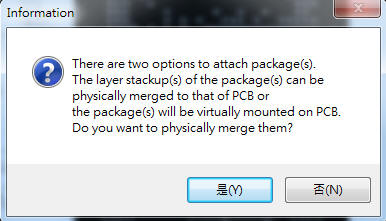

4.2 step3.7中跳出的詢問視窗是做何用途?

Ans:如果沒有選擇"physically merged"而是用"virtually mounted",BGA layer在Layer Stack-up並不會出現(沒有真的匯入SIwave),但可以看的到,如下圖所示。其原本是為了merge不同堆疊定義的BGA封裝,讓ALink可以Export to Q3D or HFSS to solve it,但筆者實測的結果,"virtually mounted" does not work ?

4.3 為何看起來bond wire是飄浮在空中沒有與finger pad真正接觸?

Ans:參考 這裡

4.4 為何單看PCB與BGA的loss都不大,但兩者結合起來的loss卻增加很多(增加量不是加成的效果)?

Ans:打個比方:單獨分析BGA在1G的S21=-0.5dB、PCB在1G的S21=-1dB,但合起來model在1G的S21=-2dB而不是-1.5dB。這是因為多了訊號從BGA傳遞到PCB時,在兩者介面間因阻抗不匹配所引起的損耗。參考這裡

4.5 單獨抽取PCB與BGA的model後,在Designer或HSPICE內串起來模擬,與直接把BGA+PCB 3D merge的差異?

Ans:前者沒有考慮BGA的最下層trace與PCB上層trace之間,在三度空間上的coupling。至於這差異在多高頻寬才有影響,參考這裡。