線上影音

Home > ANSYS Q3D 教學 > Partial and Loop Inductance

本文始於2015年,主要介紹電感與迴路電感,並於2018年新增第七節。相信您一定知道什麼是電感,高中就學過V=L*di/dt。但您清楚loop inductance與partial inductance的差別嗎? 多打bond wire或多加via並聯,電感效應會變小,這觀念從沒懷疑過,對吧!請您繼續看下去...。(全文除了step5.1是用HFSS做的,其他都是用Q3D做的)

The article started in 2015 and was revised in 2018. It is intended to introduce several important concepts of inductance (as loop and partial L) with Q3D 2015. Even a senior engineer may misunderstand them sometimes, while you will get right points easily here.

-- Add section 7 and update example with Q3D 2018.1. 2018.07

-

Introduction

-

阻抗與電感並聯計算的關係 (Parallel Calculation for Inductance)

-

多打bond wire或vias,PI的電感性不一定變好 (Loop Inductance not always smaller with more bond wires in parallel)

-

Inductance decreases with frequency increasing

-

Plane挖洞,PI的電感性不一定變差 (Inductance of plane not always worse with anti-pad voids)

-

問題與討論Q&A

8.2 導體電感與導體截面積呈正比嗎? No, No, No

8.3 磁向量位勢(vector magnetic potential)到底跟電位有什麼類比關係?

![]()

-

Introduction

首先,電阻與阻抗不同,後者才能完整表達導體的被動(passive)效應。

又,電感元件(inductor)與電感(inductance)不同,後者是電流流過材料所造成的,而電流必須有迴路才會流動。

1.1 阻抗

阻抗Z=R+jX=R+j(XL-XC)=R+j(wL-1/wC)。其中阻抗實部為電阻ZR=R,虛部則由感抗ZL=jwL與容抗ZC=1/jwC所構成 [1]

ZL=jwL

XL=2pfL=wL ... 隨頻率增加,此項對電路的影響也會增加

高頻時,電感將變成重要的影響因素. (for example, loop inductance impacts decoupling performance very much)

1.2 電感

1.2.1 法拉第定律描述磁場如何產生電場:時變的磁通量會產生感應電動勢

電感是材料抑制電流瞬間變化的能力 (可將時變的電流轉成電壓儲存能量)

必須有電流迴路(面積A)與時變的磁場,才能產生感應電動勢。電感與面積有關

並且迴路面積對自感的影響,比導體本身的尺寸來的大 [2], p.7

電感跟迴路面積關係最大,其次是電流密度。 [2], p.46

1.2.2 對於Lloop_DC,則可以透過磁通量y來描述 [3], p.35

磁通量y

磁通量密度B

磁向量 位勢A (vector magnetic potential) ,其平行於電流方向,並且在無窮遠處為零 : 定義

。

電感是電流流過材料時,產生磁通量的能力 (單位電流所產生的磁通量)

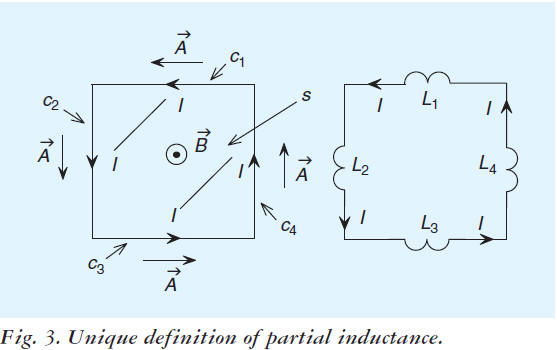

1.3 Loop Inductance and Partial Inductance [2] p.14-16, [3] p35-36

由法拉第定律所導出的total loop inductance是迴路整體的效應,沒辦法區分出電源與地路徑上各別的電感,即難以分析 電感對power bounce或ground bounce分別的影響,所以有了partial inductance的定義。

為了得到每一線段的partial inductance,定義了 磁向量 位勢A, 可以把磁通量密度基於面積分的關係,轉為 磁向量 位勢 基於線積分的關係 。

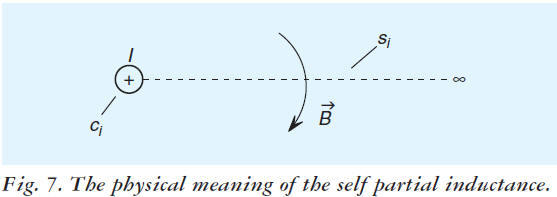

The self partial inductance of a segment of the contour of a closed loop is the ratio of the magnetic flux penetrating(穿透) the surface between that segment and infinity and the current on that segment as shown below.

Total Loop Inductance = sum of all Lself and Lmutual (for example, L1+L2-L12-L21)

總迴路電感效應,可以用自感與互感(partial inductance)來集總表示。這裡的互感可能為正(Ip1, IP2同向)、為負(Ip1, IP2反向)或為零。

在Q3D內透過reduce matrix "return path"計算loop L時,要特別注意訊號線與迴路線的sink\source要分別在同一側(比方說die端都設sink, Ball端都設source),因為reduce matrix會自動把return path上的電流反向(也就是L1+L2-2*L12式中負號代表的意思)。如果訊號線與迴路線的sink\source在不同側(比方說訊號線sink設在die端,但迴路線的sink卻設在Ball端),那互感在計算return path前就是負值,經過L1+L2-2*L12後,互感值會負負得正,導致loop L暴增。

Loop Inductance有可能會小於partial inductance,且這情況不罕見。常出現於訊號導體與迴路導體接近(互感大),且 迴路導體阻抗\電感值小的情況下發生

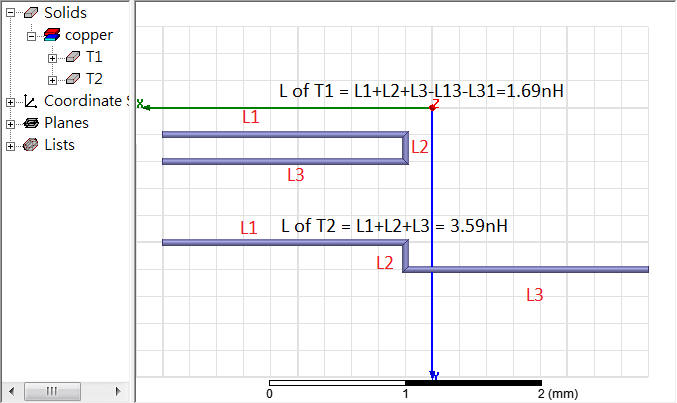

比較兩段長度相同的導線,其中一條T1對折(有較大互感)。可以在Q3D中輕易地觀察出兩者LDC不同,T1明顯較T2小。

對照前一節所介紹的loop inductance與partial inductance,了解Q3D的計算是基於partial inductance,且其RLCG是從阻抗Z得到的。

-

阻抗與電感並聯計算的關係 (Parallel Calculation for Inductance)

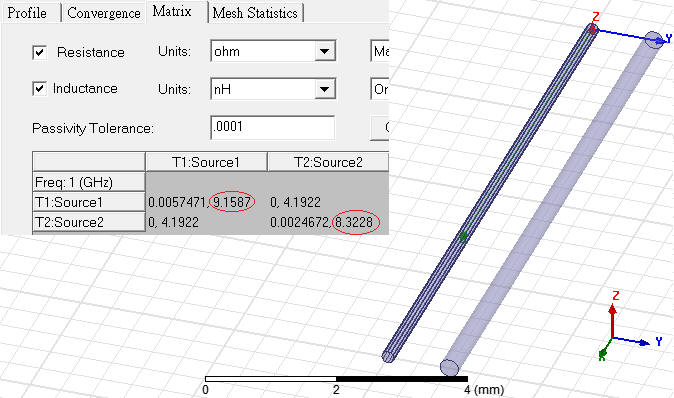

3.1 兩條"相同"的導線,電感(Lp1, Lp2)並聯並不是除以2這麼簡單,還需要考慮互感(Mp=Lp1p2=Lp2p1)。

除非兩條線 彼此夠遠,其互感Mp夠小,那這兩條導線電感並聯值才是除以2。 [2], p.32

As

Lparallel=(9.15+4.19)/2=6.67nH ... 正好是Q3D reduce matrix [join in parallel]算出來的值

3.2 但即便有考慮互感,兩條"不同"的導線,電感並聯仍然不是[2], p.32所示的公式。

原因是當兩條Z值差異較大的導線並聯時,RDC值較小的導線上會流動較多電流,其貢獻的電感值會增加,所以並聯的電感值會略大於公式所算出的值。 (別忘了我們才介紹過,電感與電流密度有關)

Lparallel=(9.15*8.32-4.192)/(9.15+8.32-2*4.19)=6.44nH ... 略小於 Q3D reduce matrix [join in parallel]算出來的值6.66nH

3.1與3.2例的差異在於:3.1中兩條線的RDC是相同的(5.7 mohm),故兩線並聯時,電流是均分1/2流過;但3.2的兩線 RDC差一倍,故往T2的電流會比T1多一倍,造成並聯後的真正電感略增。簡言之, [2], p.32所示的電感並聯計算公式只適用於結構相同的兩條線段並聯時使用,若不相同的兩條線並聯計算,該式中的互感項Mp=Lij要改成互阻Zij才可以 。

-

多打bond wire或vias,PI的電感性不一定變好 (Loop Inductance not always smaller with more bond wires in parallel)

從3.1與3.2例 可知,若封裝內有一個net使用約等長的double bonds,只把一條bond wire變粗對於降低整體迴路電感其實沒有太大幫助,除非把兩條bond wire都加粗。 另 一種常 見的狀況是:多打bond wire或via,但PI (loop inductance)並沒有比較好,這讓工程師很困惑,並且情感上很難接受

。

下圖所示的例子,四組從source to sink (共八條bond wires)的RDC約0.08~0.09 ohm,彼此差異不大,但左邊的兩組loop inductance(3.5~3.7nH)比右邊 的兩組 (1.5~1.9nH) 大約一倍,這種情況下bond wire是放左邊還是放右邊,結果是截然不同。因為RDC差不多,所以原本的4組path上流動的電流大約各是0.25*Itotal,但若把bond wire縮減成三組,每一組的電流會變成0.33*Itotal。

更多的並聯 路徑,電感不必然變小 。所增加的並聯路徑位置,必須在loop inductance較小的區域才有效。也就是說:增加bond wire或via所改變的電流分佈,必須能讓電流集中到loop inductance較小的path,那整體的loop inductance才會減少。

-

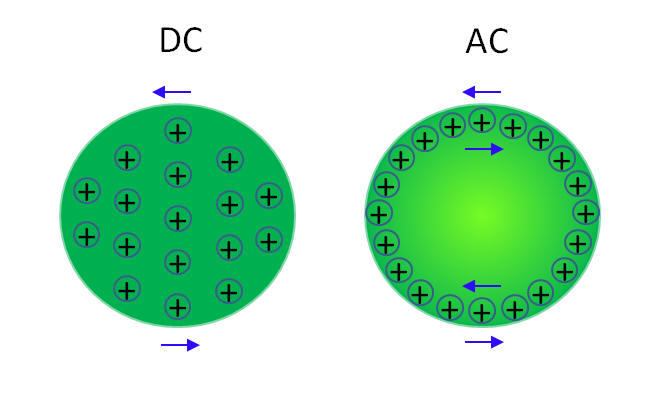

Inductance decreases with frequency increasing

大家所習知的:因為肌膚效應,電阻隨頻率增加而呈指數級的增加。

但電感隨著頻率增加而減少,這該如何解釋呢?

5.1 對於U型導體 [2],p.27-30

頻率不同時的電流迴流路徑不同,以HFSS示範一長2.2", 寬10mils, 厚1mils, 距離GND 10mils的U型線,其1KHz, 1MHz與1GHz的電流迴流路徑,以及電感隨頻率的變化。發現高頻時迴流路徑直接在導線下方 循最小迴路面積迴流(L dominates the path with min. Z),而低頻時迴流路徑直接找最短直線距離迴流(R dominates the path with min. Z),此時迴路面積是較大的,所以低頻的loop inductance會增加,而且增加很大。(50n<-24nH)

5.2 對於直線導體

因為肌膚效應,電阻隨頻率增加而呈指數級的增加。若橫軸與縱軸皆以指數(log)表示,那電阻R在進入肌膚效應區時(2MH~)與頻率變化呈線性。

但電感隨著頻率增加略為減少,且降低的量極小(9.2n->8.8nH)。這是因為當肌膚效應發生時,集中於導體表面的電流根據安培右手定律,在"導體內"所產生的磁場\磁通量密度,會有些微抵銷的現象。

電感隨頻率增加而減少,有兩個原因:

-- 若減少很多,表示因高頻與低頻的電流迴路面積不同所造成。

-- 若只減少一點,表示因高頻肌膚效應所造成的導體內部些微磁場互相抵銷的現象。

5.3 更進一步,我們比較實心導體與空心導體的電感

虛線是空心,實線是實心導體。空心導體在低頻L反而是比較好的。

一般以為電流截面積較小的導體,R與L都會較大,這觀念在實心導體是對的,但在空心導體,L非但不會變大,還會變小。筆者特別點出這現象,是為了下一章節鋪陳。

-

Plane挖洞,PI的電感性不一定變差 (Inductance of plane not always worse with anti-pad voids)

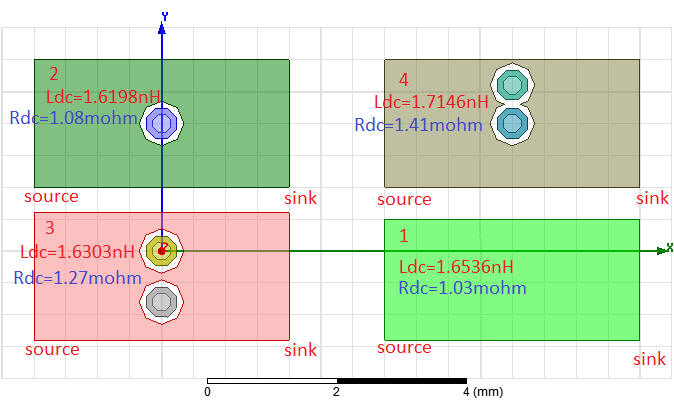

以下四種情況,何者的平面阻抗(partial R, L)最小?

case1的RDC最小,這很直覺,但LDC最小的是哪一個?

case2的LDC最小,原因是導體內被anti-pad分流的上下"對稱"電流,會對 磁路上的部份磁場產生些微抵銷的現象,所以L變小。

注意case3, case4都是打兩個via,而case3是比較理想的做法

After assigning sink\source on a suitable return path, R19.1 Q3D can get pretty consistent loop L as HFSS get.

對這項目有興趣讀者,可參考以下兩堂Q3D進階課程

Q3D的RL要如何與HFSS結果正確比較? Part I, B站, 範例

Q3D的RL要如何與HFSS結果正確比較? Part II, B站, 範例

想進一步了解Q3D如何從RLC結果算出S-parameter,請參考

Q3D Extractor HELP > Q3D Extractor Technical Notes > S-Parameter Calculations in Q3D Extractor

-

問題與討論Q&A

8.1 如何從SYZ模擬結果換算出Inductance?

Ans:

As Z=R+j(wL-1/(wC))=1/Y

計算迴路電感:

Case1用Im(1/Y11)/(2*pi*freq)計算迴路電感(loop inductance),而不是Im(Z11)/(2*pi*freq)。

在舊的軟體版本,HFSS內plot L使用Im(1/Y11)/(2*PI*freq),而在Designer內plot L則需使用Im(1/Y11)/(2*PI*f),請注意兩個操作環境內定的頻率表示參數不同。此惱人的差別,在新版(2020R1起)已修正;新版Designer circuit內,使用f或freq都可以得到正確(一樣)值。

計算迴路電阻:

Case1用R=Re(1/Y11)計算迴路電阻,而不是Re(Z11)。 前者才有考慮地迴路的電阻。

使用Y11或Z11換算RLC,主要取決於另一端(port2)要short或open。使用Y11取值換算時,表示p2 port是short to reference

計算電容:

對於一個導體(net)只有一個port的情況(open circuit):Cself=1/Im(Z11)(2*pi*freq)

對於一個導體(net)只有一個port的情況(open circuit):Cmutual=Im(Y21)/(2*pi*freq)

注意:不能使用Im(1/Z21)/(2*pi*freq)計算互容

- 計算電導(Conductance, G):

G11=Re(1/Z11) , G21=Re(1/Z21)

如果希望HFSS算出的G11與G21與Q3D相同,需要在HFSS內將air box取大一些,並且把air box的radiation boundary BC拿掉,也就是用默認的PCE當air box屬性。

8.2 導體電感與導體截面積呈正比嗎? No, No, No

Ans:電感與迴路面積呈正比,並非導體截面積,這完全是兩碼子事。迴路面積越大儲能效果越好,故電感越大,這與磁路的截面積有關,而不是電流的截面積,千萬別搞混了。

The inductance value of a conductor increases with larger loop area, but regarding to cross-section area, how does inductance value change with that? It depends.

對於實心導體,以step3.2為例,我們可以看出較細的導體(截面積小)有較大的電感值。

別忘了電感是阻止電流瞬間變化的能力。

對於空心導體,以step5.3為例,我們可以看出實心的導體(截面積大)有較大的電感值。

別忘了對稱的電流分布可以產生磁場抵銷的作用。

8.3 磁向量位勢(vector magnetic potential)到底跟電位有什麼類比關係?

Ans: 磁向量位勢線積分得到的磁通量,類比於電場線積分得到的電壓

8.4 step2,3,5.2的例子中,並沒有參考平面,Q3D是以何處為迴流路徑計算電感的?

Ans:Q3D計算的是partial inductance,所以這問題本身是不存在。有這疑問表示不清楚partial inductance的數學與物理上定義。請參考[3] p.35-36,並參考Q3D進階課程Q3D生成S參數模型時,如何考慮參考地位置?

若把step2中的U型導體(T1 line)在Q3D中試著畫出如step5.1電感隨頻率的變化,將會看到高頻的電感只比低頻減少一點(下圖藍色實心線),即只呈現了導體內因肌膚效應所造成的電感差異,並無法顯出如step5.1中因迴路大小改變所造成的電感差異。

如果要Q3D以本身以外的導體當return path,方法是透過後處理,在reduce matrix內指定[return path]。這樣就可以看到電感隨頻率變化的幅度明顯變大了(下圖綠色實心線)。

8.5 電感隨頻率增加而開始變小的頻點,與電阻開始隨肌膚效應變大的頻點相同嗎?

Ans:對於5.2的情況,兩者發生的頻點相同,即發生肌膚效應的頻率,但對於5.1則不同,L開始變小的頻點較早發生 ,即此時電感變化並不是因為肌膚效應所造成。

[1] 阻抗, Electrical Impedance

[2] Bruce Archambeault, "Inductance and Partial Inductance What's it all mean?", IEEE EMC Society Newsletter, Winter 2010 (推薦)

[3] Clayton R. Paul, "Partial Inductance", IEEE EMC Society Newsletter, Summer 2010 (推薦)

[4] 磁向量 位勢(vector magnetic potential \ magnetic vector potential \ vector potential) , ref1 , ref2

[5] Randy Wolff, "Signal Loop Inductance in [Pin] and [Package Model]", DesignCon IBIS Summit 2010