ANSYS Designer以前稱做[Designer-Nexxim],這樣的稱謂常讓初學者一頭霧水,經過一段時間才了解:Designer circuit是一個功能強大的電路模擬環境/平台,而Nexxim則是其circuit simulator。

早期ANSYS Designer是一套獨立產品,之後拆分成DesignerSI、DesignerRF兩套產品。自2020年起,其大部分功能整合進EBU各旗艦型產品內,也就是說SIwave/HFSS/Q3D/Maxwell Premium內含原Designer circuit除了AMI/QuickEye/VerifyEye analysis以外的所有功能。而AMI/QuickEye/VerifyEye analysis這些電路分析進階功能,則需Electronics Enterprise產品才包含。

其有兩個主要使用面向

基礎課程:

Lesson 01:傳輸線預模擬 (Pre-Simulation). 範例

Lesson 02:串擾(CrossTalk)與反射(Reflection). 範例

Lesson 03:Overshoot/Undershoot from Reflection. 範例

Lesson 04:DDR and ODT simulation. 範例

Lesson 05:DDR3 simulation using SPICE Model, 範例1, 範例2

Lesson 06:眼圖分析與IBIS-AMI. 範例 (2014年度精選, 2022更新)

ANSYS安裝目錄C:\Program Files\AnsysEM\AnsysEM18.1\Win64\Help\Circuit\GSG,裡面有

幾份Getting Start Guide

ANSYS安裝目錄C:\Program Files\AnsysEM\AnsysEM18.1\Win64\Help\Circuit\GSG,裡面有

幾份Getting Start Guide

進階課程:

Lesson 07:Differential pair Quick-Eye Analysis by SIwave(+ Designer). 延伸閱讀02

Lesson 08:如何以Designer建立一個帶雜訊成份的電源模型, 範例

Lesson 09:Differential pair with different space. 範例1, 2, 3

--

分別以Designer/Nexxim、SIwave、HFSS分析differential pair線間距對傳輸訊號的影響

Lesson 10:ESD Gun Model and ESD Simulation, 範例

(2013年度精選)

Lesson 11:DDR4 and DDR Compliance Test. 範例 (2017年度精選)

Lesson 12:PAM4 and MIPI, 範例

Lesson 13:CMA(Chip Model Analyzer), 範例

其他介紹

AN 01:介紹如何以一個Designer circuit跑數個不同condition 的.snp模擬比較

AN 02:如何求得microstrip

line的有效介電係數

AN 03:Eye Analysis for Differential pair, Part I. 範例

AN 04:Eye Analysis for Differential pair, Part II. 範例

AN 05:Different PRBS generator in Designer. 範例

AN 06:IBIS over clocking. 範例

AN 07:如何在電容位置下port,讓電容於電路外接做模擬? 範例

AN 08:如何正確地得到訊號的頻譜成份? 範例

Q

& A (點擊以下項目,展開內容)

-

Designer 各版的主要新增功能

--Designer v8:大幅改善了對IBIS-AMI的支持兼容性,至少有十家IC vender support list,整合IBIS與IBIS-AMI的導入路徑與symbol,新增Project Archive function整合Circuit design與System design

-- Designer 2014(R15):support x64位元的軟體版本,新增causality check function

-- Designer 2015(R16):support IBIS-AMI Repeater (redriver\retimer),HPC for Transient parallel bus speedup

-- Designer 2016(R17~R17.2):state-space fitting improve, IBIS 6.0 parser support, virtual compliance for LPDDR4, support coupled RLC package model .pkg in IBIS simulation(R17.2), probing die side of package, support "DLL_path" keyword in IBIS 6.0 during IBIS-AMI simulation

-- Designer 2017(R18):support PSPICE and support PAM4 for IBIS-AMI and QuickEYE.

-- Designer 2018(R19):PAM4 support for IBIS-AMI, QuickEye, and VerifEye. Added Spread Spectrum Clocking components

-- Designer 2019R1(R19.3):Added frequency-dependent voltage and current sources

-- Designer 2020:Duty Option for ss_clock Component and DC-preserving passivity enforcement algorithm IFPVLF.

-- Designer 2021:Support LTSPICE model, Single-ended IBIS-AMI, ISO7637 EFT source in Circuit EMC component

-- Designer 2022:Dynamic link frequency sampling points for circuit-field Solver co-sim, PSPICE model export for Q3D RLGC state-space fitting, add more source compoments for EMC(EFT, ESD).

-- Designer 2023:New EMI receiver component with Peak/QuasiPeak/Average and RMS Detections, calculate ERL w/o using COM flow, Support for AMI Reserved Parameter DC_Offset, remove trise/tfall from IBIS-AMI Tx component, S_element model order reduction and add some SiC MOSFET models.

-- Designer 2024R1:MIPI C-Phy transmitter component, Semiconductor characterization tool (beta) and Motor models for Power Electronics and EMC.

-

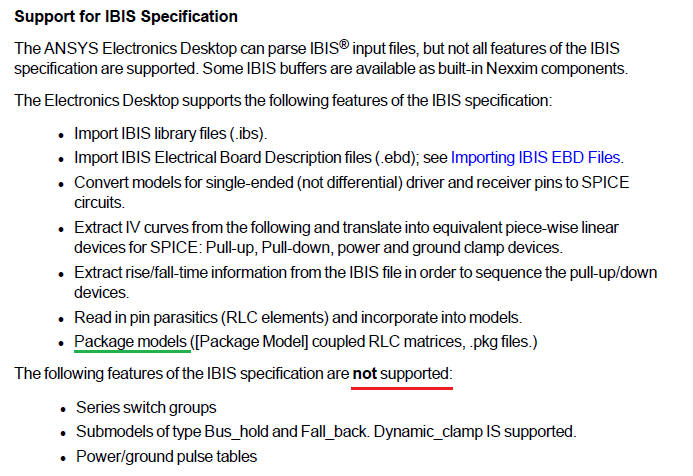

Designer對IBIS的支持狀況如何?

-- Designer從v6.1開始支持.ebd,從2016.1開始支持package

coupled RLC (.pkg) in IBIS。這裡的支持.pkg是指會考慮.ibs內所包含的[package

model]關鍵字下所定義的RLC矩陣內容,並非可以單獨匯入.pkg file。以下是從Designer Circuit R18.1

HELP內節錄的內容

--

Designer基本上是支持IBIS 6.0的,但有三個特殊功能例外,如下所示

-

Designer\Nexxim v5.0與Designer v6.0有何差異?

v6.0以前的版本,Designer與Nexxim需要分開安裝;從v6.0開始,使用者會漸漸感覺不到Nexxim的存在,安裝完Designer即會內含Nexxim與Library,並且不再看到[Nexxim]這字眼,而是直接以[Circuit]取代,讓使用者清楚感受到原來[Nexxim]只是[Designer]平台下的一個電路模擬引擎

ANSYS安裝目錄C:\Program Files\AnsysEM\AnsysEM18.1\Win64\Help\Circuit\GSG,裡面有 幾份Getting Start Guide