線上影音

Home > ANSYS SIwave教學> How does PI affect SI, SSN and EMI

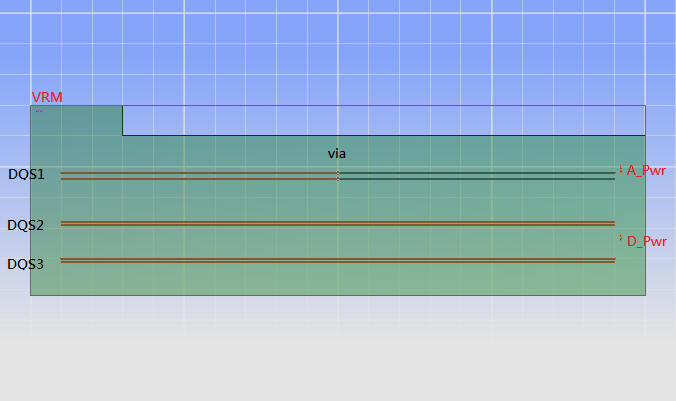

本文旨在為學習過SIwave\ Lesson 20的讀者,使用SIwave 2015針對SI+PI模擬提供基礎學習\練習,以非常簡易的例子,探討不同的電源與地平面設計(PI),對SI、SSN、EMI所造成的影響。 範例

-

參考平面(P\G plane)完整時

-

參考平面(P\G plane)不完整的SI、SSN、EMI

-

參考平面(P\G plane)不完整,但經優化後的SI、SSN、EMI

3.1 電源平面與地平面都分割,但沒有割斷彼此連接的情況下,增加decap.電容優化PI

-

問題與討論

4.1 為何DQS3的SI (jitter, 眼高)總是比DQS1差? (重要)

4.2 為何DQS1有經過一次的過孔換層,但卻不覺得其SI比較差?

-

參考資料

![]()

- 參考平面(P\G plane)完整時

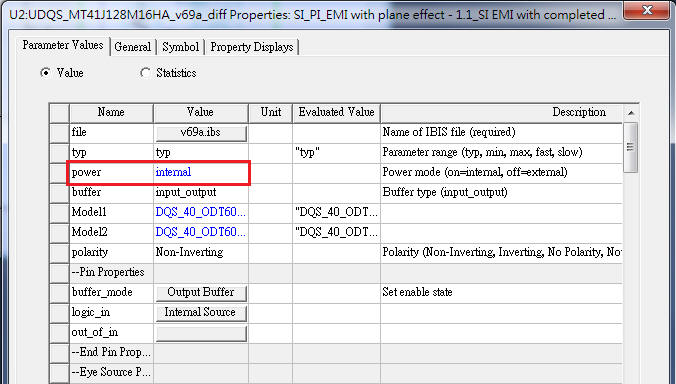

1.1 沒考慮PI (ideal PI effect)的SI、EMI

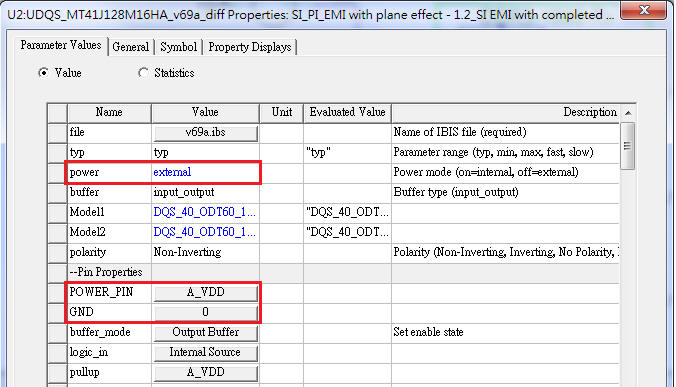

IBIS IO model使用model本身所定義的理想1.5V當電源,而不使用外部實際電路VRM所供給的1.5V

1.2 有考慮PI (real PI effect)的SI、SSN、EMI

IBIS IO model使用外部實際電路VRM透過PCB上的power\ground plane所供給的1.5V當電源

有考慮真實PI的影響下(有SSN與power\ground noise),jitter會略大、眼高會略小,EMI的差異更是明顯。所以SI+PI協同模擬co-simulation是 絕對需要的。

-

參考平面(P\G plane)不完整的SI、SSN、EMI

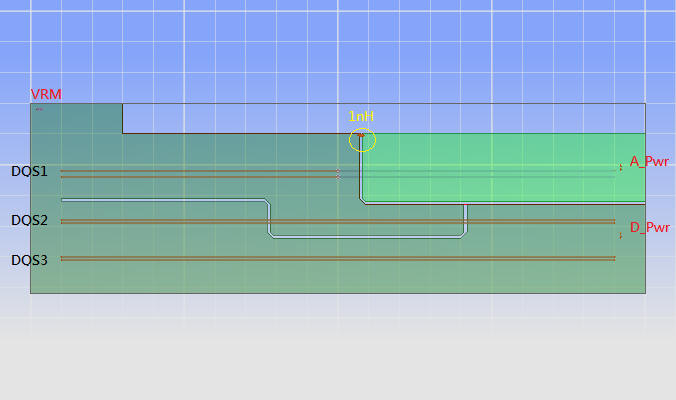

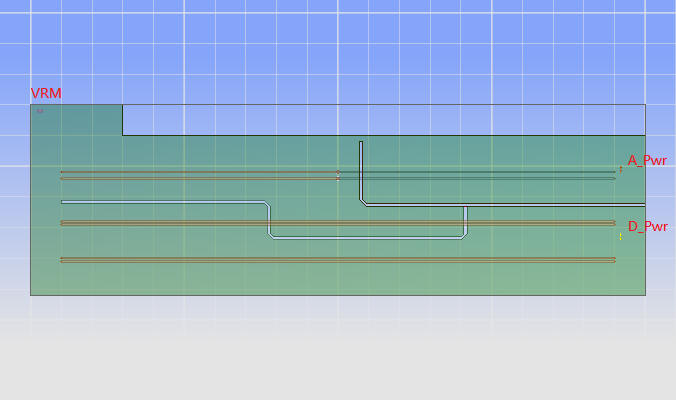

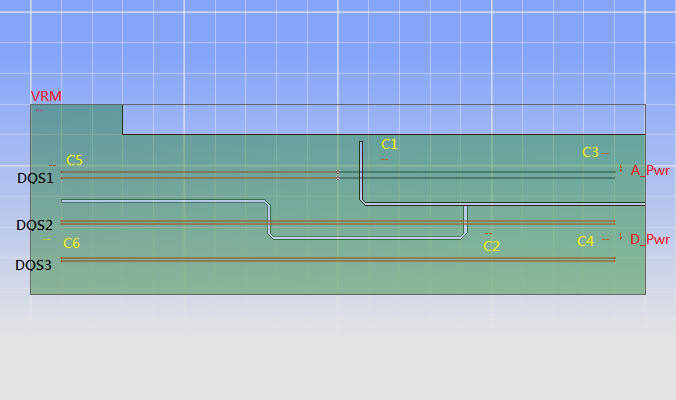

2.1 電源平面與地平面都分割,且透過1nH電感隔離

2.2 電源平面與地平面都分割,但沒有割斷彼此的連接

透過電源與地平面分割,甚至串1nH電感隔離,確實可以看到A_VDD(A_Pwr)與D_VDD(D_Pwr)上的SSN noise差異程度略為拉開了,但用A_VDD的DQS1眼高反而略為變小。另外,被切出來的A_VDD與A_GND區域,因為沒有擺放 任何的去耦電容,反而SSN noise因分割地而變的較D_VDD略差。

串電感或bead隔離兩組電源與地迴路,如果沒有做好各自的PI,分割plane與串電感,可能招致反效果

分割參考平面,若沒處理好,反而會造成SI, EMI變差

-

參考平面(P\G plane)不完整,但經優化後的SI、SSN、EMI

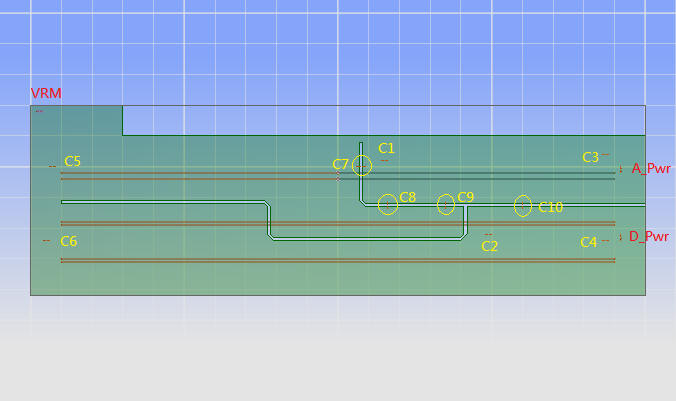

3.1 電源平面與地平面都分割,但沒有割斷彼此連接的情況下,增加decap.電容優化PI

透過參考平面分割,又有去耦電容,確實可以看到A_VDD與D_VDD上的SSN差異程度略為拉開了,且A_VDD的SSN較D_VDD小,即可以避免D_VDD的雜訊干擾到A_VDD。

3.2 電源平面與地平面都分割,但沒有割斷彼此連接的情況下,增加decap.電容優化PI,並在不同地平面間跨高頻電容

3.3 只分割電源平面(串1nH),不分割地平面,增加decap.電容優化PI

與step3.1, 3.2結果相比較,step3.3的EMI最好。這正是我們期望的良好設計所呈現的結果:既要隔離雜訊,又要兼顧SI, EMI

-

問題與討論

4.1 為何DQS3的SI (jitter, 眼高)總是比DQS1差?

Ans:分別比較step1.2, 2.2, 3.3例中的S-parameter,DQS1的loss是比DQS2, DQS3 pair略大的(因為有過孔換層),大約差0.5dB

為何loss較大的傳輸線反而SI相關指標較好?

DQS1的線間距較寬,差動特性阻抗約117 ohm,而DQS2, DQS3的差動特性阻抗約105 ohm。

又Step1.1即使是用ideal PI的模擬條件,也可以看到DQS3的jitter與眼高比DQS1差的現象,所以這不是PI的影響。

若試著在step1.1中,把Rx端的IBIS mode從DQS_40_ODT60改成DQS_40_ODT120,就會看到DQS3的眼高比DQS1好的結果。

做高速訊號模擬,不只需要關心傳輸線本身的SI、整個系統的PI,還有IO的驅動特性跟傳輸線之間的匹配,這些都會影響最後的結果。至於何者是關鍵因素,it is by case.

4.2 為何DQS1有經過一次的過孔換層,但卻不覺得其SI比較差?

Ans:因為DDR的Rx端有開 很強的ODT (On-Die-Terminator)

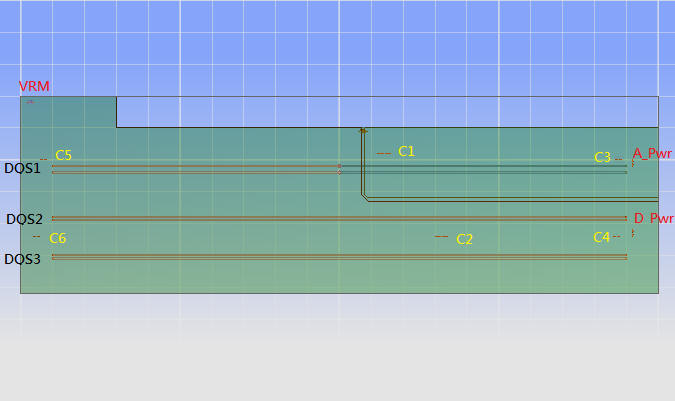

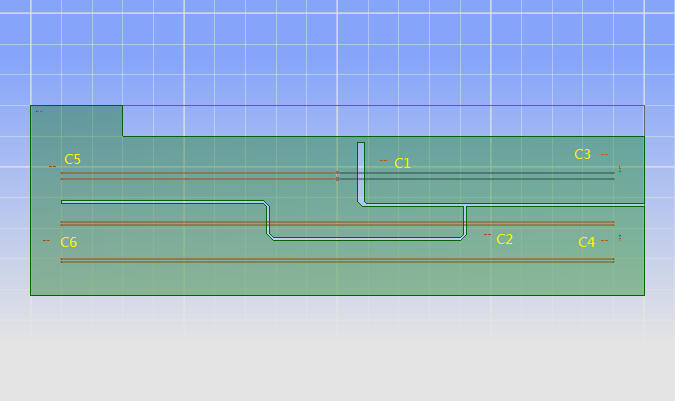

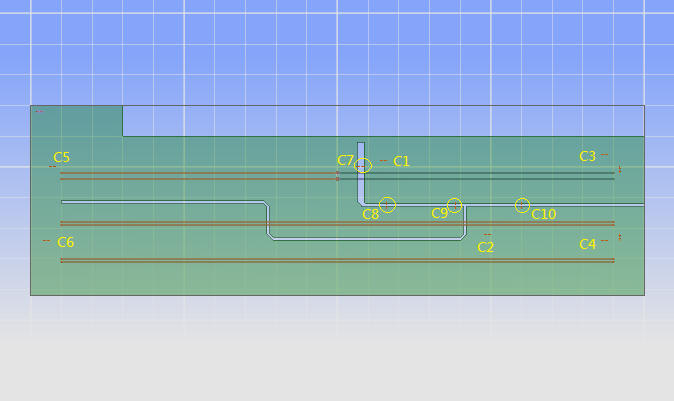

4.3 step3中的C1~C6六顆去耦和電容的擺放位置是如何決定出來的?

Ans:共振區域擺(C1~C2),IO旁邊擺(C3~6)。refer to here

4.4 為何step3.2在分割的plane間跨電容所形成的高頻回流路徑,對SI與EMI沒有明顯的改善?

Ans:這跟slot的寬度、跨接電容的數量、高頻迴流成份的頻段、跨接電容值的選擇都有關 ,又整面plane的PI一般還是會比較好的。

此例在傳輸線下方的slot很細(0.5mm),所以對傳輸線所造成的阻抗不連續只是很短的一段,對SI的影響在有打開ODT的情況下,幾乎看不出來,又因為slot很細(很窄),故slot兩側的coplane本身彼此間就會形成一定寄生耦合電容,故再跨接幾顆0.1uF的電容器件其實沒有明顯的更好。但如果把此例的slot加寬至1.2mm,如下所示,就可以看出EMI有差

4.4.1

4.4.2

-

參考資料