線上影音

Home > ANSYS SIwave教學> PI Simulation

本文使用SIwave 2014針對PI模擬提供基礎學習\練習,以非常簡易的例子,探討以下五點:

-

Resonant mode與Z-profile的相關性

-

Power\Ground Plane的劃分與PCB疊構對Z-profile的影響

-

De-coupling電容的位置對Resonance mode與Z-profile的影響

-

De-coupling電容的ESR、ESL對target impedance設計的重要性

-

PI最佳化設計對EMI的影響

-

比較step1.2與step3例,觀察S21可以了解分割plane對P1, P2兩位置上擺放的IC,所看到彼此間PI關係的影響

-

問題與討論(Q&A)

7.2 在4.2中,如果在更高頻段(~0.5G)要進一步優化PI,該怎麼做?

7.3 若去耦合電容沒放在適當的位置,抑制Z-profile或諧振的效果是否會受到影響?

7.4 step5遠場EMI的結果,為何沒下電容時較低的0.25G頻點在遠場看不到,只有0.56G, 0.99G在遠場可以看到?

-

參考資料

![]()

-

完整的power\ground plane所呈現的諧振模態與Z-profile

1.1 首先以兩層間距3.6mils (Er=4.4)的90mm*80mm的矩形平面為例

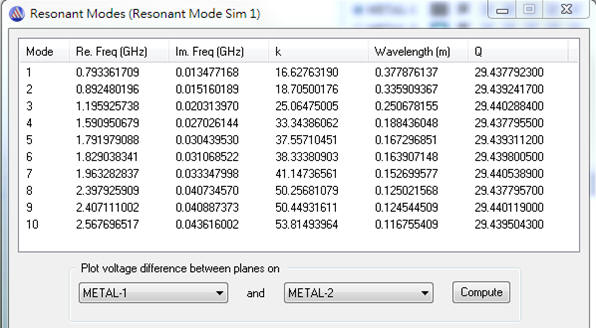

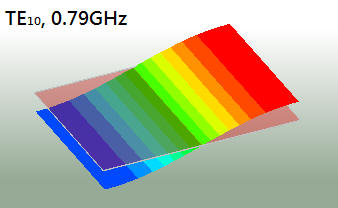

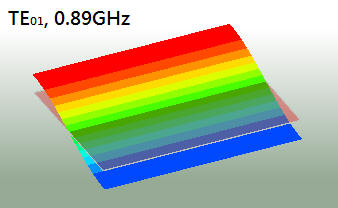

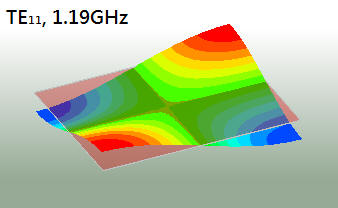

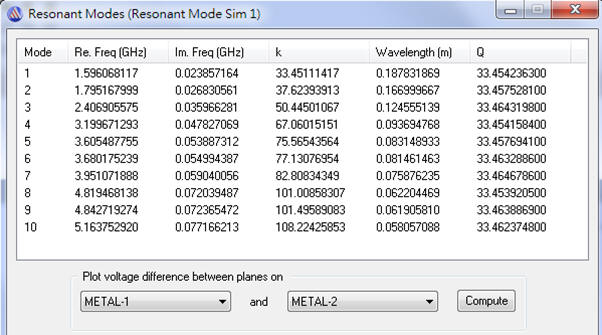

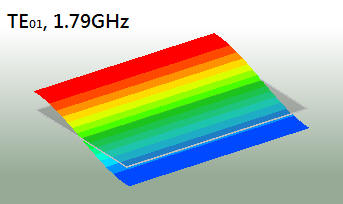

SIwave的Resonant Mode分析,顯示有0.79G, 0.89G, 1.19G, 1.59G...等諧振頻點

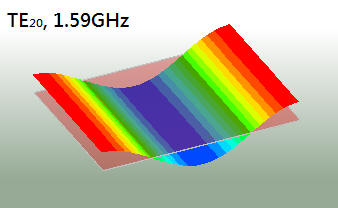

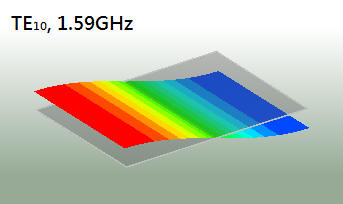

對應諧振模態的頻點與位置如下所示

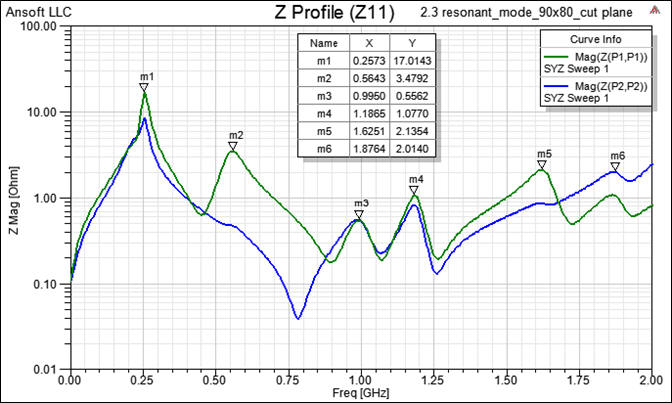

1.2 在版子的左上角放一顆0.1 ohm電阻跨在P\G間當VRM,右下角則放port P1於P\G間,得到的Z-profile如下:可以清楚的看出,在resonant mode所看到的諧振頻點,其在Z profile中也會呈現較高的Z值。

-

完整的power\ground plane,但改變尺寸,對諧振模態與Z-profile的影響

將板子的尺寸各邊縮小一半,改為45mm*40mm的矩形平面 (面積變成1/4)

此時的第一個諧振頻點變成1.596GHz,這個值大約是0.79GHz的兩倍。所以我們可以看出,平面諧振腔所形成的最低諧振頻點,與能量傳遞的最長路徑成反比。

-

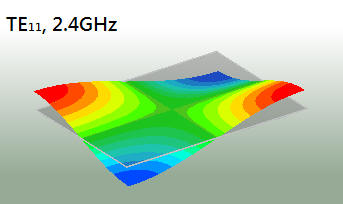

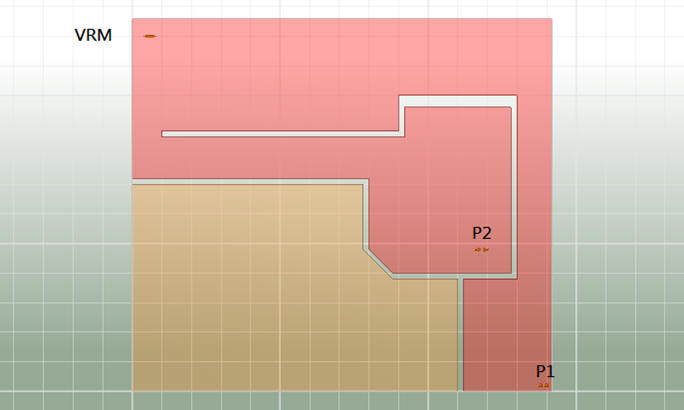

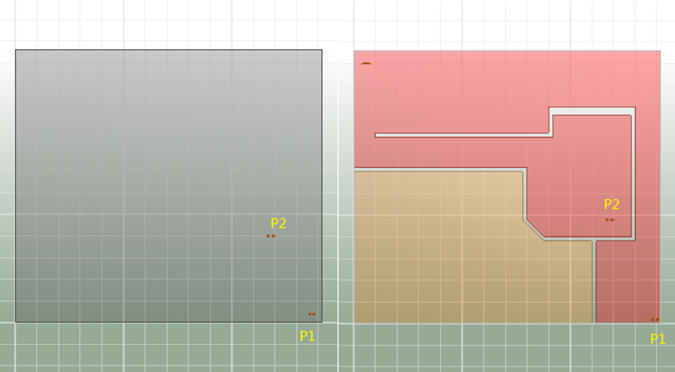

Power plane被切割後的共振頻率與Z-profile

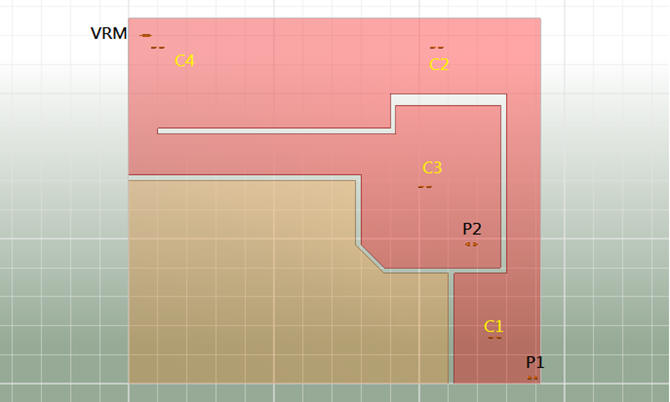

延續90mm*80mm的平面尺寸,但把power plane分割成兩區塊,同樣左上角放0.1 ohm的VRM,右下角放port P1,如下所示

此時port P1, P2看到的Z profile分別如下所示:

小於600MHz的低頻段,有經過平面分割的Z profile明顯較高,又P1的Z profile整體比P2差,尤其在0.56GHz與1.62GHz這兩個頻點上 。

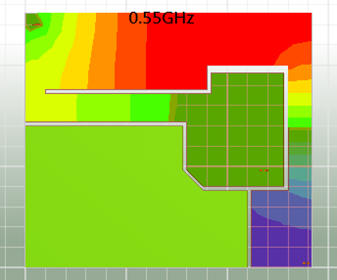

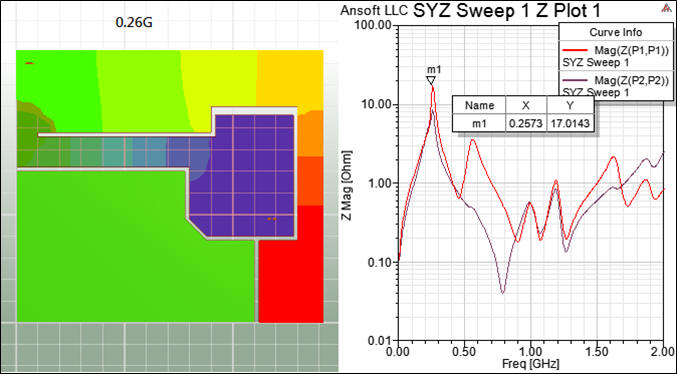

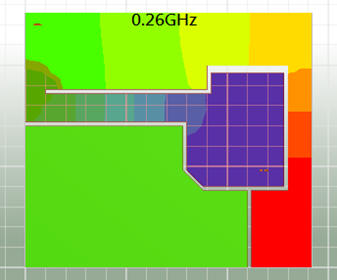

我們從下圖resonant mode來觀察:在P1, P2位置,0.26GHz存在諧振,但在0.55GHz處,只有P1有諧振能量。(綠色表示無諧振能量,紅色與深藍色表示有很強的諧振)

-

下de-coupling電容抑制諧振頻點後的Z-profile

4.1 去耦電容擺放位置

延續step 3,若假設port P1, P2處分別是兩顆不同的IC device放在板子上的位置,以PI設計優化的觀點,放P1處的IC至少要抑制Z profile在0.26G、0.55G的峰值,而放P2處的IC則要抑制Z profile在0.26G的峰值。而3中透過resonant mode所得到的諧振能量較強的區域,就是擺放去耦電容的最佳位置。

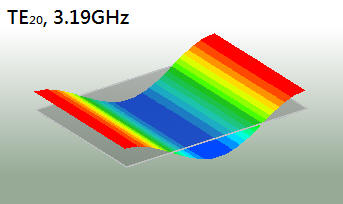

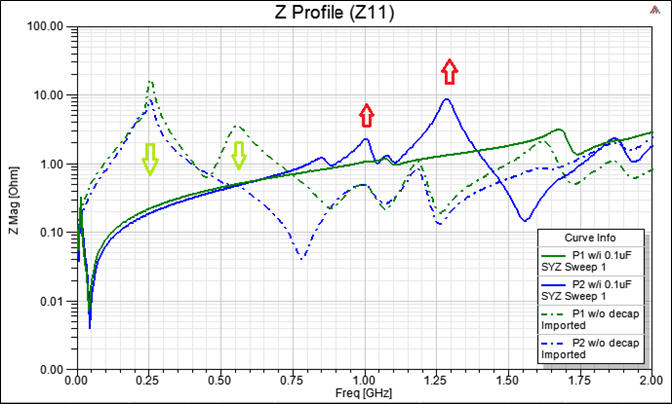

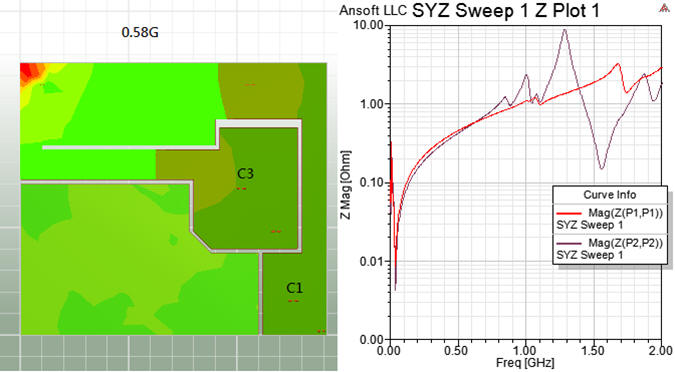

我們先在下圖所示位置上擺上四顆0.1uF電容,然後觀察Z profile與諧振區域的變化

0.58GHz 0.88GHz

0.26G、0.55GHz處的Z值明顯降低許多,但1G與1.3GHz附近的Z卻上升了,主要原因是目前選的0.1uF去耦電容頻寬不夠,只對較低頻段有較好的效果

4.2 去耦電容型號的選擇

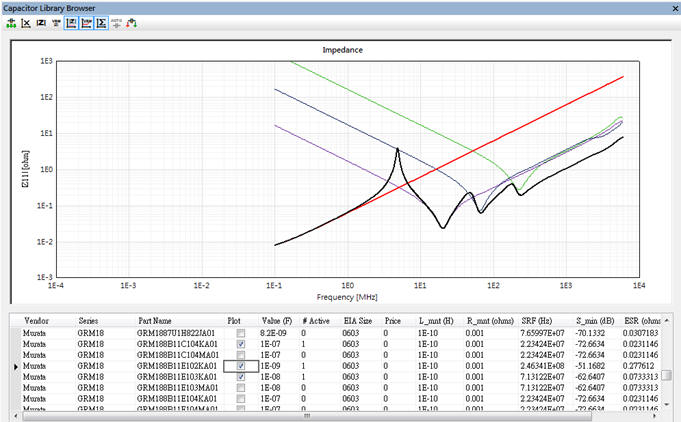

透過SIwave內建的電容資料庫,分別比對一下0.1uF、10nF、1nF電容的Z profile差異

從下圖可以清楚看出,如果我們想要bypass 0.25GHz的能量,選擇1nF比0.1uF好。

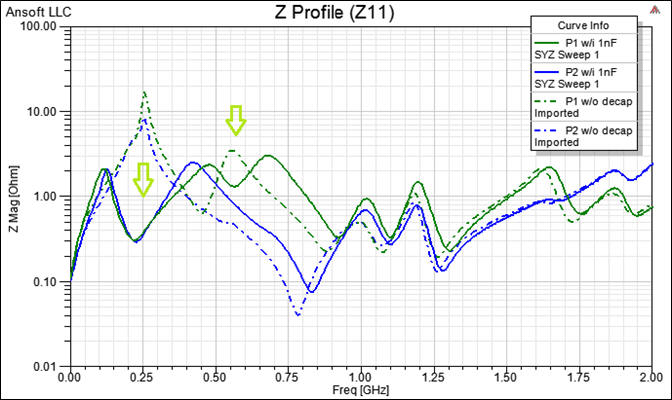

透過SIwave直接以在電容資料庫挑選的Murata 1nF電容(GRM188B11E102KA01)取代原先的0.1uF電容,再做一次分析,得到的Z profile如下:0.25GHz的Z被壓下來,而且1G以上的Z並沒有因此增加太多

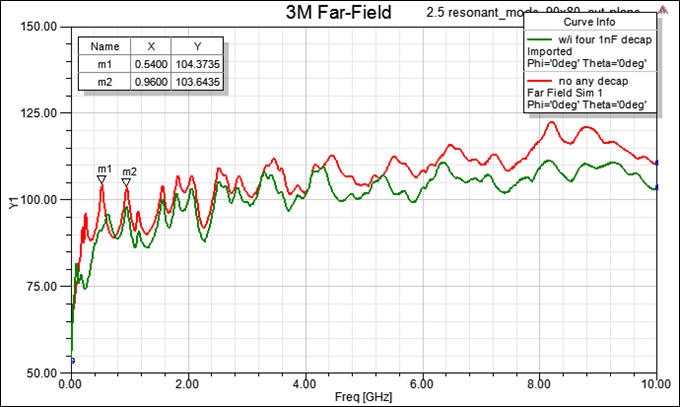

延續前例,把VRM處0.1 ohm電阻換成Frequency Independent Voltage Source (1V),板子沒有去耦電容,與板子放四顆1nF的EMI比較

可看出沒有去耦合電容的例子中,其兩根EMI 0.54G、0.96GHz,與step3內的諧振頻率正好可以對起來

-

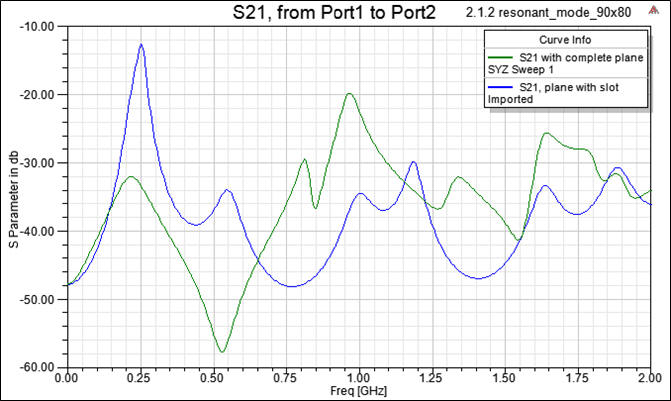

比較step1.2與step3例,觀察S21可以了解分割plane對P1, P2兩位置上擺放的IC,所看到彼此間PI關係的影響

對參考平面分割,增加低頻0.25G處的阻抗,有時我們會利用這樣的特性來隔離P1, P2間的電源雜訊耦合。但參考平面的分割設計,必須考慮其他更高頻訊號成分迴流路徑的連續性,避免影響高速訊號的傳輸,或在板子上產生共模雜訊成份,必須小心。

-

問題與討論(Q&A)

7.1去耦合電容的選擇與擺放,該如何決定?

Ans:如本文3, 4節的說明,去耦電容的最佳位置可以靠觀察resonant mode的諧振區域得知;去耦電容值或型號的選擇,則從欲優化的電源迴路Z profile上,觀察Z存在峰值的頻點,而挑選適當頻寬的去耦電容。

7.2 在4.2中,如果在更高頻段(~0.5G)要進一步優化PI,該怎麼做?

Ans:板級電容因為存在一定的ESR、ESL,所以能有效抑制Z profile的範圍通常在數百MHz內。對於更高頻段的處理,可以考慮封裝內嵌電容、IC內建電容(die level de-cap.)、板級寄生電容(PCB相鄰內層間,power\ground plane夾出的電容,也就是調整疊構或介電質板材)...等措施。

7.3 若去耦合電容沒放在適當的位置,抑制Z-profile或諧振的效果是否會受到影響?

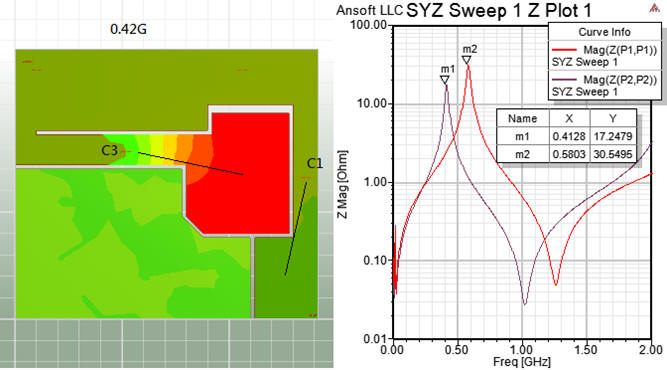

Ans:如果去耦電容沒有擺在合適的位置(離諧振區域較遠),導致去耦半徑涵蓋的範圍內無法有效的抑制諧振與Z profile。若將step4.1的去耦電容C1, C3位置如下移動,板中心的諧振頻點抑制效果明顯受到影響

沒放去耦電容

去耦電容放置於正確位置

去耦電容放置於錯誤位置

7.4 step5遠場EMI的結果,為何沒下電容時較低的0.25G頻點在遠場看不到,只有0.56G, 0.99G在遠場可以看到?

Ans:近場強的能量頻點,不見得遠場一定量的到,尤其是很低頻點的能量。除非板子夠大,有至少1/4波長的輻射路徑讓該低頻的能量可以輻射出來,這樣遠場才有機會量到。這就是為何一般100~200MHz的EMI都是switching noise透過cable帶出來的原因。