線上影音

Home > ANSYS Designer 教學> Overshoot/Undershoot from Reflection

本文最早始於2011,以Designer v6.0示範,後於2023更新,以2023R2 Designer circuit示範。分析傳輸線上高速訊號overshoot/ undershoot的成因(reflection與cross-talk都有貢獻),並觀察分別在訊號發送端(近端)與訊號接收端(遠端)加串聯終端電阻(Rs, damping電阻)的效果。

-

建立電路

-

傳輸線反射

2.1 使用40ohm_1066MHz IBIS模型,microstrip線長5mm

2.2 使用40ohm_2133MHz IBIS模型,microstrip線長5mm

2.3 使用34ohm_2133MHz IBIS模型,microstrip線長5mm

2.4 使用40ohm_2133MHz IBIS模型,microstrip length 10mm

2.5 使用40ohm_2133MHz IBIS模型,microstrip length 10mm with cross-talk

-

消除傳輸線反射所引起的振盪

-

問題與討論

![]()

-

建立電路

-

傳輸線反射

- 消除傳輸線反射所引起的振盪

-

問題與討論

1.1 建立傳輸線,並設定疊構 ![]()

Components tab \ Nexxim Circuit Elements \ Distributed \ Microstrip \ Coupled lines \ MS_MCPL02_Ref

當選定這傳輸線模型拖曳進電路繪圖區時,會自動跳出以下PCB疊構設定視窗:

這樣的疊構條件下,若要試算傳輸線線寬1mm、線距1mm時的特性阻抗多少,可以用Designer內現有的工具

[Circuit] \ [TRL] \ [Microstrip] \ [CPL] (指的是Coupled Line),選上一步驟剛定義的"Substrate",按OK

1.2 匯入IBIS模型 (DQ Buffer) ![]()

Import IBIS Components \ v69a.ibs (Micron DDRIII-1600 IBIS)

1.3 Tx/Rx端設定 ![]()

Tx端設成[Output Buffer],且只需要再設定Unit Interval (UI=1ns)與Bit Pattern,不需要設Tr/Tf,因其由IBIS內所定義的I/O輸出波形特性所決定,而非使用者定義。

過去(~2022R2),Designer circuit匯入IBIS模型後,在Tx Symbol端是可以設定Tr/Tf(Rising/Falling time)的,但這其實很容易造成使用者混淆。因為IBIS"輸出"波形的Tr/Tf應該是由IBIS內定義的waveform特姓所決定,而不是使用者所設定的"輸入"波形Tr/Tf所決定。故過去建議在IBIS Tx Symbol內設的輸入波形Tr/Tf必須小於(一般設1~10ps)實際的輸出波形Tr/Tf(一般是30~100ps)。2023R2之後的新版Designer circuit匯入IBIS模型後,使用者不再需要設定Tr/Tf,這才是較正確的流程 。

Rx端則設成[Input Buffer]

1.4 添加模擬設定 ![]()

1.5 電路連接結果 ![]()

2.1 使用40ohm_1066MHz IBIS模型,microstrip線長5mm ![]()

下圖紅色箭頭所示為訊號傳遞延遲,而訊號上升緣與下降緣的抖動,稍後會證明,來自傳輸阻抗不匹配。

2.2 使用40ohm_2133MHz IBIS模型,microstrip線長5mm ![]()

較高速的IBIS模型其訊號傳遞延遲時間較小,但rising and falling time並沒有變小,why? 參考4.1

2.3 使用34ohm_2133MHz IBIS模型,microstrip線長5mm ![]()

選用Pullup電阻較小的IBIS模型(表示驅動力較強),上升緣與下降緣能拉到的準位較理想。參考4.2

2.4 使用40ohm_2133MHz IBIS模型,microstrip length 10mm ![]()

傳輸線變長2倍,振幅變大,是因為同樣的Tr在較長的線較易進入傳輸線模式(阻抗不匹配引起的反射較強)。

2.5 使用40ohm_2133MHz IBIS模型,microstrip length 10mm with cross-talk ![]()

由於此時特性阻抗不匹配所引起的reflection與差分對cross-talk的影響一起貢獻

當我們觀察單端(single-end)訊號,其確實會因為旁邊另有訊號做動的影響(cross-talk)而波形變差(振盪較大)

但於此同時,如果看的是差分訊號(正負端相減),反而波形是變好的。(因為是差分訊號,看的是相對差異量)

3.1 Rs放Tx端 ![]()

3.2 Rs放Rx端 ![]()

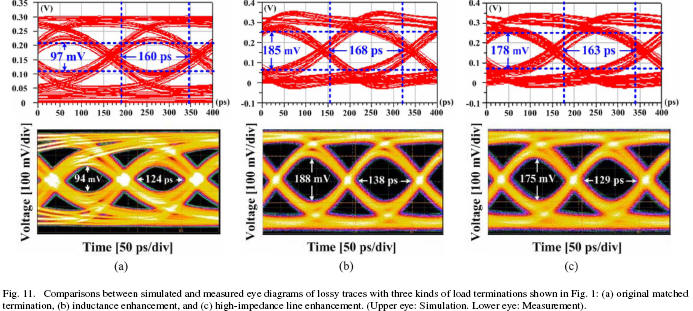

![]() Rs不管是放哪一端都可以改善overshoot/undershoot,但效果是不同的。

Rs不管是放哪一端都可以改善overshoot/undershoot,但效果是不同的。

有人覺得放靠近transceiver (drive)端較好(source termination),因為其根本上直接抑制了引起反射的訊號高頻成份;但筆者是認為,Rs只當damping電阻,而是修正阻抗不匹配,放在引起反射的一端(可能是source termination或是load termination),以上圖為例就是放在high-impedance的input buffer端,這樣既可消除overshoot/undershoot,又不會改變rising time、falling time太多。

![]() 常見的做法是series termination放drive端(尤其當想要抑制EMI時),parallel termination放receiver端;而DDR的ODT (On-Die Terminator),是做在receiver端。

常見的做法是series termination放drive端(尤其當想要抑制EMI時),parallel termination放receiver端;而DDR的ODT (On-Die Terminator),是做在receiver端。

4.1 Compare IBIS of

DQ_40_1066 and DQ_40_2133 ![]()

觀察上圖IBIS內所定義的rising time特性,較高速的DQ pin,開始將訊號拉起來的時間會較早,但rising time並沒有比較小,這與我們在2.1, 2.2所看到的結果相互呼應

4.2 Compare IBIS of

DQ_34_1066 and DQ_40_2133 ![]()

觀察上圖IBIS內所定義的Pullup特性,較小Pullup電阻者,有較大drive電流,這與我們在2.2, 2.3所看到的結果(overdriven)相互呼應

參考台大電機吳瑞北老師的課程如下:

5.1 Ringing is often due to multiple reflections between impedances discontinuities at the ends.

5.2 Effects of rise time -- overdriven case

5.3 Effects of rise time -- underdriven case