-

Creating New Free-Form Schematics

-

Adding

Transmission Lines

-

Adding

ICs

-

Adding

Passive Components and Power Supplies

-

Editing

Power-Supply Voltages

-

Adding

Vias

-

Setting

Up and Running Simulations

-

Viewing

Simulation Results

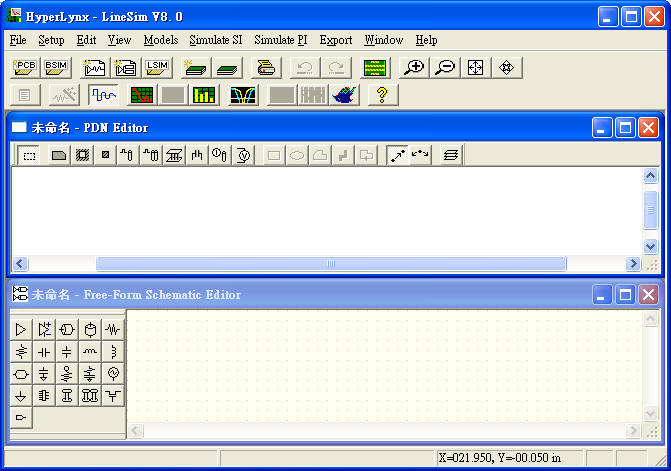

Free-Form Schematic Editor一開始是個空白的編輯區,由使用者放入電路模型符號(傳輸線、貫孔...等)來做模擬。

-

Creating New Free-Form Schematics

File \ New

Free-Form Schematic或按New LineSim Free-Form Schematic button

,會出現以下的[PDN

Editor]與[Schematic Editor]視窗 ,會出現以下的[PDN

Editor]與[Schematic Editor]視窗

-

Adding

Transmission Lines

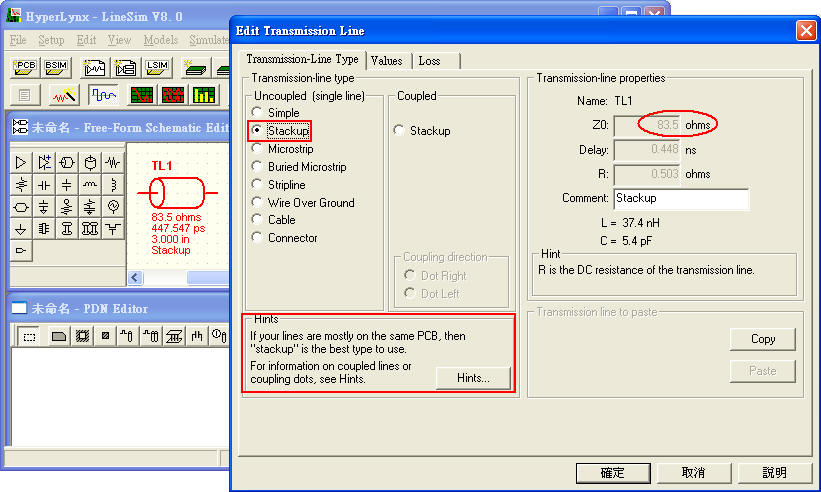

2.1 按Add transmission line to schematic

or

or

icon,於工作區中擺放傳輸線模型,然後滑鼠左鍵雙擊該傳輸線符號,即可開啟傳輸線設定視窗

icon,於工作區中擺放傳輸線模型,然後滑鼠左鍵雙擊該傳輸線符號,即可開啟傳輸線設定視窗

2.2

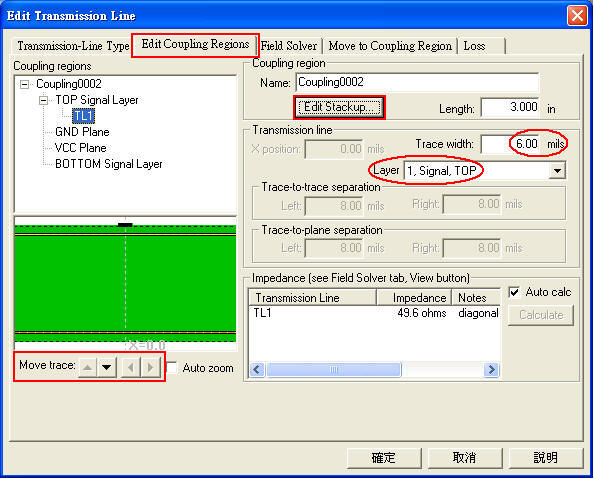

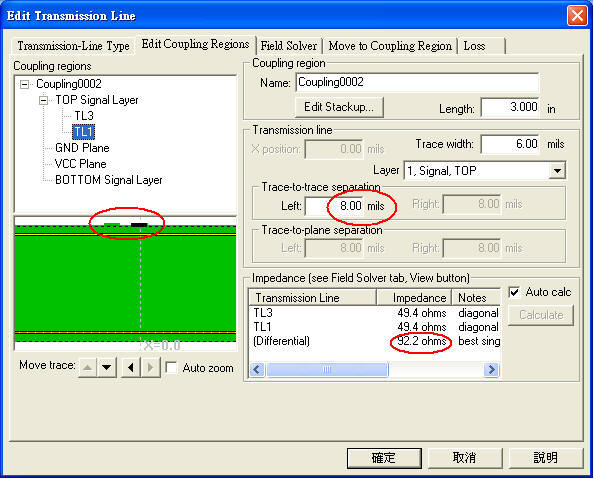

這裡有很多東西大家可以好好試一下,首先傳輸線特性阻抗Zo=83.5歐姆,這值是由線寬與堆疊決定的,所以切到右邊Coupled

Type的[Stackup],然後選擇[Edit Coupling Regions]標籤頁,確定線寬,按[Edit

Stackup]按鈕,我們要調整堆疊設定讓microstrip

line特性阻抗接近50歐姆。

從上圖可以看出,傳輸線默認是走在top layer;User可以透過Move trace的上下按鍵,移動trace所在的layer。

從上圖可以看出,傳輸線默認是走在top layer;User可以透過Move trace的上下按鍵,移動trace所在的layer。

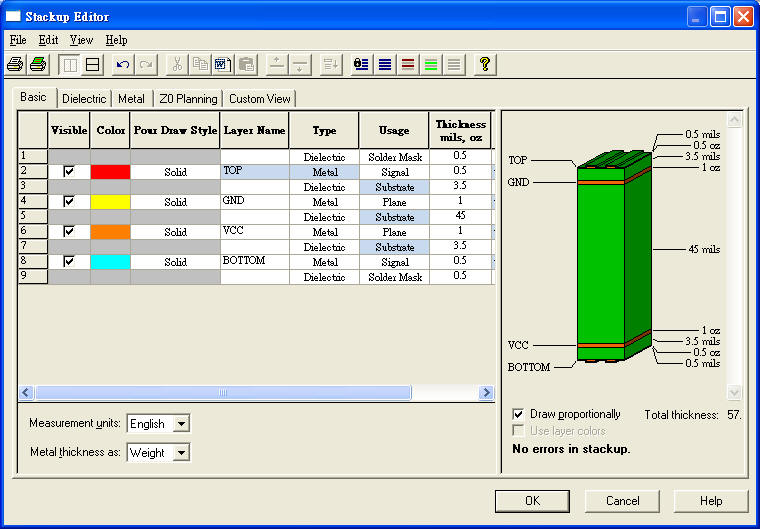

將原本六層板改成如下的四層板PCB堆疊,並且讓GND plane在Top

layer的相鄰層(因為我們默認signals是在top layer)

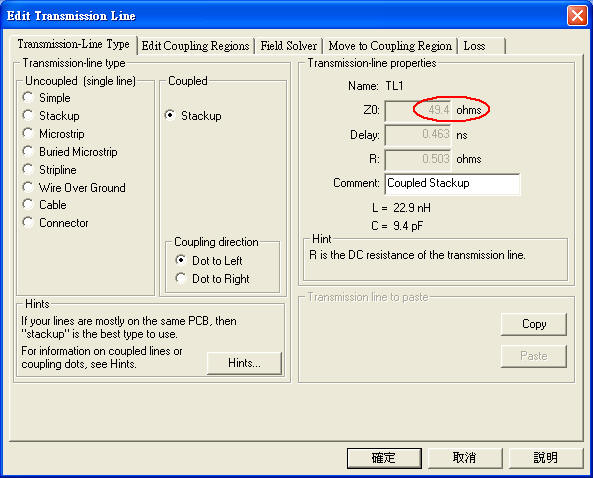

2.3

再切回Transmission-Line Type觀察,特性阻抗變成49.4歐姆,這正是我們要的。

2.4

同樣的傳輸線我們再copy一段,並且選擇[Coupling

direction],就會看到兩條傳輸線間有一條淺綠色虛線連接,表示這兩段線彼此有耦合關係

傳輸線符號上綠色的點(coupling dot),其設置位置必須注意,相鄰兩線的近端,同時擺coupling

dot才對,不可一個擺近端一個擺遠端

傳輸線符號上綠色的點(coupling dot),其設置位置必須注意,相鄰兩線的近端,同時擺coupling

dot才對,不可一個擺近端一個擺遠端

若兩條傳輸線間原本是uncoupled,可以先以Ctrl+滑鼠左鍵選定,再按滑鼠右鍵選擇[Couple]。

若兩條傳輸線間原本是uncoupled,可以先以Ctrl+滑鼠左鍵選定,再按滑鼠右鍵選擇[Couple]。

此時若我們再打開[Edit Transmission Line]視窗,在[Edit

Coupling Regions]標籤頁內,就可以看到兩線間的space與差模特性阻抗

2.5

進一步再切到[Field Solver],即可看到表面電場與磁場分佈,這功能太帥了

3.5mils的microstrip堆疊高,即使有8mils的線距(space),線間的電力線與磁力線還是有交互影響的(coupling

effect)

3.5mils的microstrip堆疊高,即使有8mils的線距(space),線間的電力線與磁力線還是有交互影響的(coupling

effect)

-

Adding

ICs

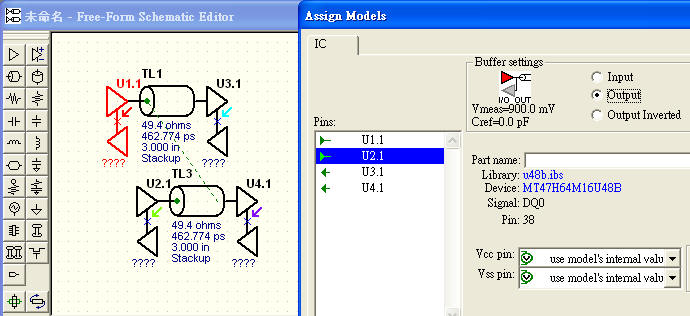

按Add IC to schematic

or Add differential IC to schematic

or Add differential IC to schematic

,於工作區中擺放IO

driver model (IC model),同樣以滑鼠左鍵雙擊該IC符號,即可開啟IC設定視窗,整個設定方法跟SI

BoardSim該文sec.6所介紹的方法一樣。 ,於工作區中擺放IO

driver model (IC model),同樣以滑鼠左鍵雙擊該IC符號,即可開啟IC設定視窗,整個設定方法跟SI

BoardSim該文sec.6所介紹的方法一樣。

設定過程

設定完成後,IC符號會根據是Input、Output而變化,線路符號間也會開始連接

-

Adding

Passive Components and Power Supplies

4.1 Add

passive component

可以添加R、L、C、Ferrite Bead、pull-up\pull-down resistor、RC terminator

to ground...。

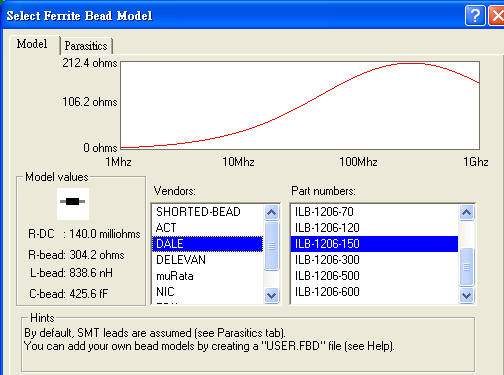

HyperLynx所提供的Ferrite Bead元件很有意思,可以自己設定特性曲線,玩過EMC的工程師應該就會對這功能有感覺

HyperLynx所提供的Ferrite Bead元件很有意思,可以自己設定特性曲線,玩過EMC的工程師應該就會對這功能有感覺

4.2 Add

power supplies

只能把power supplies連接到passive component,也可以設定被動元件要pull-up到哪一個power

net。

若要設定IC model的power supplies,則要在step 3內做(setting VCC pin)。

若要設定IC model的power supplies,則要在step 3內做(setting VCC pin)。

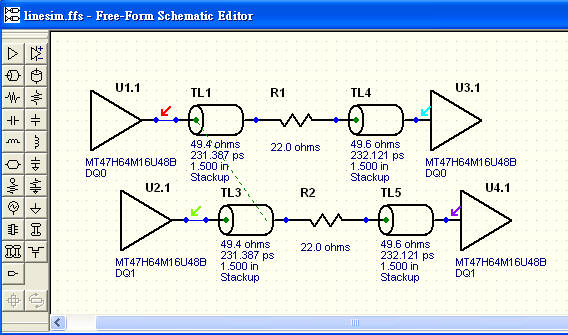

假設我們最後的線路連接方式如下

-

Editing

Power-Supply Voltages

因為IC已經套用IBIS model內所定義的理想電源1.8V,所以這步驟不用再多做什麼設定

-

Adding

Vias

在線路中加via模型,有以下幾個步驟 (只有Free-Form Schematic

Editor有Via model,Cell-Based Schematic Editor沒有Via model )

6.1

Edit

Stackup button

(the same as step 2.2)

(the same as step 2.2)

6.2

Setup menu

\ Padstacks

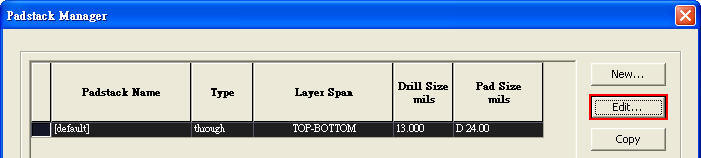

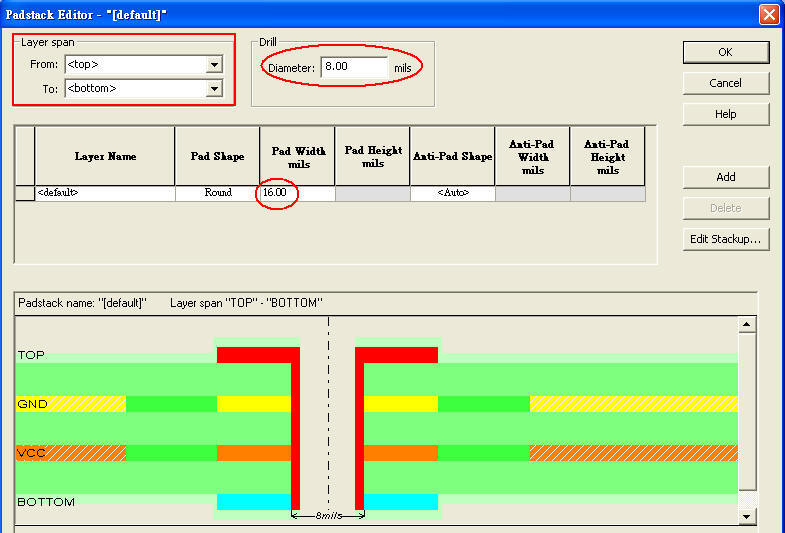

設定via的孔徑大小、pad大小、貫穿層(從哪一層穿到哪一層)。

下圖我們將原本孔徑(drill)從13mils改成8mils,pad size也從24mils改成16mils

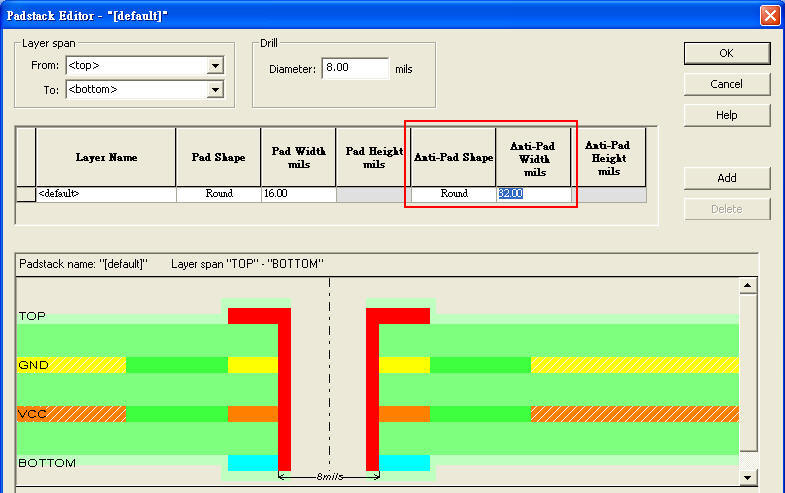

anti-pad width原本不能設定,只要把[Anti-Pad Shape]設定一個形狀,就可以設anti-pad

width

依以上幾個步驟,我們可以設定幾組不同孔徑大小或不同換層方式的via model供後面模擬時套用

6.3

HyperLynx的via只能與Transmission line

model連接,不能直接與被動元件或IC相接,如下圖所示(TL6走線要改成在bottom layer)

-

Setting

Up and Running Simulations

設定方法跟SI

BoardSim該文sec.8所介紹的方法一樣。

-

Viewing

Simulation Results

設定方法跟SI

BoardSim該文sec.9所介紹的方法一樣。

8.1

若DDRII-800走線總長3500mils,不開ODT眼圖有點睜不開,如下圖所示

8.2

若把DDRII-800走線總長控制在1000mils以內,不開ODT眼圖如下所示

再一次說明,盡量把總線長縮短的重要。

再一次說明,盡量把總線長縮短的重要。

每個訊號眼圖疊起來,"自己的"時間差(jitter)就蠻大的。

這是因為模擬的test pattern是用(PRBS),若以這樣的source模擬,會依前幾個bit是否有轉態,影響到傳輸線當下訊號要轉態的瞬間,需要改變傳輸線C極性的難度,即影響訊號edge傳遞速度,這效應

稱為ISI。讀者可以比較source pattern分別使用PRBS與CLK的眼圖差異,後者眼圖會細很多。 這是因為模擬的test pattern是用(PRBS),若以這樣的source模擬,會依前幾個bit是否有轉態,影響到傳輸線當下訊號要轉態的瞬間,需要改變傳輸線C極性的難度,即影響訊號edge傳遞速度,這效應

稱為ISI。讀者可以比較source pattern分別使用PRBS與CLK的眼圖差異,後者眼圖會細很多。

|