## Welcome to

## **25**<sup>TH</sup>ANNIVERSARY **DESIGN CON® 2020** WHERE THE CHIP MEETS THE BOARD

Expo

Conference

January 28 - 30, 2020

January 29 - 30, 2020

Santa Clara Convention Center

#DesignCon

## Hybrid PEX Flow for 2.5D Si-Interposer SerDes Signal Channel Model Extraction by Considering High Loss Silicon Substrate Effects

Jun So Pak, Samsung Electronics Co., Ltd. junso.pak@samsung.com

Bo Pu, Gibak Han, Wonyoung Kong, Ingun(Lars) Jung, Sungwook Moon, Samsung Electronics Co., Ltd. {bob.pu, gibak.han, wy0217.kong, ingun.jung, sw2013.moon}@samsung.com

#DesignCon

## Contents

#### **Background & Motivation**

- HPC (high performance computing) Chip on Si-Interposer due to HBM (high bandwidth memory)

- What is the Critical Component in SerDes Si-Interposer Channel? 0

#### TSV

- TSV(through silicon via) with MIS (metal-insulator-semiconductor) or MIM (metal-insulator-metal) Structure 0

- Freq. Dependent IL (insertion loss) Characteristics 0

- Limitations of Conventional PEX Flow to Si-Interposer SerDes Channel Model Extraction 0

#### Proposed Hybrid PEX Flow for Si-Interposer SerDes Channel

- Key Difference referring to Silicon Substrate between Conventional & Proposed Hybrid PEX Flow 0

- What makes Proposed Hybrid PEX Flow Important for Si-Interposer SerDes Channel? 0

- Proposed Hybrid PEX Flow

- Summary

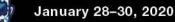

## **HPC Chip on Si-Interposer**

- SerDes Si-Interposer Channel Configuration for External Connection

- [Micro-bump ~ BEOL (back-end of line) ~ TSV ~ C4-bump] ~ PKG ~ BGA ~ Board

- Well-known Critical TSV to SI Performance of High-speed Si-Interposer Channel (PCIe Gen4/5, SerDes 56G/112G)

- How about **BEOL & C4-bump** Impact on the HSI Channel?

- How to Extract High-Freq. Resistances & Capacitances of BEOL & C4-bump ?

### How to Extract High-Freq. Model Parameters of BEOL & c4-bump?

- Model Parameters •

- Micro-bump Pad

- Resistance / Capacitance / Inductance?

- Conventional PEX Flow can cover? or 3D Full-wave Tool?

- BEOL & Silicon-Substrate

- Resistance / Capacitance / Inductance? ٠

- Conventional PEX Flow can cover? or 3D Full-wave Tool?

- TSV & Silicon-Substrate

- Resistance / Capacitance / Inductance by Well-known 3D Full-wave Tool ٠

- Conventional PEX Flow can cover?

- C4-bump Pad & Silicon-Substrate

- Resistance / Capacitance / Inductance by Well-known 3D Full-wave Tool ٠

- How about Silicon-Substrate Effect on BEOL?

- Same BEOL Environment as TSVs

- 3D Full-wave Tool can cover? ٠

- **Reasonable Flow considering Design Complexity?** ٠

#### **Remind TSV Model Parameters**

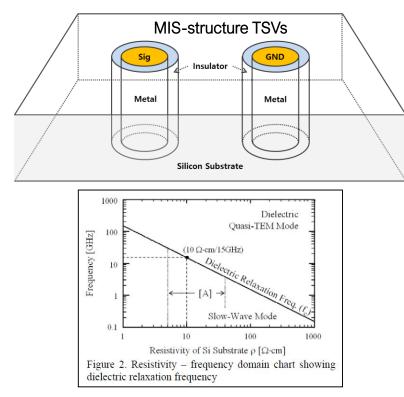

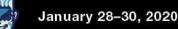

[1] J. S. Pak, et al.," Slow wave and dielectric quasi-TEM modes of Metal-Insulator-Semiconductor (MIS) structure Through Silicon Via (TSV) in signal propagation and power delivery in 3D chip package," in 2010 ECTC, Las Vegas, NV, USA, 2010.

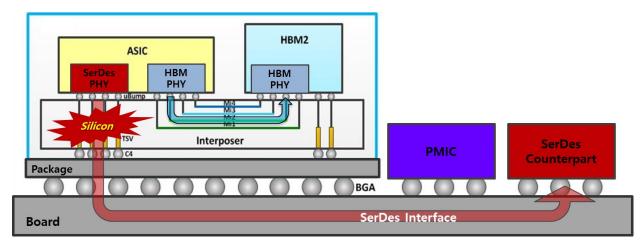

- TSV (Through Silicon Via)

- MIS-structure

- Metal-Insulator-Semiconductor

- Metal (TSV barrel) surrounded by Insulator (Silicon Oxide) in Semiconductor (Silicon Substrate)

- TSV Electrical Characteristics following Slow-Wave Mode

- Large Capacitance & Low Inductance due to Silicon Substrate

- Model Parameters

- Resistance: TSV itself, Silicon Substrate (Small Conductivity)

- Capacitance: MIS Capacitance between TSV & Silicon Substrate,

#### Silicon Substrate Capacitance between Two TSVs

- Inductance: Two Signal & GND TSVs' Loop Inductance

- Slow-Wave Mode @ TSVs

- Coming from Shunt LARGE Resistance & SMALL Capacitance of Silicon Substrate between Two TSVs

- Due to Small Conductivity Silicon Substrate

- Resulting in Freq. Dependent Electrical Characteristics

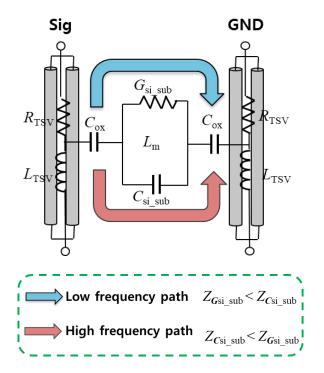

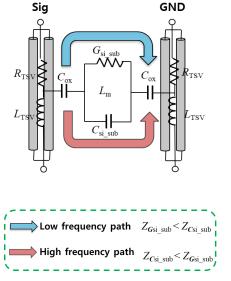

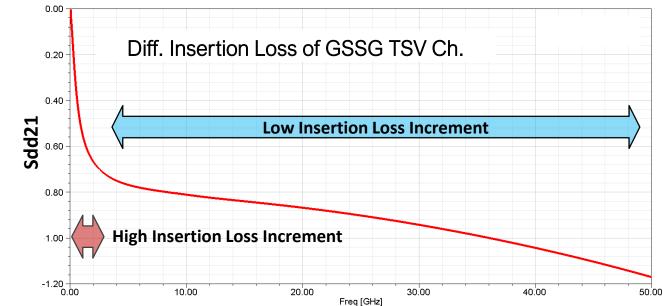

### Freq. Dependent Electrical Characteristics of TSV Model

- TSV Model

- Key TSV Model Parameters for Signal Insertion Loss

- Parameters of Signal Path from Signal TSV to GND TSV

- Signal TSV MIS Cap;  $C_{ox}$  → Silicon Substrate Conductance;  $G_{si\_sub}$ & Capacitance;  $C_{si\_sub}$  → GND TSV MIS Cap;  $C_{ox}$

- Low Impedance Path between Signal & Ground TSVs

- @ Low Freq. ( )

- $Z_{Sig_{GND}_{low_{freq}}} \sim 1/(j\pi C_{ox})$

- High Insertion Loss Increment ( $C_{ox} > 10xC_{si_sub}$ )

- @ High Freq. ( )

- $z_{Gsi_{sub}} > z_{Csi_{sub}}$

- $Z_{Sig\_GND\_high\_freq} \sim 1/(j\pi C_{si\_sub})$

- Low Insertion Loss Increment

### Freq. Dependent Electrical Characteristics of TSV Model

January 28-30, 2020

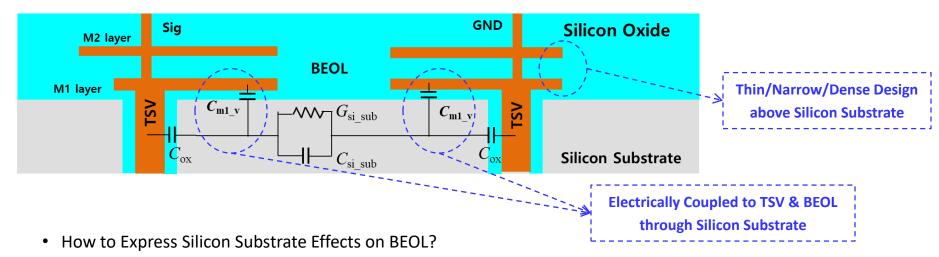

#### How about BEOL & C4-bump Pad?

- **BEOL & C4-bump Pad** ٠

- Electrically Coupled to Silicon Substrate through Silicon Oxide = Same as TSV \_

- C4-bump Pad: Large Dimension & Model Extraction with TSV by 3D Full-wave Tool

- **BEOL**: Thin Metal Layer & Narrow Strap-type Power/GND Design & High Density/Complex Design  $\rightarrow$  What Tool? \_

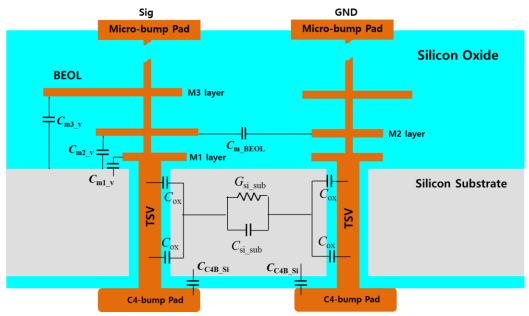

## **BEOL coupled to TSV & BEOL through Silicon Substrate**

- Conventional PEX Flow

- Can extract C<sub>mN v</sub> (BEOL MIS Cap) values

- BUT, those extracted C<sub>mN v</sub> are combined into Single Node → NOT Connected to each related Silicon Substrate Gsi\_sub & Csi\_sub!!!

- Impossible to express High Freq. Characteristics

- 3D Full-wave Tool

- Can express partial design  $\rightarrow$  NOT extract All C<sub>mN\_v</sub> (BEOL MIS Cap) values

- Impossible to apply real Si-Interposer Design with Reasonable Reiew TAT (turn-around time)

### Need BEOL Modeling Flow during TSV Modeling → Hybrid PEX Flow

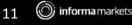

- **Proposed Hybrid PEX Flow** instead of **Electrically Isolating** Conventional PEX Flow for BEOL & TSV

- Adopting Conventional PEX Flow

- Apply R-Only PEX Option to Si-Interposer Design

- Extract Signal/Power/GND Partial Resistances of Micro-bump Pad, BEOL (Strap/Via), & C4-bump Pad

- Assign short connection path to TSV between M1 Layer to C4-bump Pad

- **Convert** Partial Resistances to S-parameter by assigning Ports to Signal-GND & Power-GND at Micro-bump & C4-bump Sides separately

- Enabling 3D Full-wave Tool to deal Interactions among BEOL, Silicon Substrate, & TSVs

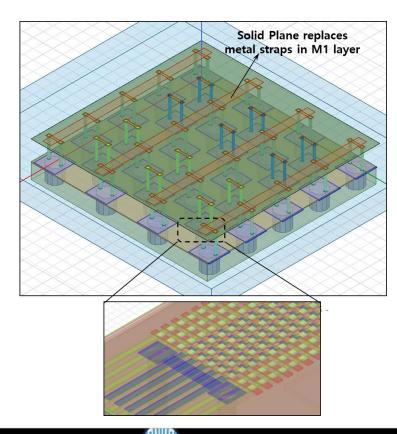

- Convert M1 Layer Strap Design to Solid Design for letting 3D Full-wave Tool solve BEOL

- Consider Multi-layer Strap Design (M1, M2,,,,MN) MIS Cap almost SAME as M1 Layer Solid Design MIS Cap

- Consider Simple Vertical Structure of Si-Interposer SerDes Channel for minimizing Loading Capacitance

While Complex Power/GND Design

Apply Micro-bump & C4-bump Structures for including their Parameters & minimizing Port Parasitic Cap

### **Proposed Hybrid PEX Flow Verification**

12 🔘

### M1 Layer Solid MIS Cap vs Multi-layer Strap MIS Cap

|                                   | Cm_v<br>(Verical Cap) | Cm_s<br>(Sidewall Cap) | Total Cap              |

|-----------------------------------|-----------------------|------------------------|------------------------|

| Strap Design<br>(BEOL All Layers) | 82%                   | 18%                    | 100%                   |

| Proposed Solid Design<br>(M1)     | 102%                  | 2%                     | 104%<br>(Conservative) |

| Difference                        | +20%                  | -16%                   | +4%<br>(Reasonable)    |

- Comparison MIS Cap of Proposed Solid M1 Design & Original Strap Multi-layer Design

- Proposed M1 Layer Solid Converting Method well cover Original Design MIS Cap Value

- Show 4% Conservative & Reasonable Result

- Use Simple Capacitance Calculation Equation such as Cap =  $\varepsilon x$  [Overlap Area] / [Oxide Thickness]

- NOT consider Signal-GND capacitance because of Long Distance & Thin BEOL Area

- 3D Full-wave Tool

- \* Can express partial design  $\rightarrow$  NOT extract All C<sub>mN\_v</sub> (BEOL MIS Cap) values

- Impossible to apply real Si-Interposer Design with Reasonable Review TAT (turn-around time)

### **Proposed M1 Layer Solid Design**

- Proposed M1 Layer Solid Design

- Let Larger Design Area Analysis Possible

- C4-bump #: 8 → 32

- Power Net Included

- Small Design Review TAT  $\rightarrow$  Good to Design Optimization

- Weak Point

- Many Manual Jobs  $\rightarrow$  High Human Error Risk

- Long Initial Design Setting

- Still, Partial Design Analysis

- NOT YET, Measurement Correlation

January 28-30, 2020

14 O informamarkets

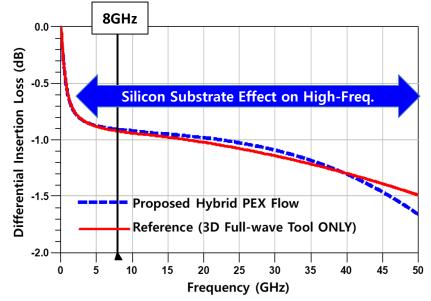

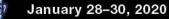

### Comparison Sdd21 of Hybrid PEX Flow vs 3D Full-wave Tool Only

- Hybrid PEX Flow

- Well Agreement with 3D Full-wave Tool Result

- Hybrid PEX Flow shows the Discrepancy owing to Over-estimated Inductance Value from Conventional On-chip PEX Tool

- NOT Apply Inductance option  $\rightarrow$  MUST Consider Mutual Inductance

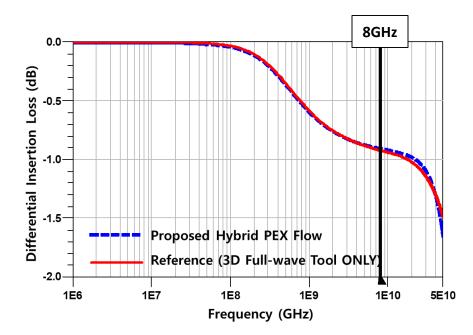

### **Comparison Sdd21 in Log-scaled X-axis**

• Hybrid PEX Flow

- Well Agreement in DC Level

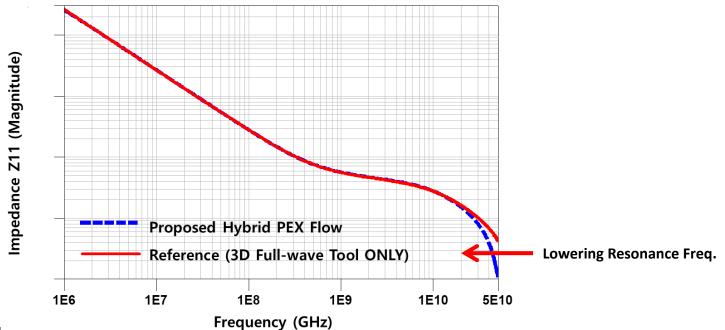

### **Comparison Z11**

- Hybrid PEX Flow

- Well Agreement in Capacitance & Resistance

- But, Over-estimated Inductance lowers Resonance Freq.

### Measurement vs Proposed Hybrid PEX (TSV+PKG)

- Hybrid PEX Flow

- Interposer: BEOL + TSV + C4-bump  $\rightarrow$  Differences from the previous Results come from Different BEOL Design. (Smaller Cap)

- Overall Differences between Measurements & Hybrid PEX Simulation mostly come from PKG modeling

- Need more Analysis for Simulation: Probing Pad Effects, Insulator Thickness, & Silicon Substrate Conductivity

## Summary

#### @ Background & Motivation

- o HPC Chips on Si-Interposer need SerDes Channel including BEOL, TSV, & C4-bump Pad

- Their Larger Capacitances can be up to 1 pF & Critical Component to SerDes Si-Interposer Channel

#### • @ Remind TSV Model Parameters

- o BEOL, TSV, & C4-bump Pad have MIS (metal-insulator-semiconductor) Structure

- o Their IL shows Freq. Dependent Characteristics due to Silicon Substrate and Consequent MIS Cap

- o Important to SerDes Cannel because SerDes Nyquist Freq. over 10GHz

- o Conventional On-chip PEX Flow gives Wrong way to Si-Interposer SerDes Channel Design

#### @ Proposed Hybrid PEX Flow for Si-Interposer SerDes Channel

- o For SerDes Si-Interposer Channel, High Freq. Electrical Performance must be well estimated

- o Adopt Conventional On-chip PEX Flow for modeling Resistance only of BEOL & C4bump Pad

- Adopt 3D Full-wave Tool for modeling Silicon Substrate on BEOL, TSV, & C4-Bump Pad by converting Strap-type M1 Layer Design to Solid-type M1 Layer Design

#### Proposed Hybrid PEX Flow shows Reasonable Results

# Thank you!

## **QUESTIONS?**