## The Case of the Closing Eyes:

### Is PAM the Answer? Is NRZ dead?

### Agenda

- Introductions

- Overview

- Design Engineering Perspective

- Test & Measurement Perspective

- Summary

- Audience Discussion

### **Panelists**

#### **Cathy Liu**

Director, Broadcom Ltd

#### **Ransom Stephens, PhD**

Principal, Ransom's Notes

#### Pavel Zivny Domain Expert, Tektronix, Inc.

Mike Li, PhD Fellow, Intel Corporation

#### **Greg LeCheminant**

Sr. Applications Engineer, Keysight Technology

**Mark Marlett**

Principal Engineer, Inphi Corporation

#### **Marty Miller**

Chief Scientist, Teledyne-LeCroy Corporate

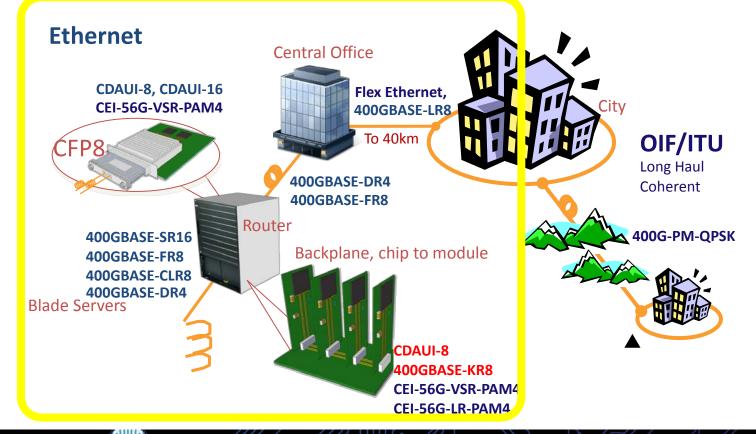

### PAM4 Impact on Communications Network

UBM

| Distance                                        | Standard            | Modulation/signaling | e.g.                                      |

|-------------------------------------------------|---------------------|----------------------|-------------------------------------------|

| X,000 km                                        | OIF, OTN, ITU       | Complex optical      | DP-QPSK                                   |

| 100M (MMF)                                      | Ethernet            | PAM2 at 25 GBd       | 400GBASE-SR16                             |

| 10 km                                           | Ethernet            | PAM4 at 25 GBd       | 400GBASE-LR8                              |

| 2 km                                            | Ethernet            | PAM4 at 25 GBd       | 400GBASE-FR8                              |

| 500 m                                           | Ethernet            | PAM4 at 56 GBd       | 400GBASE-DR4                              |

| Backplane < 1m                                  | OIF CEI             | PAM4 at 25 GBd       | CEI LR                                    |

| Interconnect<br>module to chip,<br>chip to chip | Ethernet<br>OIF CEI | NRZ<br>PAM4          | CDAUI-16,<br>CDAUI-8<br>CAUI-4<br>CEI VSR |

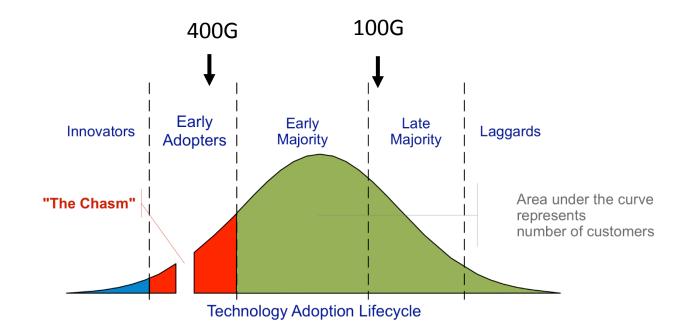

## Is NRZ Dead?

Ransom Stephens, PhD, Ransom's Notes

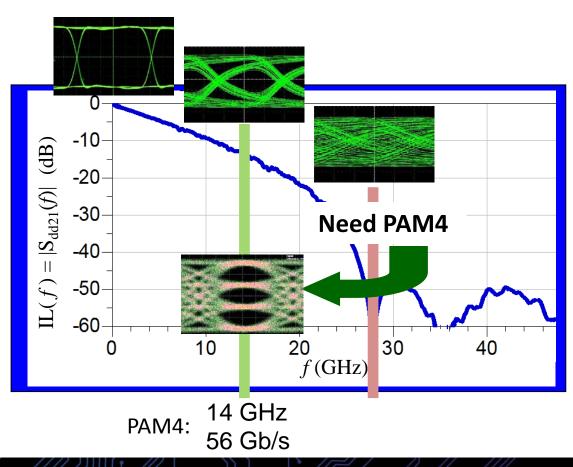

### The problem

- Frequency dependent loss

→ ISI (inter-symbol interference)

- Equalization is not enough

### **Closed eyes**

### The problem

- Frequency dependent loss

→ ISI (inter-symbol interference)

- Equalization is not enough

### **Closed eyes**

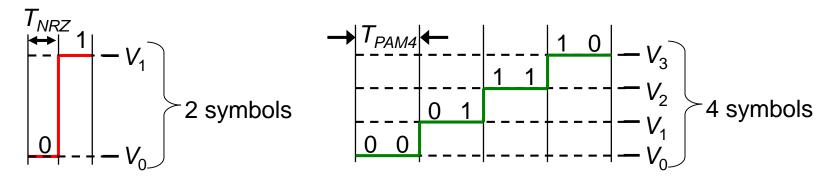

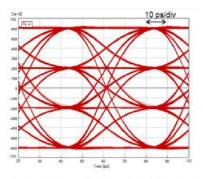

### PAM4 vs NRZ – bits, symbols, baud

• NRZ bits are really PAM2 "symbols"

- NRZ bit rate = symbol rate (Gb/s = Gbaud)

- PAM4 bit rate = 2×symbol rate (Gb/s = 2×Gbaud)

PAM4 28 Gbaud = 56 Gb/s

### **NRZ** is dead

PAM4 development

- 3 slicers, 4-level DFE, mushy clock recovery

- Disruptive Receiver Improvements

DSD based Dessivers

**DSP-based Receivers**

→ PAM8, PAM16, …, PAMn

RIP

NRZ

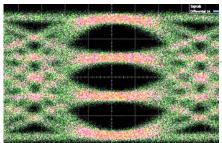

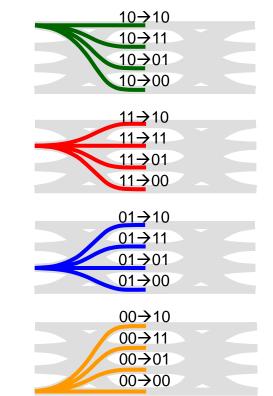

### But PAM4 makes everything gets harder

- Every signal degradation has greater impact on PAM4 than it had on NRZ

- SNR at least 9.5 dB worse

- 16 symbol transitions

- 6 different rise and fall times,  $t_{rise} \& t_{fall}$

- 75% transition density

- Crosstalk, reflections cause more trouble

AND

- Forward error correction, FEC → BER < 10<sup>-5</sup>

- costs power, latency, space

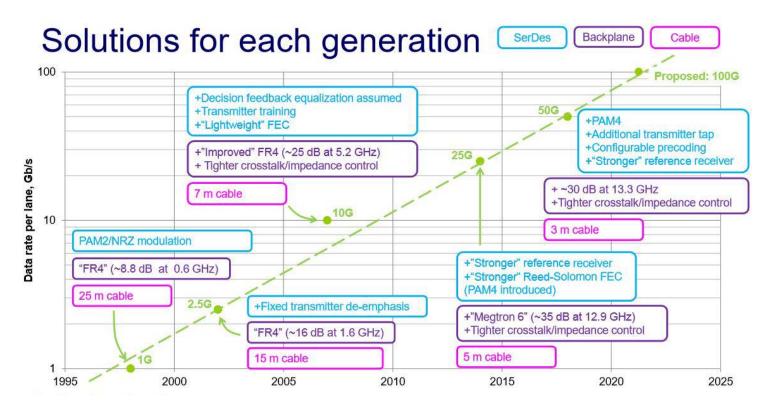

# Path from 56G to 112G

Mike Peng Li, Intel

### NRZ vs PAM4 vs Reach at 56G

| Parameter                                      | USR              | XSR                 | VSR                   | MR                    | LR                 |  |

|------------------------------------------------|------------------|---------------------|-----------------------|-----------------------|--------------------|--|

| Data Rate (Gbps)                               | 18 -58           | 36 -58              | 36 -58                | 36 -58                | 36 -58             |  |

| BER                                            | 1E-15            | 1E-15               | 1E-15                 | 1E-15                 | 1E-15              |  |

| Distance                                       | 10 mm<br>(~0.4") | 50 mm<br>(~2")      | 150 mm<br>(~6")       | 500 mm<br>(~20")      | 886 mm<br>(~34.9") |  |

| Interconnect                                   | МСМ              | PCB+ 0 connector    | PCB + 1 connector     | PCB + 1 connector     | PCB + 2 connectors |  |

| Insertion Loss<br>(dB)<br>(at f <sub>N</sub> ) | 2                | 4 (PAM4)<br>8 (NRZ) | 10 (PAM4)<br>23 (NRZ) | 20 (PAM4)<br>36 (NRZ) | 30 (PAM4)          |  |

| Modulation                                     | NRZ              | NRZ or PAM4         | PAM or NRZ            | PAM4                  | PAM4               |  |

| FEC                                            | N                | N dead yet!         | X Y/N                 | Y                     | Y                  |  |

| NR. NR.                                        |                  |                     |                       |                       |                    |  |

#### Is NRZ dead? No !!

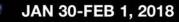

#### FPGA 58 Gbps PAM4/30 Gbps NRZ Transceiver Measurements

- PAM4: BER of <1e-9 observed at 58 Gbps with channel insertion loss (BGA-to-BGA) < -30dB</li>

- NRZ: Error free at 30 Gbps with channel insertion loss (BGA-to-BGA) < -40dB</li>

- TX and RX exceed the Ethernet and CEI 28G NRZ and 56G PAM4 spec

### **112G Feasibility**

- PAM4: Feasible for 30 dB (at Nyquist) channel, backward compatibility insured, great value proposition

- PAM4 and PAM8 comparison analysis has been done for BP/LR channels, and PAM4 out-performs PAM8 in general

- Advanced medium (e.g., better PCB materials, cable backplane) needed to be considered to achieve practical reach objectives for BP and DAC

- Constraints are in how much power the system can afford, which affects the SERDES implementation choices

### RX Architecture vs RS(544, 514) (i.e., KP FEC) vs Performance

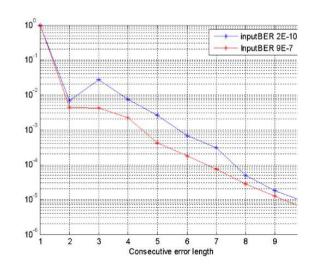

- If the RX does not have DFE, then the main burst error source is eliminated.

- A RX dominated with FFE can compensate reflections without introducing burst errors

- Post FEC BER < 1e-25 achieved with FFE dominate RX, exceeding all system requirements.

BER Improvement by RS(544,514,15) vs. Various Burst Error: PAM4 ų, 9 **BER with FEC [log10]** BER 10-15 random error b1b0 = 0.1b1b0 = 02b1b0 = 0.3b1b0 = 0.4b1b0 = 0.5b1b0 = 0.6h1h0 = 0.7b1b0 = 0.8b1b0 = 0.9no improvemne 25 8 -7 -5 -3 -10 Raw BER [log10]

# FEC and 112G Outlook

Cathy Liu, Broadcom Limited

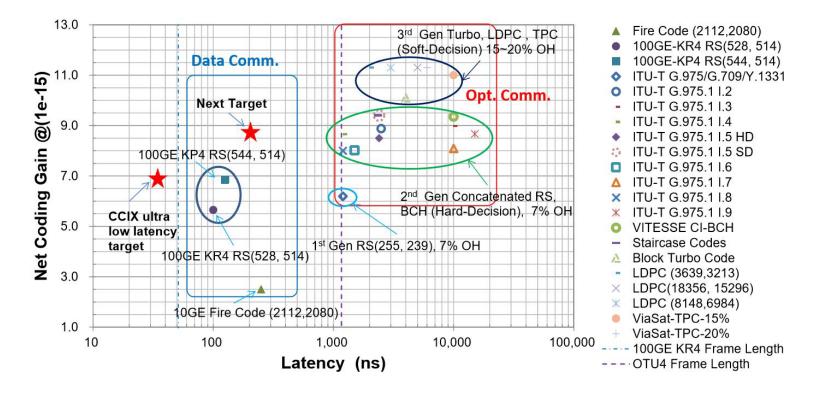

### Landscape of FEC Technology

#### **Post-FEC Measurements**

JAN 30-FEB 1, 2018

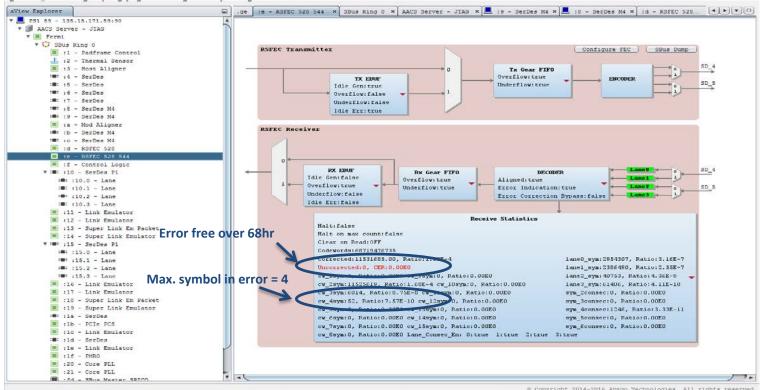

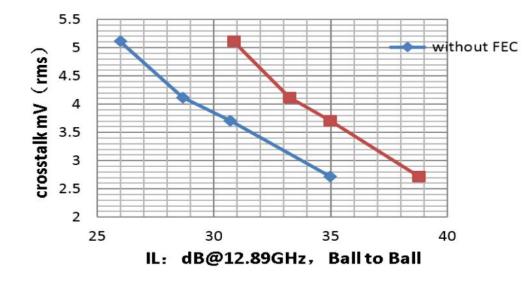

### **56G PAM4 KP4 FEC Test Results**

Error statistic (10 hr)

Channel loss and crosstalk tolerance improvement (post-FEC BER < 1e-15)

23

UBM

### **112G Outlook**

### **112G Design Challenges**

- OIF CEI 112G projects are already underway

- PAM4 is likely signaling format for VSR application

- o NRZ is out

- $\circ~$  Industry has digested PAM4 and FEC challenges through 56G design and production

- So the biggest challenge of 112G PAM4 design is the doubling bandwidth (component, package, device, T&M...)

- What if PAM4 is not good enough for long reach application?

- o PAM8, PAM16, or QAM?

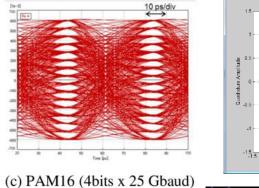

(a) PAM4 (2bits x 25 Gbaud)

JAN 30-FEB 1, 2018

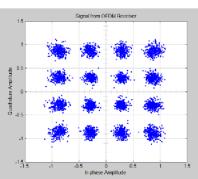

(d) 16QAM

25

UBM

# **Optics & PAM4**

Mark Marlett, Inphi

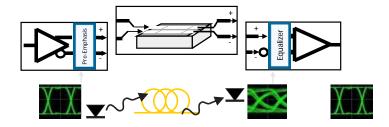

### **DSP enables PAM4 optical channels**

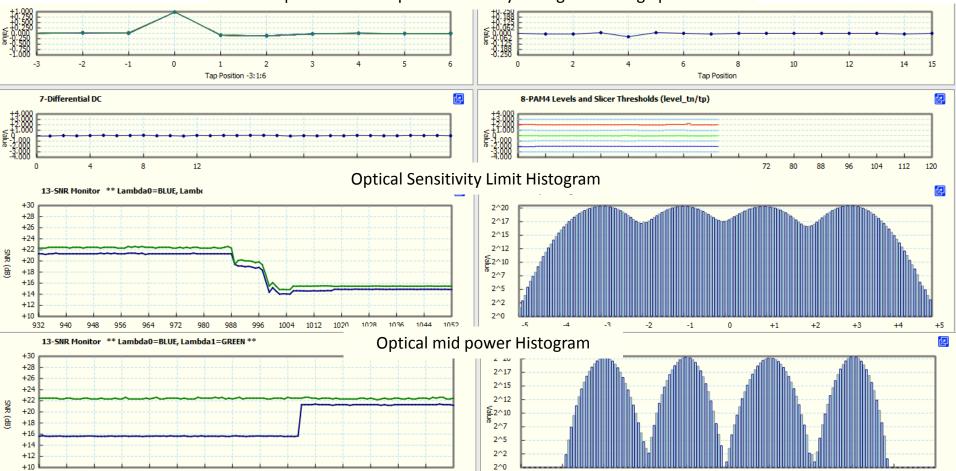

Multi-tap TAP FFE + adaptation of many timing and voltage parameters

### **Optical Communications future**

Higher Data rate (400G+) Modules

- More DSP

- New FEC

- Higher baud rates (56Gbaud)

- More wavelengths on the same fiber

- Fitting more data in these bandwidth limited channels

- So where does NRZ (PAM2) fit in?

- NRZ is in legacy (<28 Gb/sec)

- What is the future of Modulation?

- PAM4 -> PAM? -> ??

- PAM4+ -> DSP

### Receiver test has some big challenges beyond just the PAM4 issues!

Greg LeCheminant, Keysight

# Use of FEC allows for a much higher SER for the hardware. (Shouldn't SER/receiver testing be a lot easier now?)

- High coding gain FEC means that a simple SER analysis does not exactly predict the overall link integrity

- Pre-FEC SER could be within the required limit, but if there is a long burst of errors, frames can be lost

- We (T&M) need to do a better job of showing the 'signature' of errors, whether they are random or bursty

# Frame loss analysis (counting errors within the FEC frame block) would be helpful

- If the data is 'striped' across multiple lanes, all lanes need to be monitored simultaneously. Is it practical?

- Standards/T&M challenge: Consider new ways to account for long bursts of errors other than frame loss ratio when there are many parallel lanes

### Acquisition for PAM4 transmitter characterizaton

Pavel Zivny, Tektronix

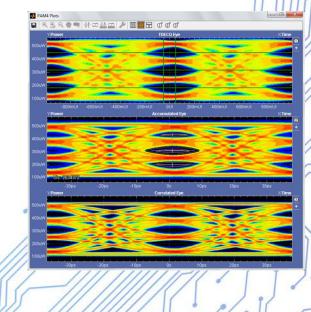

### Acquisition for PAM4 transmitter characterizaton

Pavel Zivny, Tektronix

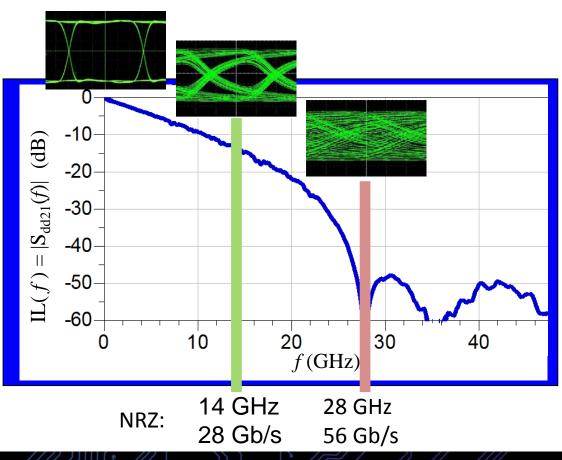

#### Traditional link design. The receiver rule: more BW is better (keeps the eye more open)

The links as we know them from lower loss systems. Equalization was low key or (optical systems) none

What's the DUT doing: the Receiver for PAM4 at 53 GBd (aka 100 Gb/s) does sample at Nyquist. The extra bandwidth beyond that is not that useful\* as it's past Nyquist.

- Today the receivers for 53+ GBd are an A/D that samples at the symbol rate... (53 GS/s for a 53 GBd signal) ... and the Nyquist is then 26 GHz ... energy beyond 26 GHz is aliased\* and thus not fully in control of the DSP

- For this and other reasons, the receiver is rolled of just past Nyquist.

- Thus the measurement system should not measure past what the receivers will be able to see. i.e. the measurement bandwidth <u>ought to</u> be similar to what the Rx does.

\*Since we sample in-phase the alias is not as bad as in asynchronous systems. And: there's (typically) is an analog boost (CTLE) *before* sampling... *not* aliased.

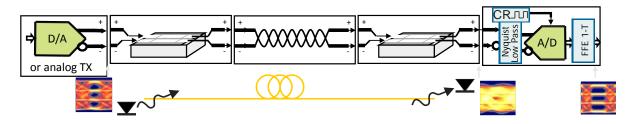

# Ethernet changed the measurement bandwidth significantly to match what the RX sees: to measure a 26 GBd signal, use 13 GHz scope BW 4<sup>th</sup> order Bessel-Thomson filter, with controlled roll-off)

And you have to get the bandwidth right! Since:

- Higher bandwith will improve the eye opening. You might get false 'good' on bad DUT.

- Lower bandwidth than the required ½ of the symbol-rate-frequency is (i.e. 13 GHz for 26 GBd of the 50 Gb/s link) will worsen the TDECQ, and increase the number of false 'fail' DUTs.

- Opposite will happen for the RX test (where the oscilloscope measures up the stressors)

TDECQ = 1.5015 dB FFE Taps = 1.0138 0.0059905 0.0016472 -0.02332 0.0019147 OMA Outer = 0.97727mW

JAN 30-FEB 1, 2018

#### Conclusion

- The measurement bandwidth is critical for correct TDECQ measurement.

- Unlike in NRZ, where the measuring device (oscilloscope) doesn't close the eye\*, the bandwidth of the oscilloscope limits the

- This is true for the measurent of the TX, and...

- ... the measurement of the RX, since the stressed eye source is measured with the same (oscilloscope) measurement bandwidth

\*about 1% closure is due to the B-T in NRZ (0.75x filter)

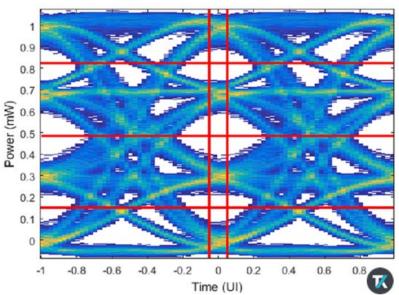

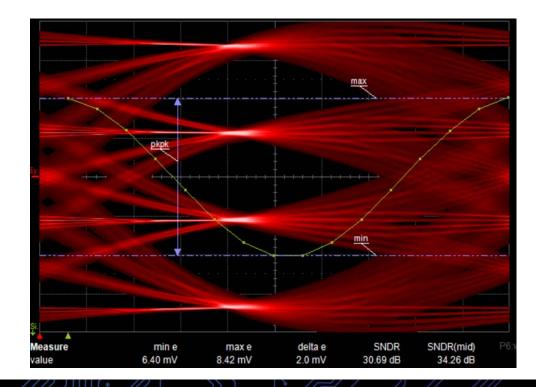

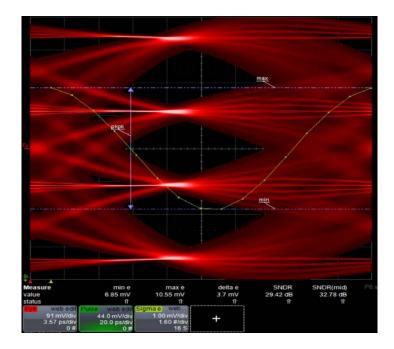

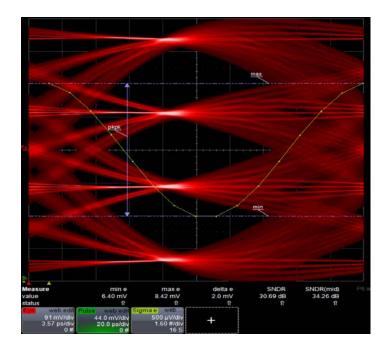

# SNDR as a good SI Indicator?

Marty Miller, Teledyne-LeCroy

### **Signal to Noise and Distortion**

- Calculated from a QPRBS13

- "linear fit" -> Pulse

$$SNDR = 10\log_{10}\left(\frac{p_{\text{max}}^2}{\sigma_e^2 + \sigma_n^2}\right)$$

(dB)

### Why not a SNDR (mid) using error at center?

• Jitter affects RMS fit error at 0 & 1UI (500fs and 50fs Rj)

# **Panel Discussion**