# **DesignCon 2012**

Method for Troubleshooting **Power Integrity Problems in** Programmable Logic Device Electronic Systems by Embedded Measurement of Power **Distribution** Impedance

Cosmin Iorga NoiseCoupling.com cosmin.iorga@noisecoupling.com (805) 231-9786

470

#### Outline

- Overview of Power Distribution Networks (PDN)

- **PDN Failure Mechanisms**

- PDN Troubleshooting Techniques

- **Proposed PDN Troubleshooting Method**

- Embedded On-Die PDN Impedance Measurement

- Case Study Implemented in a Spartan 3A FPGA Conclusions

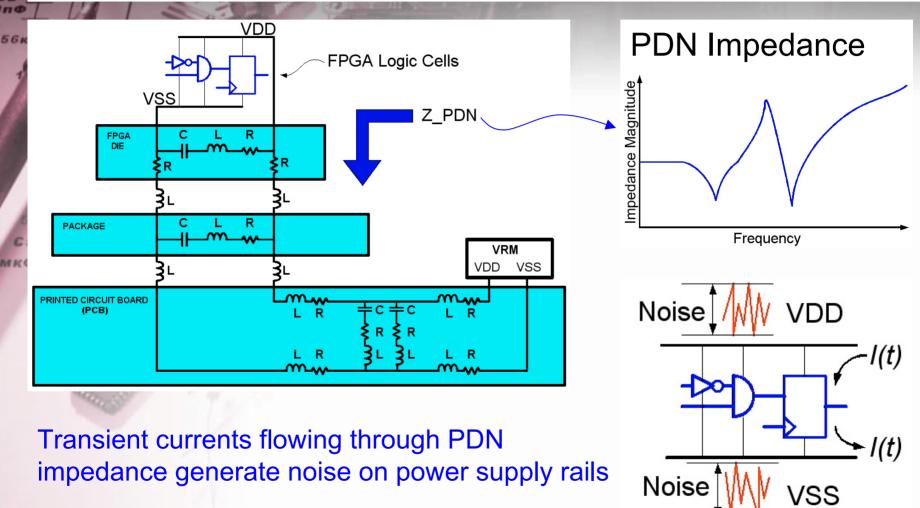

#### **Overview of Power Distribution Networks**

#### **PDN Failure Mechanisms**

# **PDN Failure Types**

#### **Total PDN Failure**

- Easy to detect

- Can be addressed using standard troubleshooting techniques

#### **PDN Performance Degradation**

- System level performance degradation

- System level "indirect" failures

- Sometimes failures are intermittent

- Hard to detect

- Difficult to troubleshoot

#### **PDN Failure Mechanisms**

# **PDN Failure Types**

#### **Total PDN Failure**

Easy to detect

56K0

Can be addressed using standard troubleshooting techniques

#### **PDN Performance Degradation**

- System level performance degradation

- System level "indirect" failures

- Sometimes failures are intermittent

- Hard to detect

- Difficult to troubleshoot

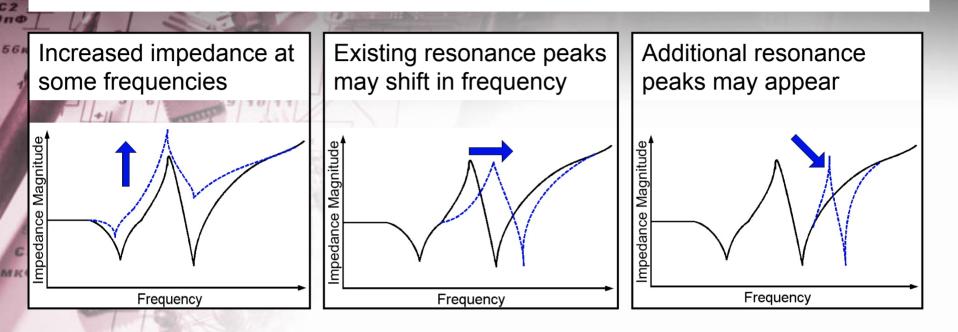

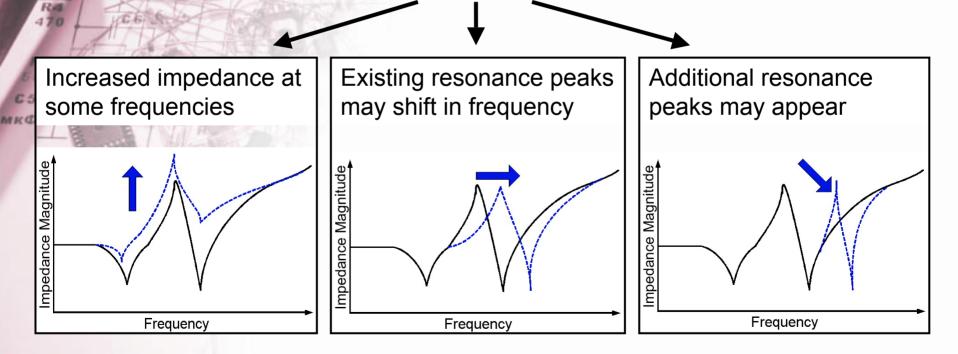

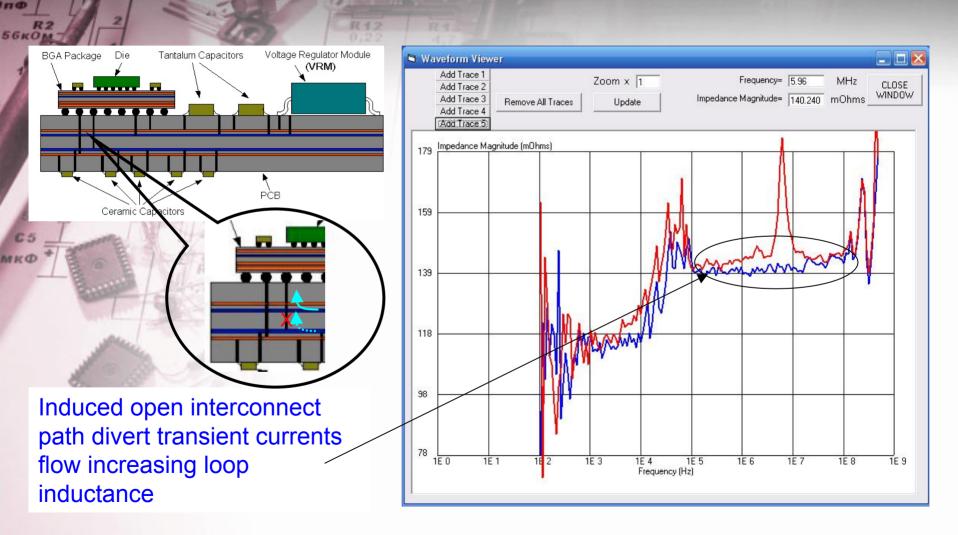

## **PDN Performance Degradation**

- The increase in PDN impedance increases the noise on power supplies

- New or frequency shifted resonance peaks may now coincide with chip operating frequencies generating significant supply noise

# **Troubleshooting PDN**

These types of problems and especially open circuit capacitors, open vias or solder joints, and increased series resistance are in general hard to identify using common test instruments due to:

1. redundant / parallel power supply current paths

2. multiple decoupling capacitors connected in parallel

# **Troubleshooting PDN - What are we looking for?**

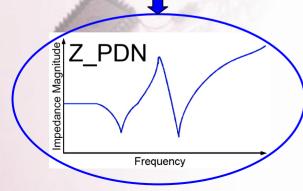

We want to be able to detect any increase in PDN impedance and the frequency location and magnitude of resonance peaks.

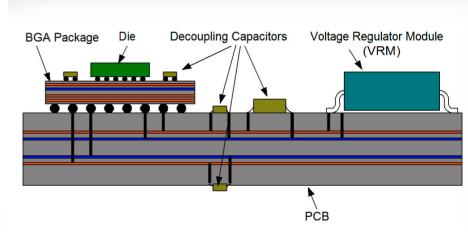

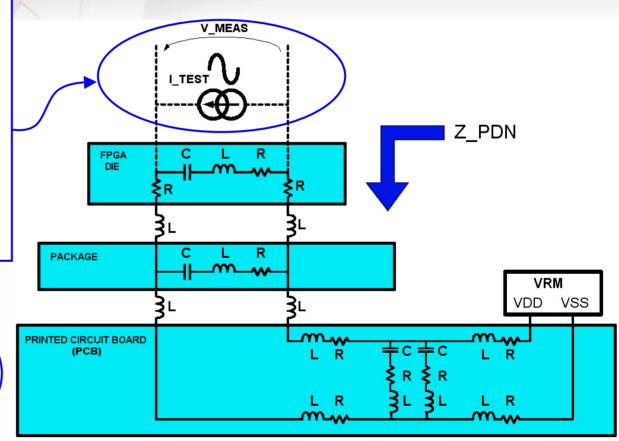

#### **Troubleshooting PDN - What do we** need? 56KC We need to get access to the PDN impedance frequency profile as seen by the logic circuits on the FPGA / PLD die. Z PDN Rat 471 Frequency BGA Package Decoupling Capacitors Voltage Regulator Module (VRM) PCB

#### **AC Steady State Analysis**

AC steady state analysis connects a sinusoidal current source to the measured port and records the voltage drop while sweeping the sinusoidal current frequency

56KOM

#### **Proposed PDN Troubleshooting Technique** no **AC Steady State Analysis** SGRON **FPGA DIE** V MEAS CLB CLB CLB CLB CLB CLB CLB R I TEST CLB CLB CLB CLB CLB CLB CLB CLB Z PDN CLB CLB CLB CLB R FPGA C DIE CLB CLB CLB CLB CLB CLB CLB MKD R R CLB CLB CLB CLB CLB CLB CLB ∩ ,vss R С PACKAGE VRM VDD VSS Z\_PDN mpedance Magnitude PRINTED CIRCUIT BOARD (PCB) R R R Frequency (patent pending technology)

Cosmin lorga - NoiseCoupling.com - cosmin.iorga@noisecoupling.com

C 2

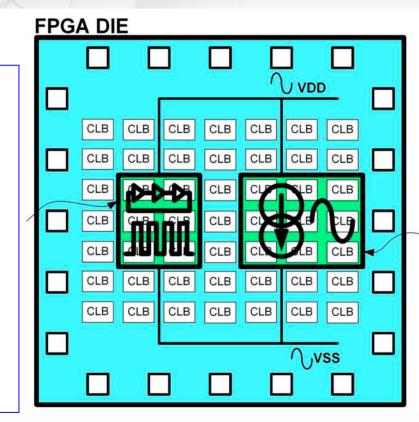

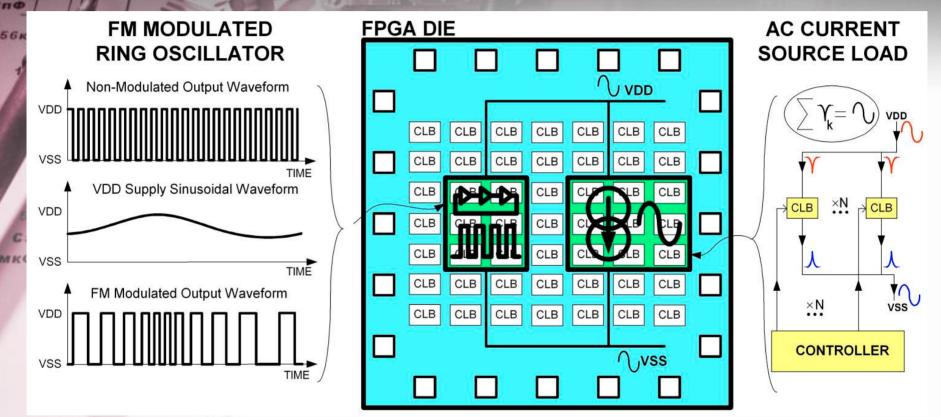

# **FPGA / PLD Implementation**

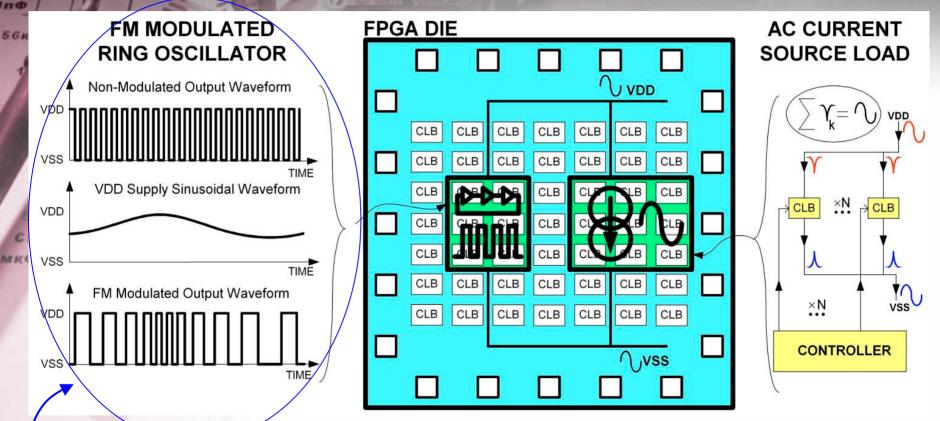

FM MODULATED RING OSCILLATOR

82 5680M

> A group of FPGA logic blocks is configured to form a ring oscillator

AC CURRENT

A group of FPGA logic blocks is configured to function as a sinusoidal current source

(patent pending technology)

The sinusoidal current flows through the power distribution network and generates sinusoidal variation of the on-die power supply voltage

(patent pending technology)

The sinusoidal variation of the voltage supply modulates the frequency of the ring oscillator

(patent pending technology)

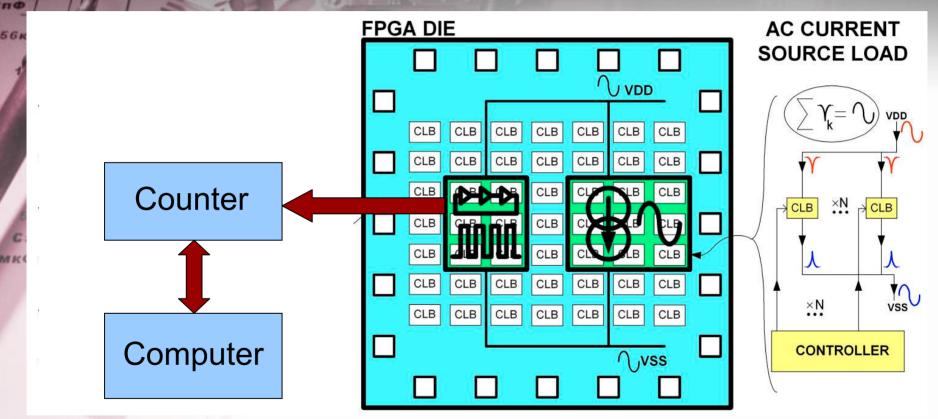

A counter circuit measures the frequency of the ring oscillator

PDN impedance is calculated from the average frequency deviation

(patent pending technology)

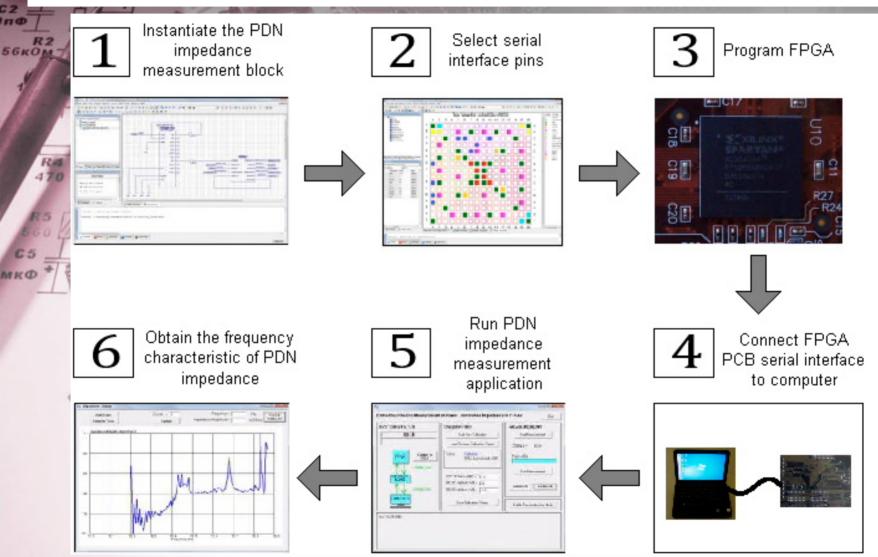

# **Device Configuration and Measurement Process**

Cosmin lorga - NoiseCoupling.com - cosmin.iorga@noisecoupling.com

62

#### **Case Study**

- The proposed PDN troubleshooting technique has been implemented in a Spartan 3A FPGA on a test board

- PDN impedance frequency profile has been measured at frequencies up to 500MHz

- Various PDN failure mechanisms have been intentionally induced in the test board

- The proposed PDN troubleshooting technique has been used to detect each induced PDN failure mechanism

#### **Case Study**

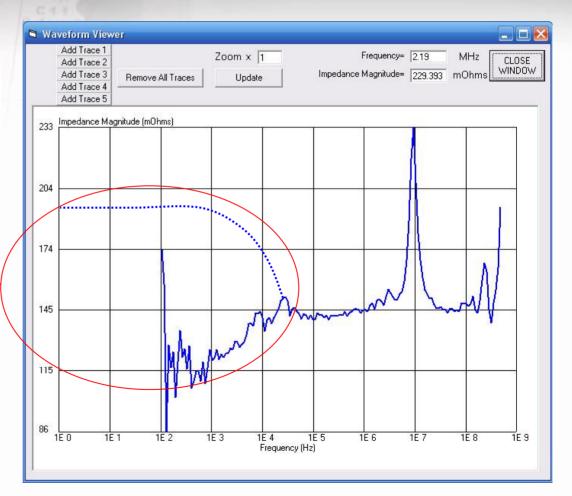

Measured on-die PDN impedance frequency profile

#### Measurement up to 500MHz

9 10 11

#### Not accurate below 20kHz

Accuracy can be extended below 20kHz with the expense of increased measurement time

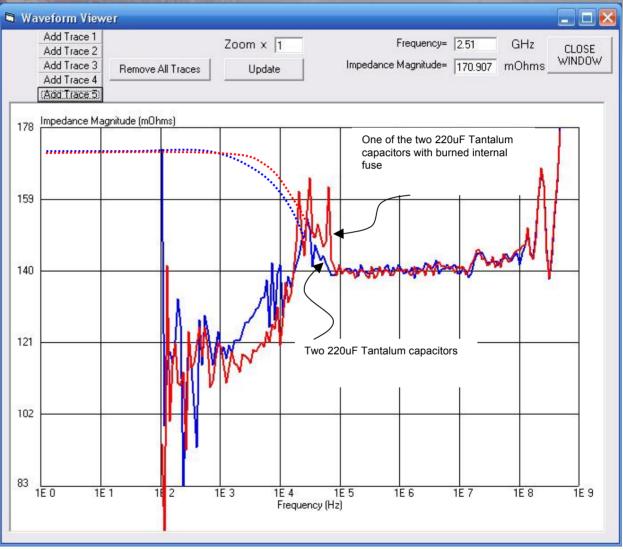

# Detecting Tantalum Capacitors with Burnt Internal Fuse

One of the two 220uF **Tantalum capacitors** with burnt internal fuse age Regulator Module im Capacitors BGA Package (VRM) Ceramic Capacitors

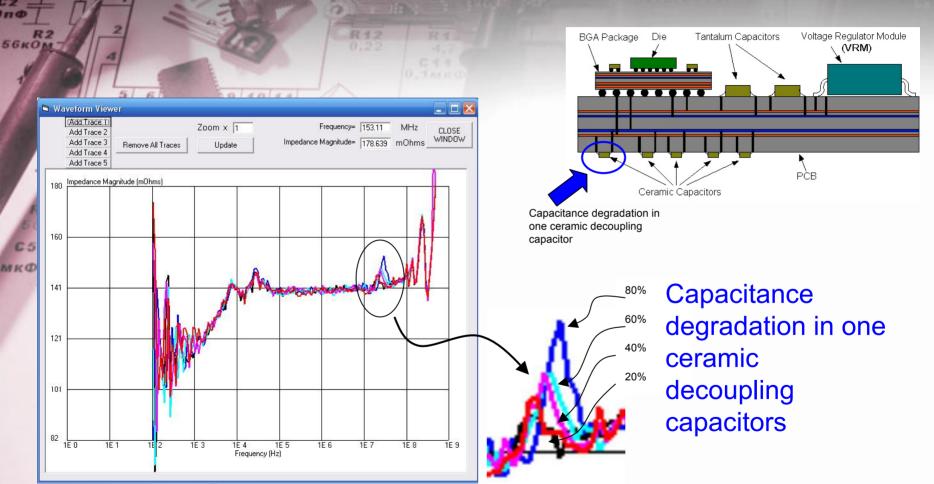

## Detecting Capacitance Degradation in Ceramic Capacitors

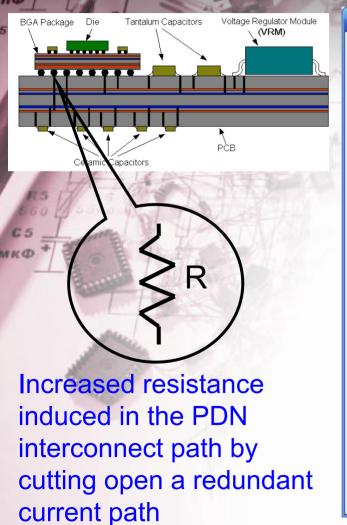

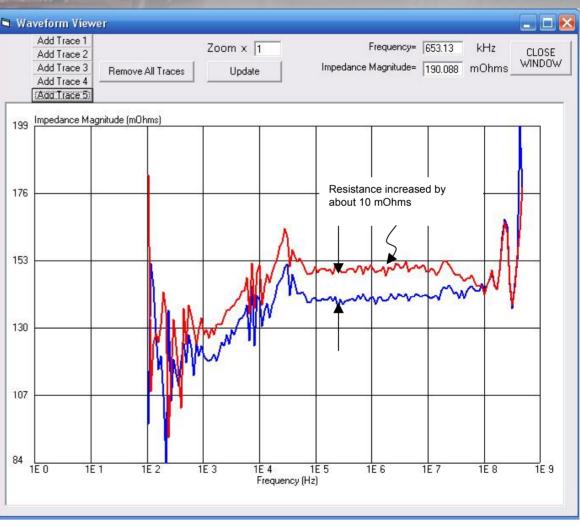

## **Detecting Increased Series Resistance of PDN Interconnects**

### **Detecting Increased Loop Inductance**

#### **Test Case Summary**

PDN failure mechanisms detected by the proposed method:

- Tantalum capacitors with burnt internal fuse

- Capacitance degradation in ceramic capacitors

- Increased series resistance of interconnects

- Increased PDN loop inductance

#### Conclusions

- Low cost PDN troubleshooting method for PLD devices

- Uses only common logic blocks and can be implemented in most existing PLDs (FPGA, CPLD, ...)

- PLDs can be temporarily configured in PDN troubleshooting mode and then reconfigured back to their intended functionality

- Can be easily implemented in existing production test floors and in product support/repair environments

- Allows remote PDN troubleshooting in systems installed in the field or in hardly accessible areas

- Evaluation on a FPGA test case has shown how this method can identify typical PDN failure mechanisms

56KO