#### Accurate and Efficient SSN Modeling Chris Herrick

# Agenda

- What is SSN?

- Model Types

- Modeling techniques

- Simulation Tips and Tricks

- Incorporating the latest Ansoft features

- Conclusions

# What is SSN?

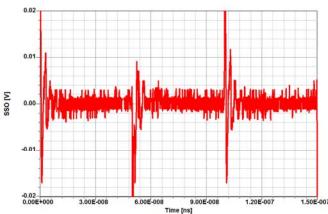

- Simultaneous Switching Noise is the deleterious effect of simultaneous switching outputs (SSO).

- Also referred to as Ground Bounce or Power Bounce

- Exacerbated by poor return path and high loop inductance

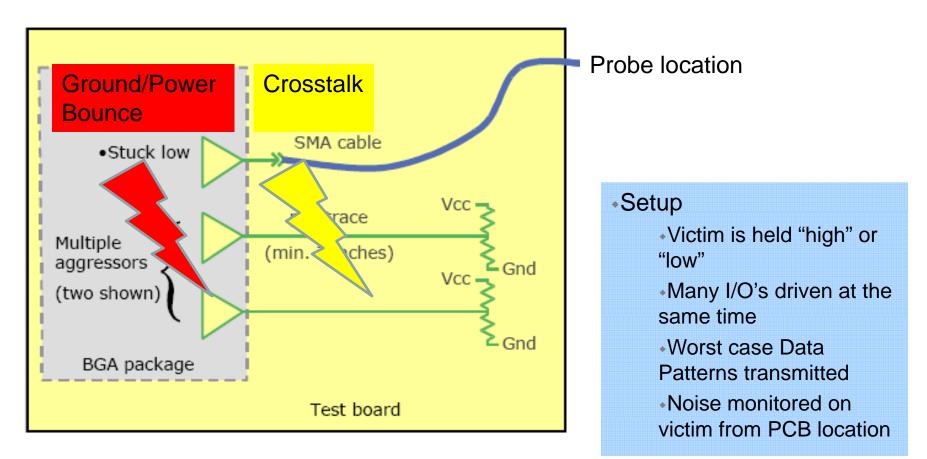

- Measured by fixing victim High or Low and monitoring output

# Why is SSN important?

- SSN Analysis gives more complete picture of both Signal Integrity and Power Integrity

- Ignoring the effects of SSO can result in a failed system design

- Increased challenges as speeds increase, voltages decrease and current increases

- Helps uncover problematic crosstalk

- Helps evaluate true PDN performance

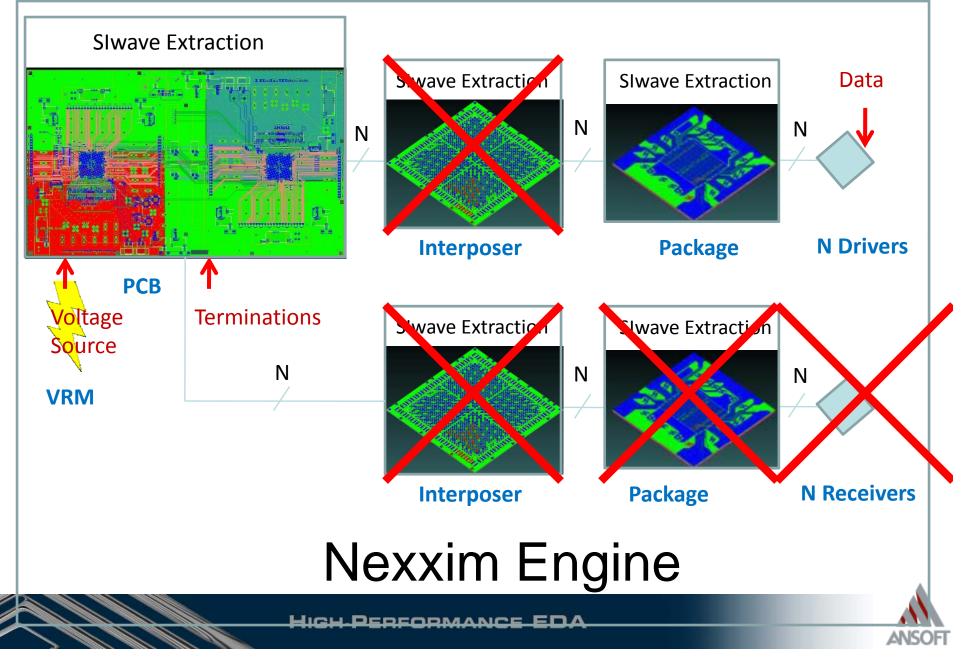

#### **Typical Setup**

Ref: BGA Crosstalk by Howard Johnson, March 1, 2005

HIGH-PERFORMANCE EDA

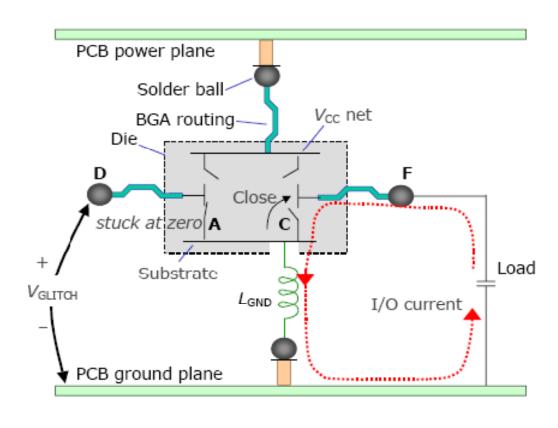

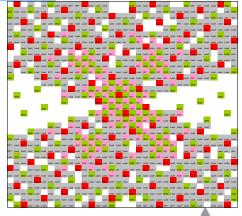

#### **SSN From Ground Bounce**

•BGA between PCB power and ground planes

•At time zero switches C closed and F transitions Low -> huge I/O current transient

$$V_{glitch} = L_{gnd} di/dt$$

•Victim D is held low will transmit voltage V<sub>glitch</sub>

HIGH-PERFORMANCE EDA

# **Model Types**

- Need to include all relevant effects of system; Both SI and PI

- Need models for: ICs, Packages, PCBs and VRMs

- Models may be extracted or gathered from vendors

- Each model should be independently verified for accuracy

#### **Designer Environment**

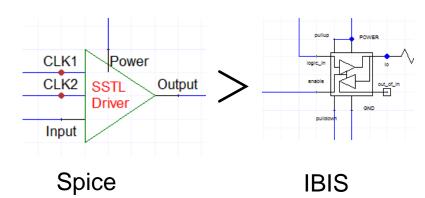

## **Driver Models**

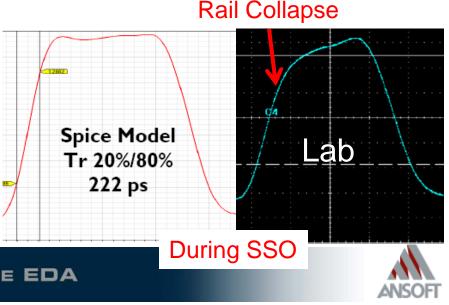

- Need to accurately model Signals and Power

- Obtain transistor level models if at all possible

- IBIS tends to be pessimistic because current scales linearly with increased drivers

- Verify waveforms for single driver AND during SSO

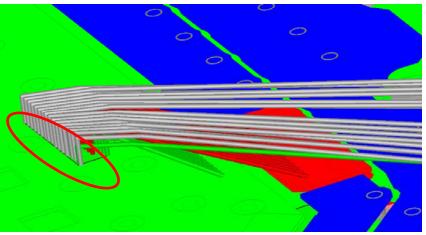

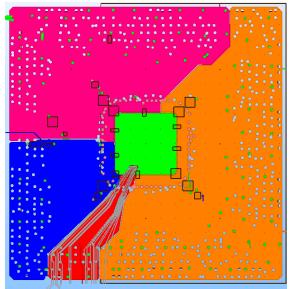

# Package Model

- Obtain layout and extract if possible

- Add Solderballs, Solderbumps, Bondwires to model

- Group Power/Ground pins on die side

- Extract Bank of signals

HIGH-PERFORMANCE EDA

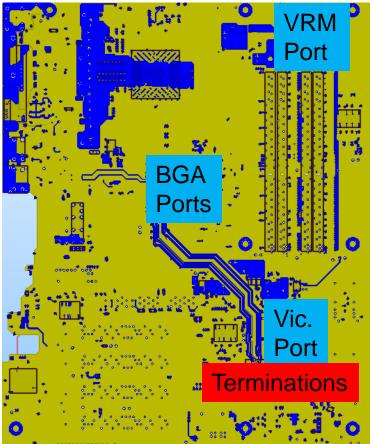

# **PCB Model**

- Extract individual Signal Power/Ground Pins at Package if feasible

- Place port at VRM

- Place port on victim far end

- Terminate far end of line with resistors

#### **VRM Model**

- Almost always modeled as an ideal voltage source

- Could also use non-ideal circuit model

- Important for DC-DC switching power supplies

# **Modeling Techniques**

- Kitchen Sink Simulate Everything!

- Generally not practical

- Nearest Neighbors

- Only simulate what's relevant

- Signal grouping

- Combine many pins into one and scale driver

- Current Mirror

- Mirror a single driver multiple times

### **Nearest Neighbors**

- 1. Identify Victim and nearest neighbors based on proximity

- 2. Extract largest segment you can afford with available hardware

- 3. Attached Driver models to each signal pin

High Speed Packages generally have banks-easy to segment

Well placed PWR/GND balls limit return path loop area

# **Nearest Neighbor Tradeoffs**

- Most accurate and flexible method

- Simulates Skew/Delay between lines

- Allows different data patterns

- Long transient simulation

- Potential for convergence trouble

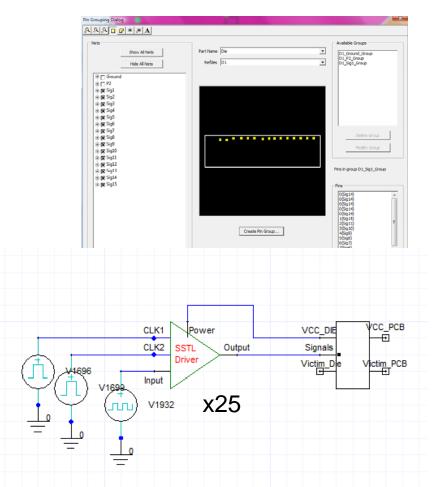

# **Signal Grouping**

- 1. Apply pin grouping to signals at Die side

- 2. Attach single port for Aggressor group

- 3. Extract PCB ports as before

- 4. Create subcircuit for driver model

- 5. Multiply subcircuit M times and connect to aggressor port

X1 CK1 CK2 Input Output Power driver M=25

# Signal Grouping Tradeoffs

- Much quicker analysis

- Greatly reduces port count

- Eliminates convergence issues with multiple drivers

- Not simulating XTLK induced skew

- Same data pattern used on all aggressors

- Assumes all lines are similar in impedance and delay

- Lose information on individual lines

- One bad signal line will affect net results

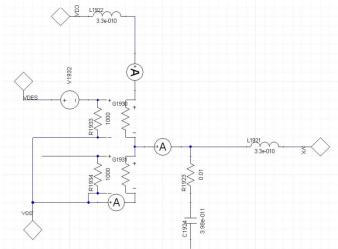

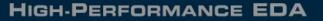

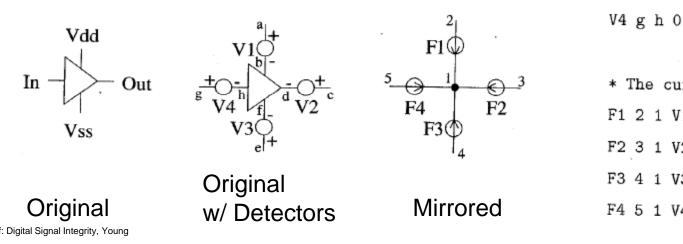

# **Current Mirroring**

- 1. Use same extracted model as "Nearest Neighbors"

- 2. Place driver on one aggressor

- Monitor current at signal and die connections using series 0v Voltage sources

- 4. Attach CCCS to all other signal lines mirroring same current as driver

- 5. Attach CCCS to die scaling current x M-1 drivers

Ref: Digital Signal Integrity, Young

# **Current Mirroring Tradeoffs**

- Much quicker analysis

- Eliminates convergence issues with multiple drivers

- Still can inspect individual s-parameters

- Not simulating XTLK induced skew

- Same data pattern used on all aggressors

- Assumes all lines are similar in impedance and delay

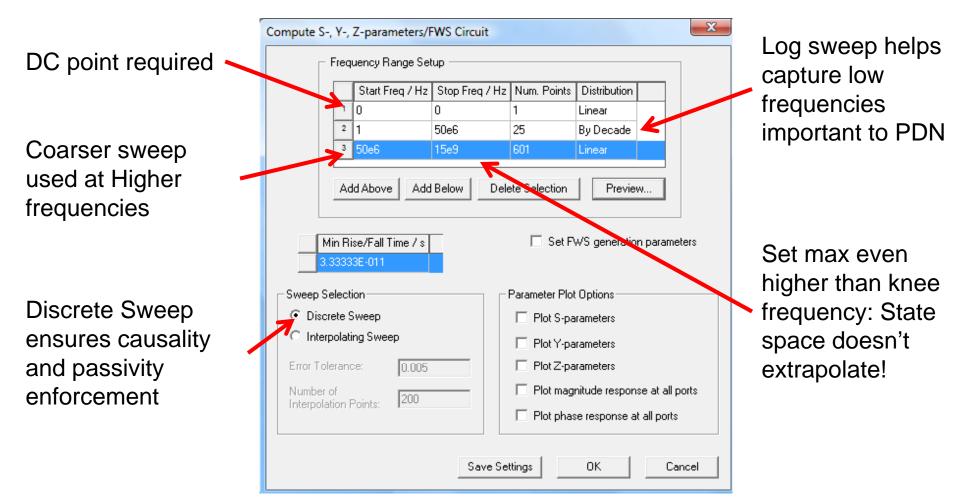

# **Simulation Tips and Tricks**

- Convolution versus state-space

- Frequency sweep setup

- Mixed port impedances

- Achieving Convergence

# **S-parameter Handling**

| State-Space (Default)                                                                                                                                                                                                                                                     | Convolution                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Much faster for long transients</li> <li>Passivity enforcement</li> <li>Causality enforcement</li> <li>Up front cost building model</li> <li>Does not extrapolate</li> <li>May not achieve fit on noisy data</li> <li>Cannot model long delays, ~22 λ</li> </ul> | <ul> <li>More options for convergence</li> <li>Can handle long delays</li> <li>Data filtering options</li> <li>Extrapolates well</li> <li>Sim time increases<br/>quadratically with tran time</li> <li>Requires linearly spaced data</li> </ul> |

# **Sweep Setup**

**HIGH-PERFORMANCE EDA**

#### **Port Impedances**

Choose port impedances that are relatively close to structure impedance

Use 1 or .1 ohms for power, 50 ohms for signal lines

This helps model accuracy and avoids 0dB values in touchstone file

| 🖈 Active | Name        | Reference Impedance (Ohms) | Port Positive "Terminal" Net | Port Negative "Terminal" Net | Port 🔺 |

|----------|-------------|----------------------------|------------------------------|------------------------------|--------|

| Yes      | Package_C3  | 50                         | NETC03                       | GND                          | C3(L   |

| Yes      | Package_C4  | 50                         | NETC04                       | GND                          | C4(L ≡ |

| Yes      | Package_C5  | 50                         | NETC05                       | GND                          | C5(L   |

| Yes      | Package_C6  | 1                          | VCCO_6                       | GND                          |        |

| Yes      | Package_C7  | 50                         | NETC07                       | GND                          | C7(L   |

| Yes      | Package_C8  | 50                         | NETC08                       | GND                          | C8(L   |

| Yes      | Package_C9  | 50                         | NETC09                       | GND                          | C9(L   |

| Yes      | Package_C10 | 50                         | NETC10                       | GND                          | C10(   |

| Yes      | Package_C12 | 50                         | NETC12                       | GND                          | C12(   |

| Yes      | Package_C13 | 50                         | NETC13                       | GND                          | C13(   |

| Yes      | Package_C14 | 50                         | NETC14                       | GND                          | C14(   |

| Yes      | Package_C15 | 50                         | NETC15                       | GND                          | C15(   |

| Yes      | Package_C16 | 1                          | VCCO_6                       | GND                          |        |

| Yes      | Package_D3  | 1                          | VCCO_6                       | GND                          |        |

| Yes      | Package_D4  | 50                         | NETD04                       | GND                          | D4(l   |

| Yes      | Package_D5  | 50                         | NETD05                       | GND                          | D5(l   |

| Yes      | Package_D6  | 50                         | NETD06                       | GND                          | D6(l   |

| Yes      | Package_D7  | 50                         | NETD07                       | GND                          | D7(l   |

| Yes      | Package_D9  | 50                         | NETD09                       | GND                          | D9(l   |

| Yes      | Package_D10 | 50                         | NETD10                       | GND                          | D10    |

| Yes      | Package_D11 | 50                         | NETD11                       | GND                          | D11    |

| 4        |             |                            |                              |                              | *      |

Designer dynamic link to Slwave will preserve port impedances

HIGH-PERFORMANCE EDA

# **Achieving Convergence**

- Inspect individual models (Divide and Conquer)

- Realistic data, passive, causal

- Sufficient bandwidth, resolution

- Frequency dependent materials

- Bypass/Deactivate components to find root cause

- Check state-space fit; tighten s\_element.reltol

- Increase s\_element.max\_states

- Slow risetimes/Soften Edges

- Try generic sources, i.e. Gaussian PRBS

- Reduce .tran step

- Decrease reltol and abstol

- Try convolutions 1-3

- Reduce s-parameter port count

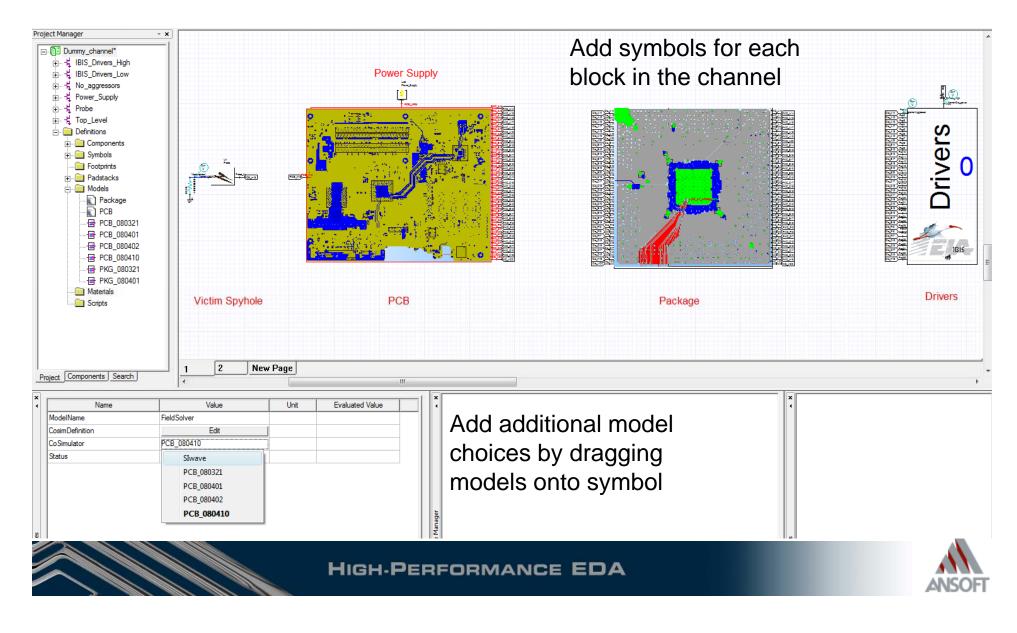

### **Schematic Setup**

- Schematic setup can be tedious and error prone when working with large number of components

- Modular/hierarchical blocks can aid with design management and debugging

- Four methods for automatic setup:

- Dynamic Linking

- APDS

- Designer I/O Wizard

- Slwave Slwizard

#### **Dynamic Links**

Stand-alone GUI to setup transient analysis

Specifically tailored to SSN of DDR interfaces

|    | Separated IBIS &                                                                                                             | &ports Ope                                                                  | en ports list                                                                                                                                                                                                           |                                                      |

|----|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|    | for Driver & Rec                                                                                                             | eiver to b                                                                  | e applied to app                                                                                                                                                                                                        | propriate port                                       |

|    | M APDS Wizard v4,0<br>Příš - About                                                                                           |                                                                             |                                                                                                                                                                                                                         |                                                      |

| is | PCB file D1doc/DDR2ttrain_files/DDR2_train_<br>Driver<br>D1doctDDR2ttrain_files/write<br>VRTEX-5 Info<br>At Info<br>SSTL18_I | Receiver Dxdoc/DDR2train_flestW4f51 K4T51XX3QE_X16 info All DQ_FULL_ODT_OFF | DDR_D0.R_U11.G8           DDR_D0_U11-F29           DDR_D1.R_U11.G2           DDR_D1.R_U11.G2           DDR_D1_U1.E29           DDR_D2.R_U11.H7           DDR_D2_U1.R29           DDR_D3.R_U11.H3           Source Setup | Course Coture                                        |

| S  | ibisIO8<br>Data (DQ) Get Data<br>Transfer<br>Direction<br>Swap                                                               | ibisID8 Data (DO) Get Cu                                                    | 800 Mbps = 1.25 nstit<br>DQ data :                                                                                                                                                                                      | <ul> <li>Source Setup</li> <li>Spec Setup</li> </ul> |

|    | Strobe (DQS) Get C                                                                                                           | Strobe (DQS) Get Cul<br>Vdd with SSN Get Cul                                | Add dVi_AC: 0.2 V<br>Input DDR2/3 Spec<br>Transient Setup<br>Step: 0.1 ns<br>Stop: 30 ns<br>C Schematic Generation only                                                                                                 | <ul> <li>Transient Setup</li> </ul>                  |

|    |                                                                                                                              | Get Cal Term Setup                                                          | Start Recent Result                                                                                                                                                                                                     |                                                      |

HIGH-PERFORMANCE EDA

**APDS**

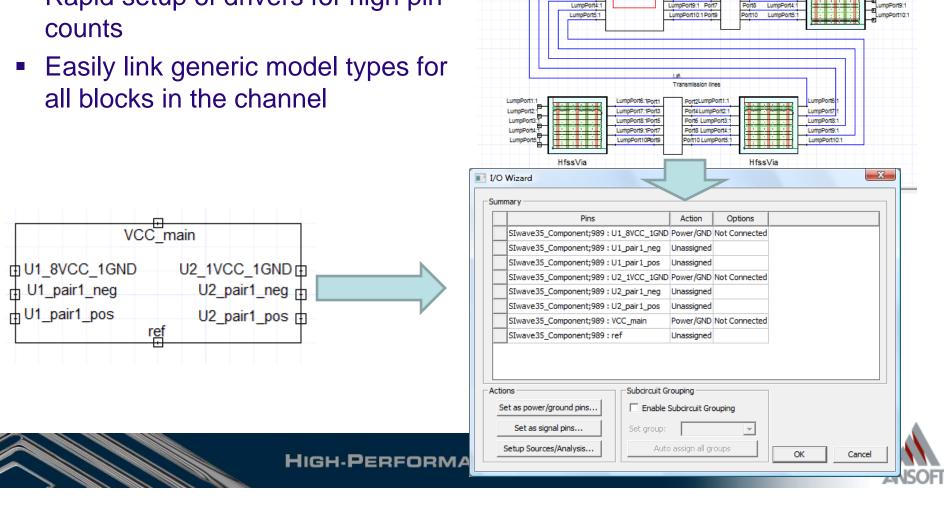

#### **Designer I/O Wizard** m1 - Schematic

Channel - Via transitions and

LumpPort6:1 Port1

LumpPort7:1 Port3

LumpPort8:1 Port5

U4 Transmission lines

Port2 LumpPort1:1

Port4 LumpPort2:1

LumpPort3:

Port6

HfssVia

Connector

SIWave line

LumpPort1: LumpPort2:1

LumpPort3:1

- Launch GUI from Designer 4.1

- Rapid setup of drivers for high pin counts

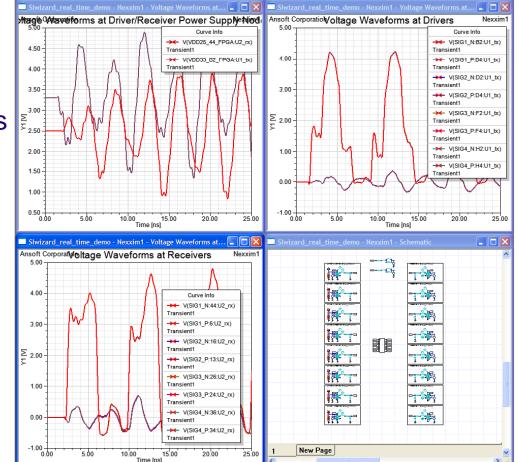

#### Slwizard in v4.0 Slwave

- 1. Select signal nets to simulate

- 2. Assign IBIS TX/RX models to pins on nets

- 3. Identify component power/ground nets

- 4. (Optional) Set VRM parameters

- 5. Set Transient Simulation parameters

#### Pin info preserved from layout

#### Conclusions

- SSN is a powerful simulation offering insight to both Signal and Power behavior

- Accurate device models are critical

- Set realistic goals and choose the best method to obtain them

- Ansoft has the capabilities and the automation to perform accurate and efficient SSN simulations

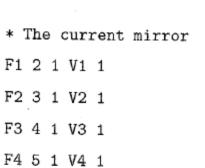

#### **Current Mirroring**

Place drivers for a single aggressor and the victim. Mirror the current to all other aggressors using CCCS. \* The current detectors

V1 a b 0

V2 c d 0

V3 e f 0

Ref: Digital Signal Integrity, Young

HIGH-PERFORMANCE EDA