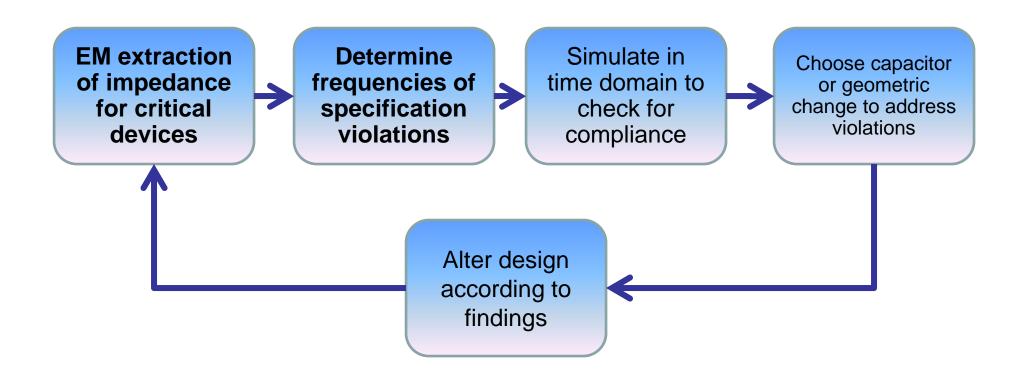

#### Power Plane and Decoupling Optimization Isaac Waldron

### **Overview**

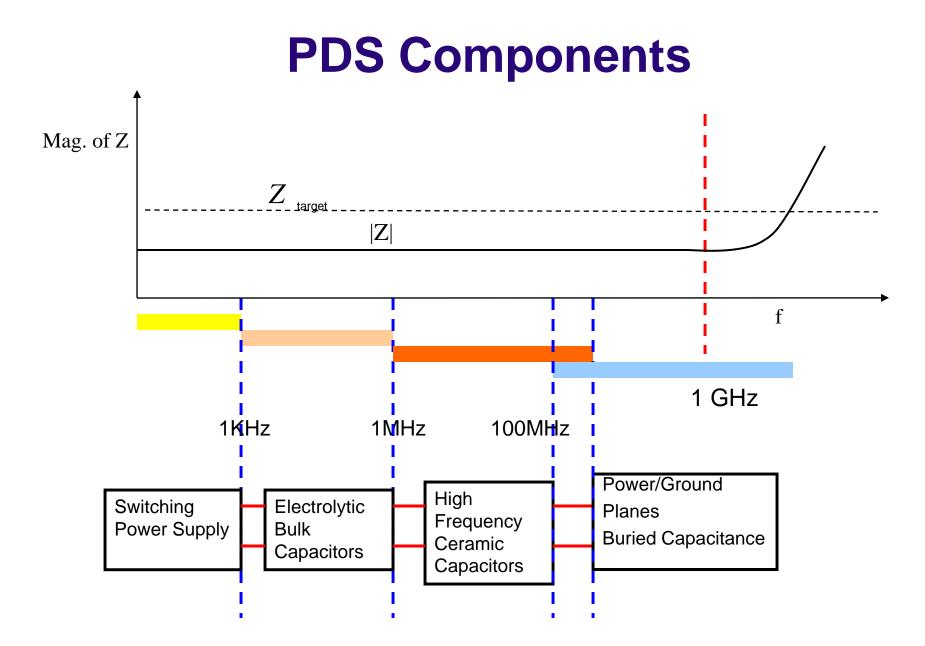

- Frequency- and time-domain power distribution system specifications

- Decoupling design example

- Bare board

- Added capacitors

- Buried Capacitance

- Conclusion

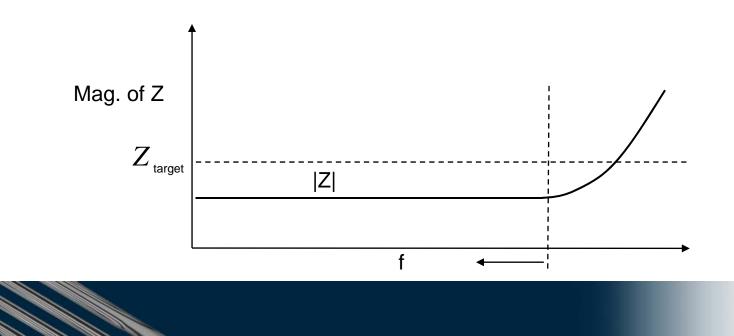

#### **Frequency Domain PDS Targets**

- Excessive impedance seen by a device drawing power from a PDS will cause power voltage to fluctuate

- On a board, impedance must be below target from DC to several hundred MHz

- Working in the frequency domain allows quick estimation of power quality

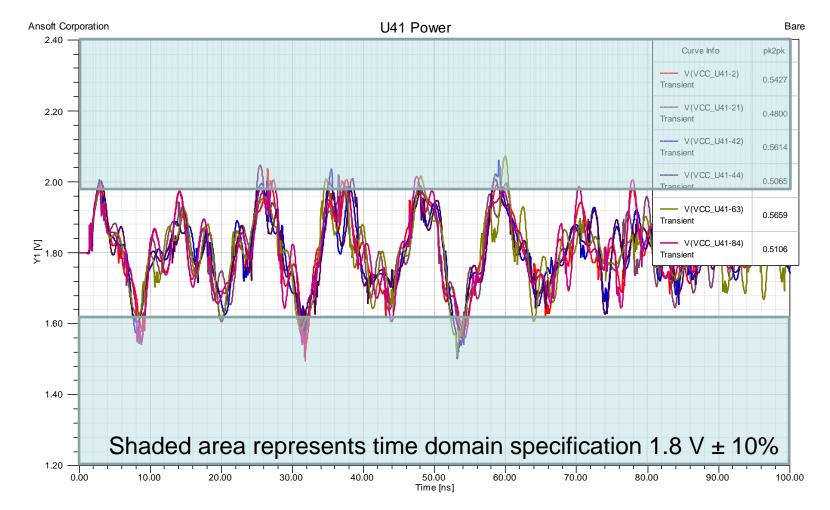

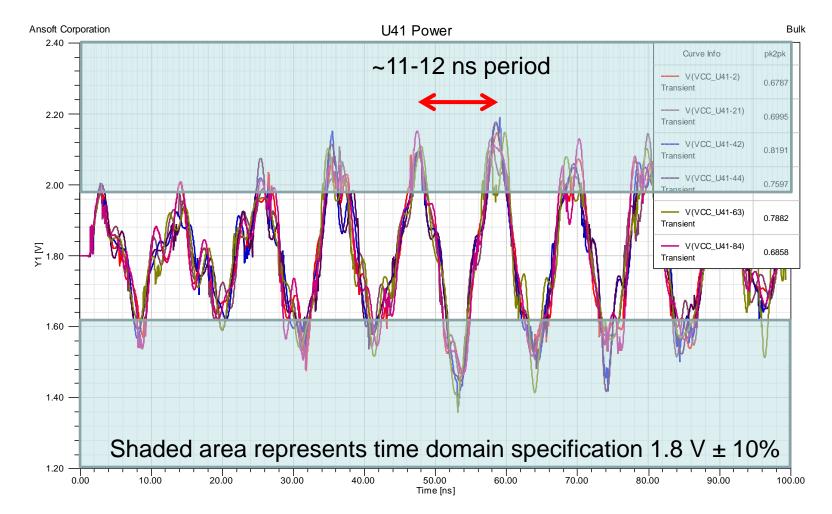

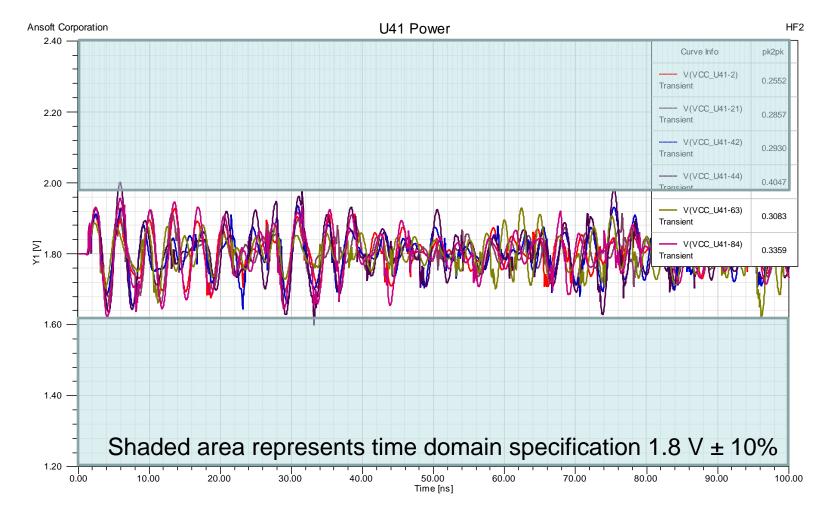

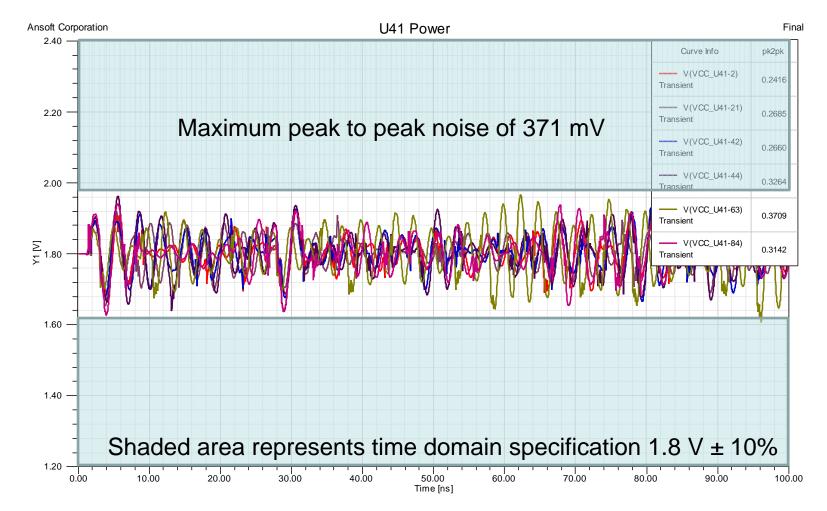

# **Time Domain PDS Targets**

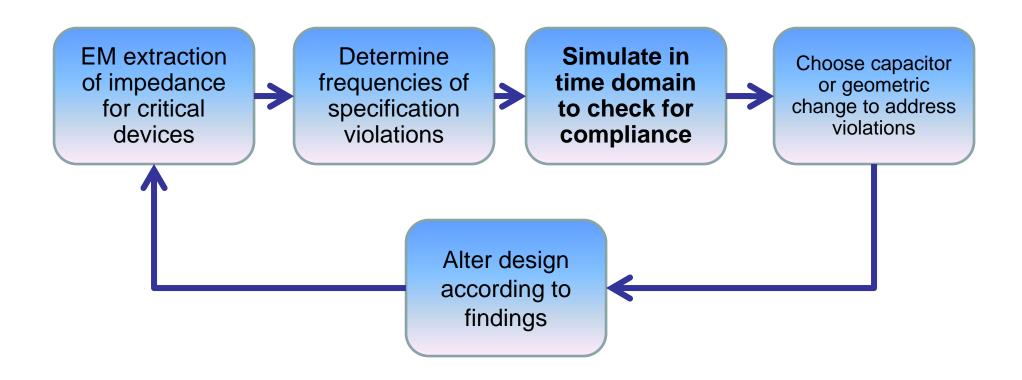

- S-parameters and impedance are calculated in the frequency domain

- Device specifications are typically given in the time domain

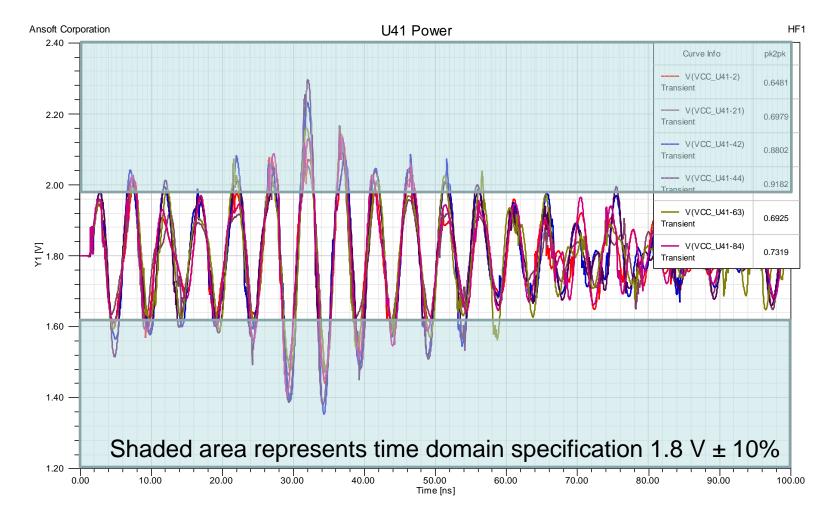

- Example: maximum VCC excursion 10% of nominal value

- 1.8 V VCC has an allowable range of 1.62 V to 1.98 V

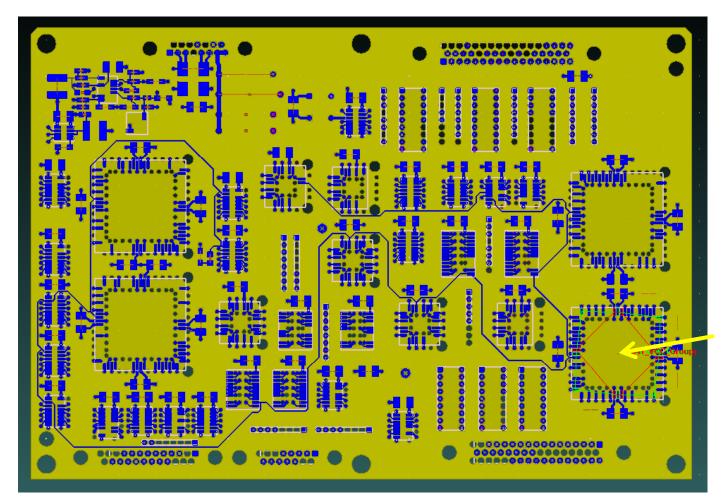

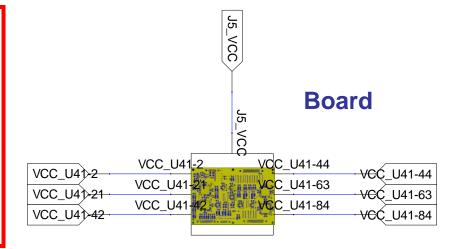

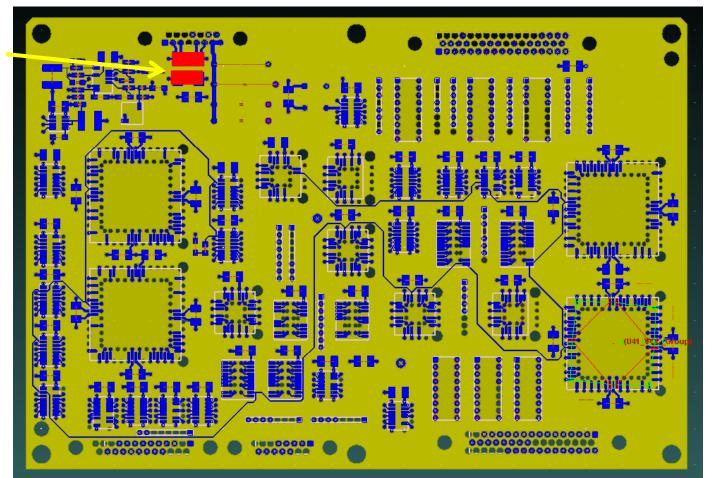

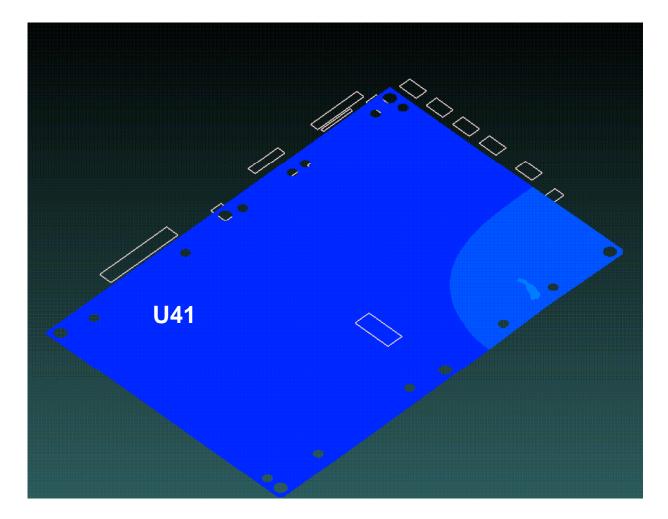

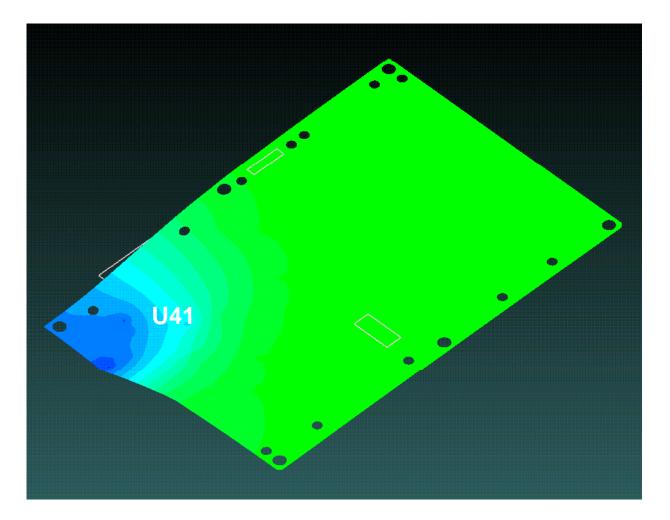

#### **Board Imported from Layout**

Measuring impedance at the six VCC pins on U41

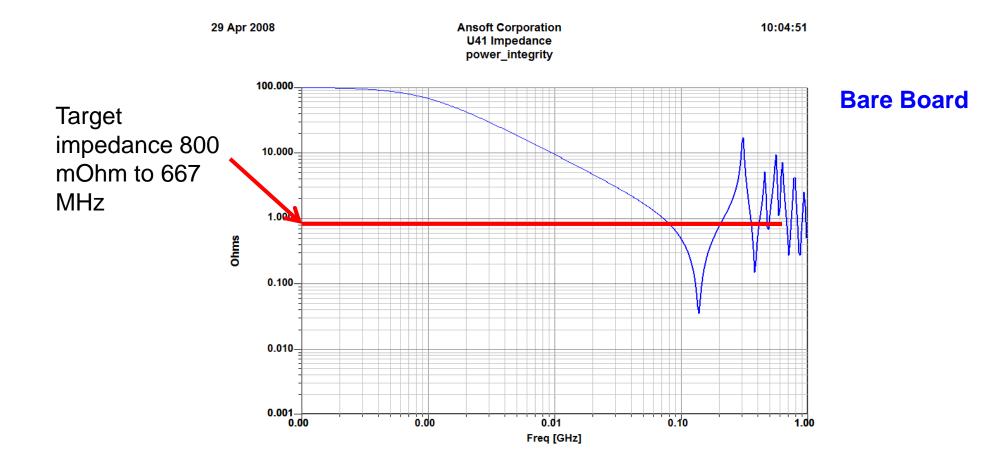

#### **Defining the Target Impedance**

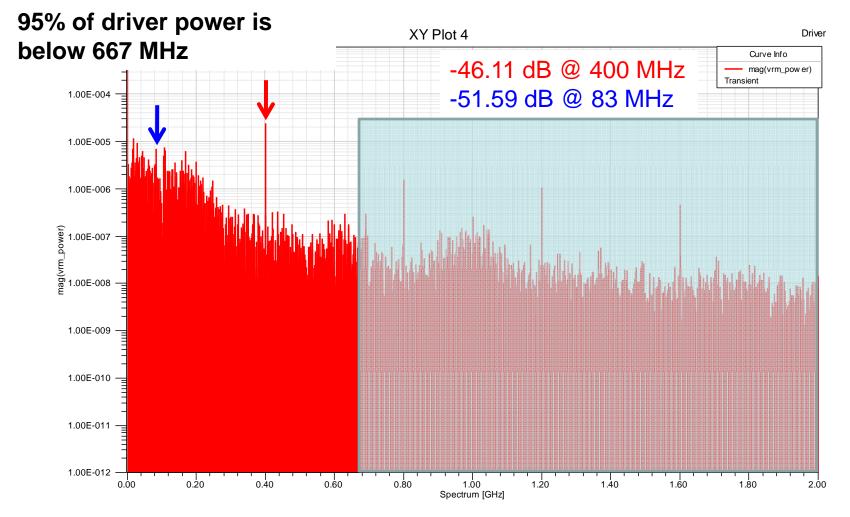

- To define the target impedance we need to consider two factors:

- Peak current

- Determines maximum impedance

- Spectral power

- Determines cutoff frequency

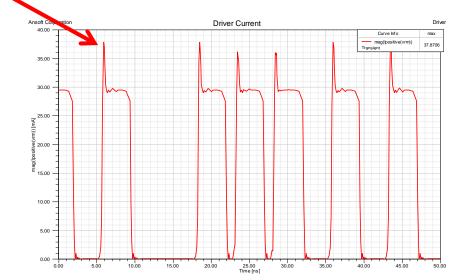

### **Peak Current**

- Peak current 37.87 mA

- Six drivers and 0.18 V maximum voltage swing:

$$\frac{0.18 \,\mathrm{V}}{6(37.87 \,\mathrm{mA})} = 800 \,\mathrm{m}\Omega$$

### **Driver Spectrum**

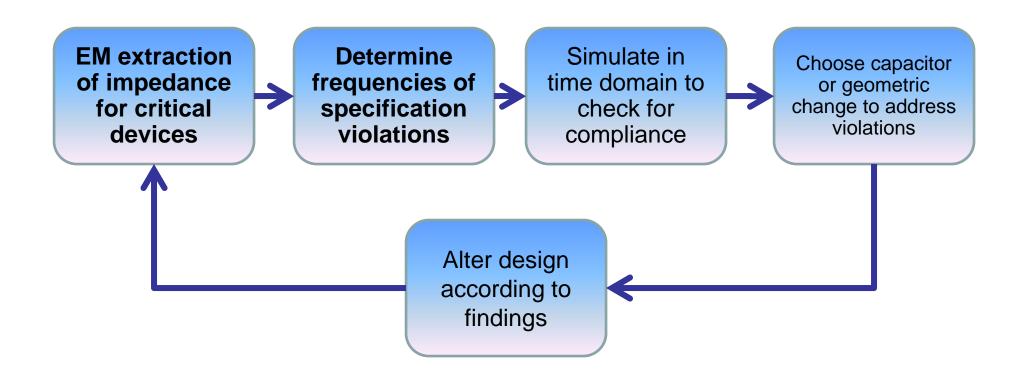

#### **Bare Board**

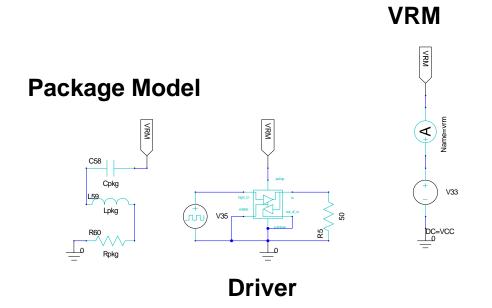

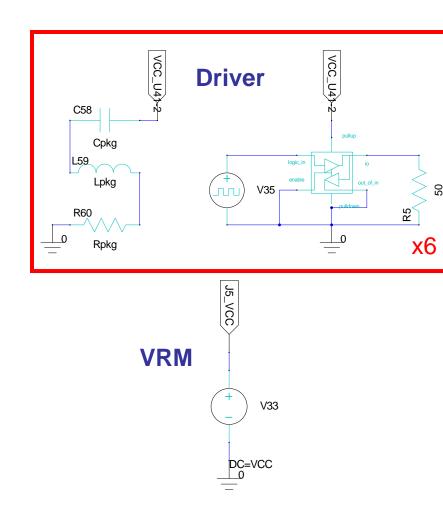

### **Time Domain Schematic**

800 Mbps data rate

DDR2 IBIS driver into ideal termination used as load for PDS

Package decoupling modeled using a capacitor w/ ESR, ESL

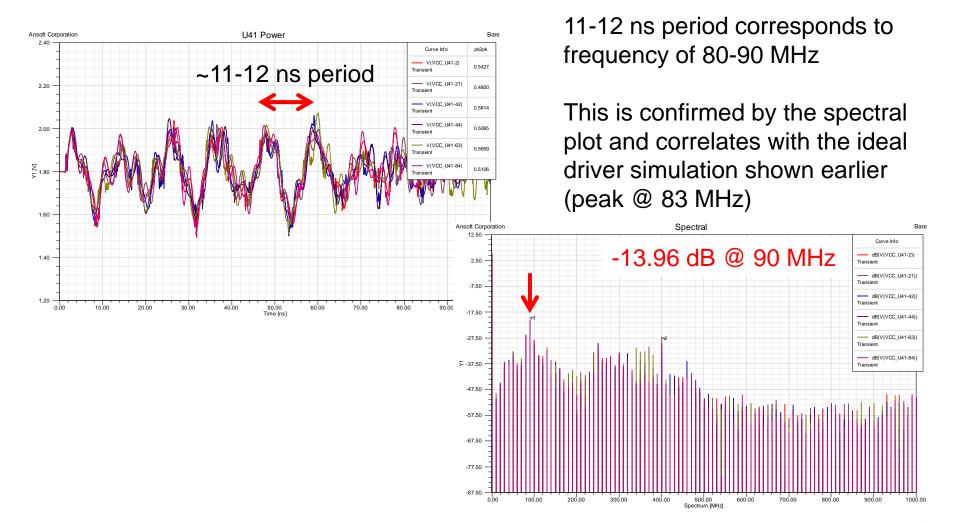

# **Switching Power Noise**

### **Spectral Analysis**

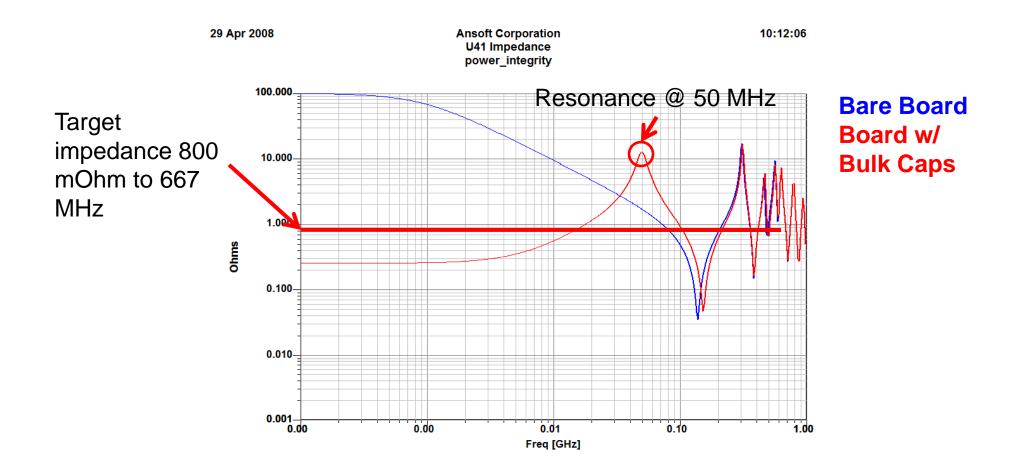

### **Adding Bulk Capacitors**

Added two 47 uF capacitors as specified by VRM manufacturer

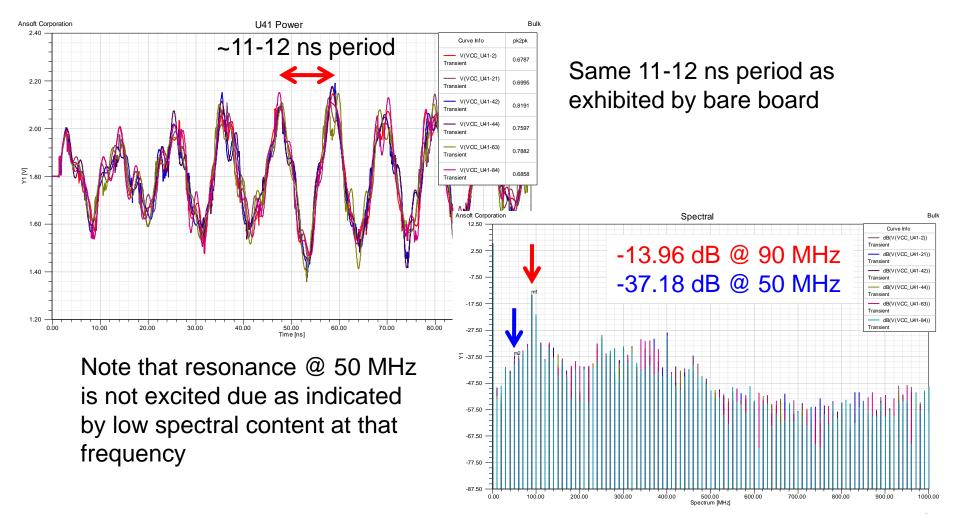

#### **Bare Board vs. Bulk Capacitors**

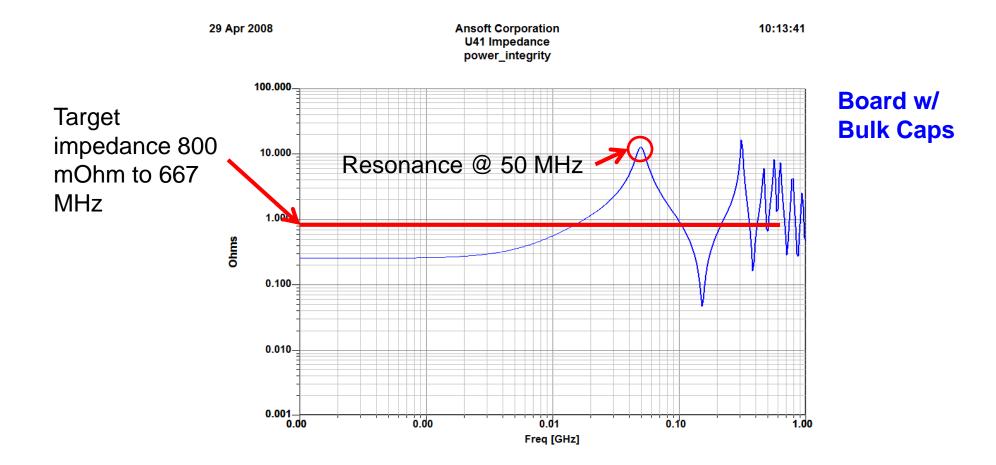

### **Bulk Capacitors**

# **Switching Power Noise**

### **Spectral Analysis**

#### **Resonance at 50 MHz**

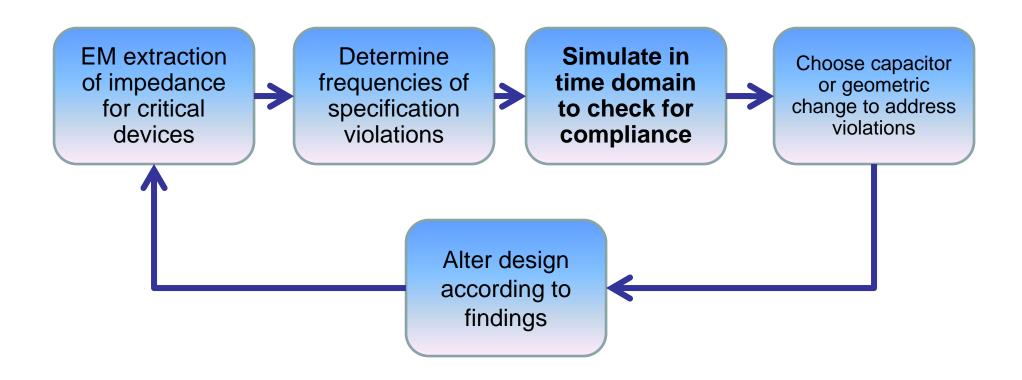

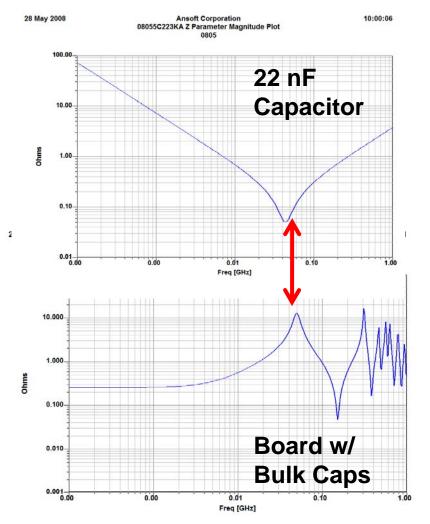

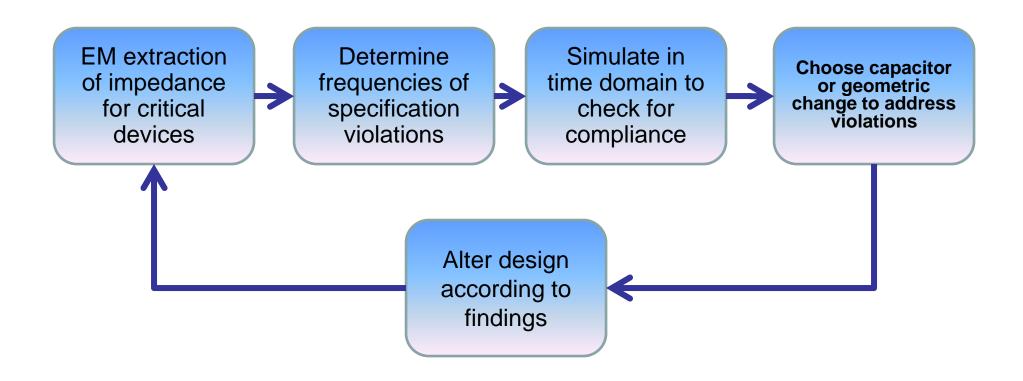

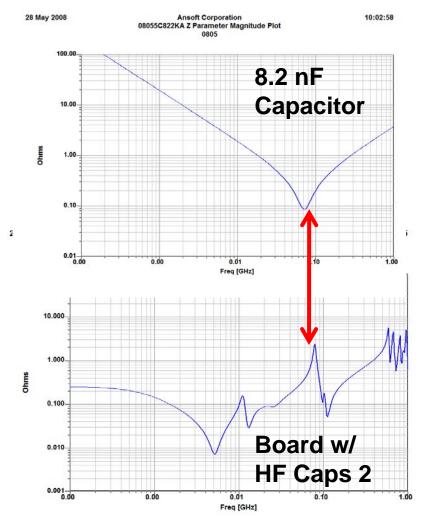

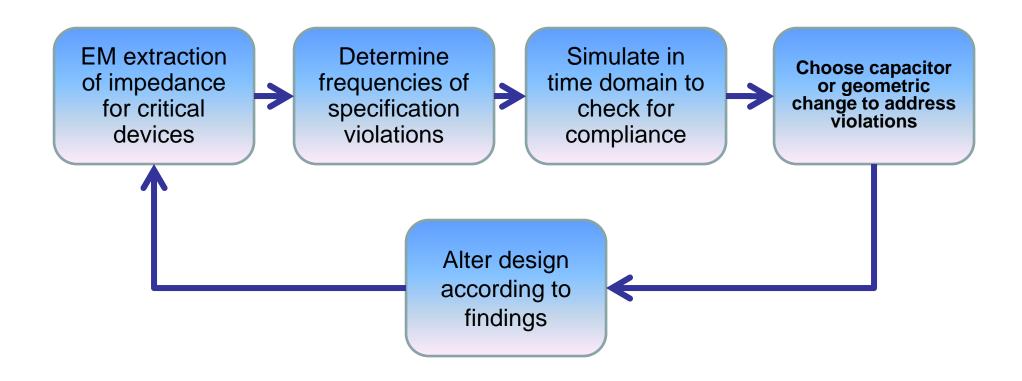

# **Choosing a Capacitor**

To reduce the effect of a resonance, choose a capacitor with a low impedance at the resonant frequency

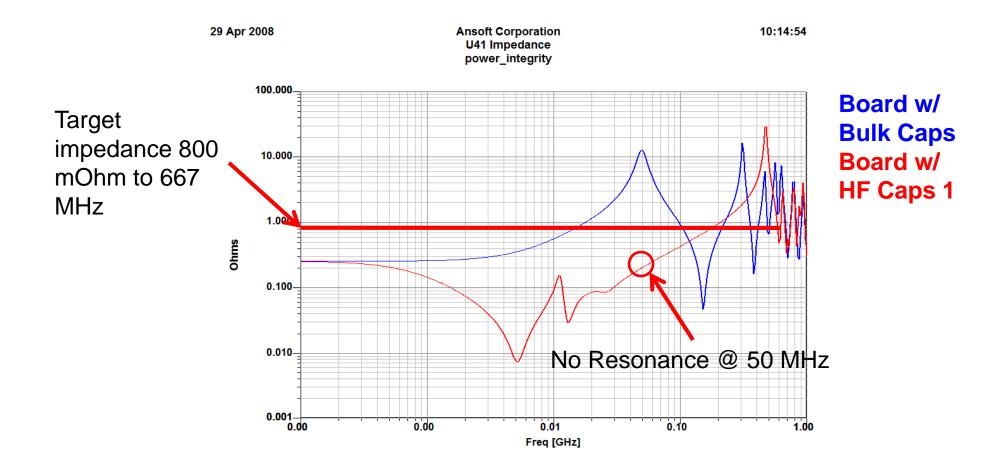

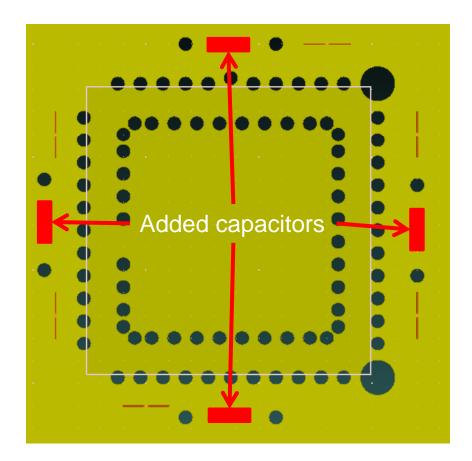

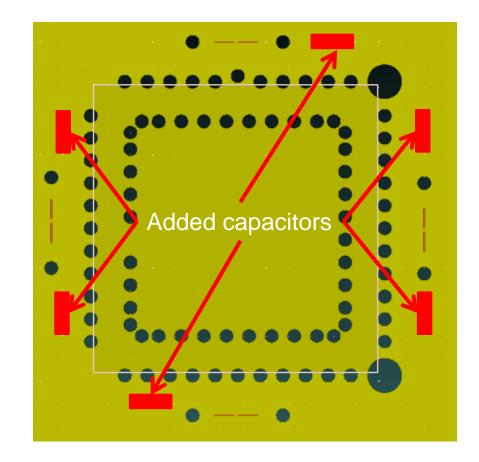

### **Added HF Capacitors**

52 20 nF capacitors were added across the board to reduce high-frequency impedance and to cancel resonance at 50 MHz

### **Bulk vs. HF Capacitors 1**

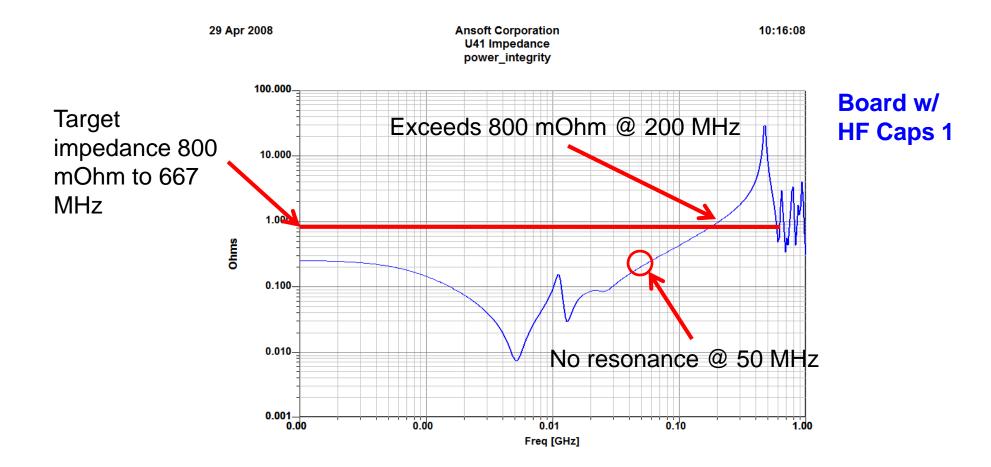

### **HF Capacitors 1**

## **Switching Power Noise**

# **Extending Low Impedance**

- 10 1.2 nF capacitors were added across the board to extend minimum highfrequency impedance

- 1.2 nF capacitor was chosen due to low impedance at 200 MHz

- 4 of these were located near U41

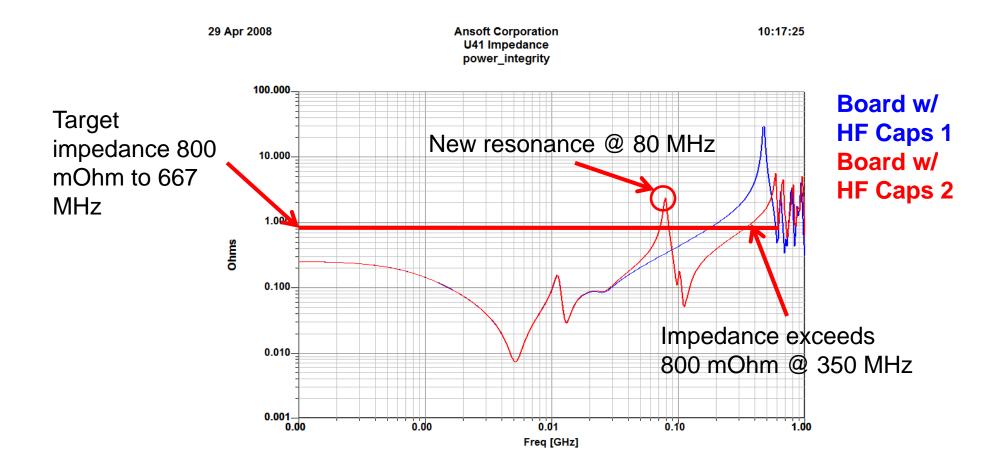

#### HF 1 vs. HF 2

#### **HF 2**

## **Switching Power Noise**

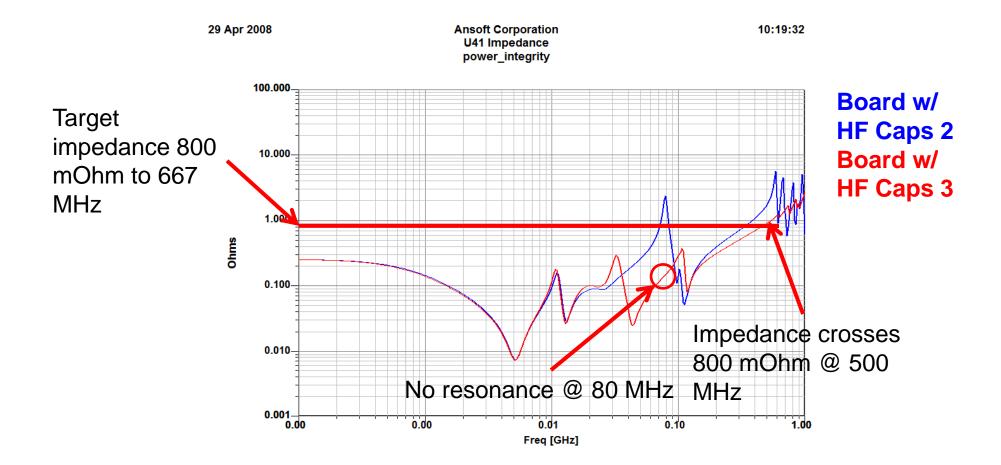

#### **Resonance at 80 MHz**

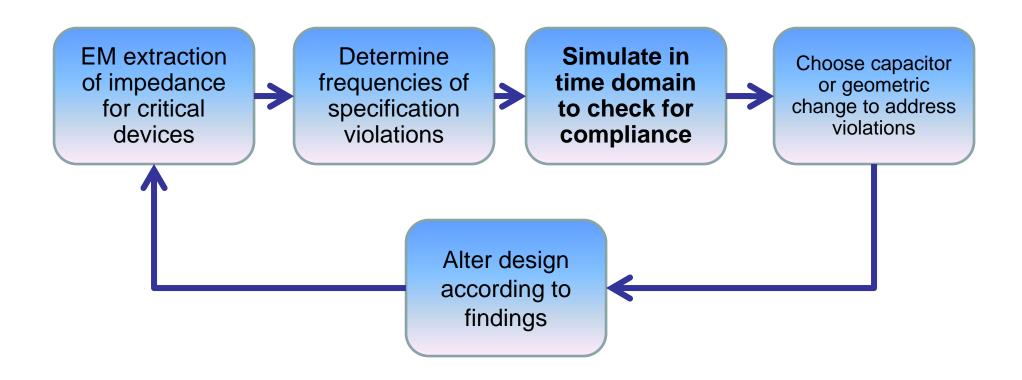

#### **Removing a Resonance**

Six 8 nF capacitors were added near U41 to cancel resonance at 80 MHz

## **Choosing a Capacitor**

To reduce the effect of a resonance, choose a capacitor with a low impedance at the resonant frequency

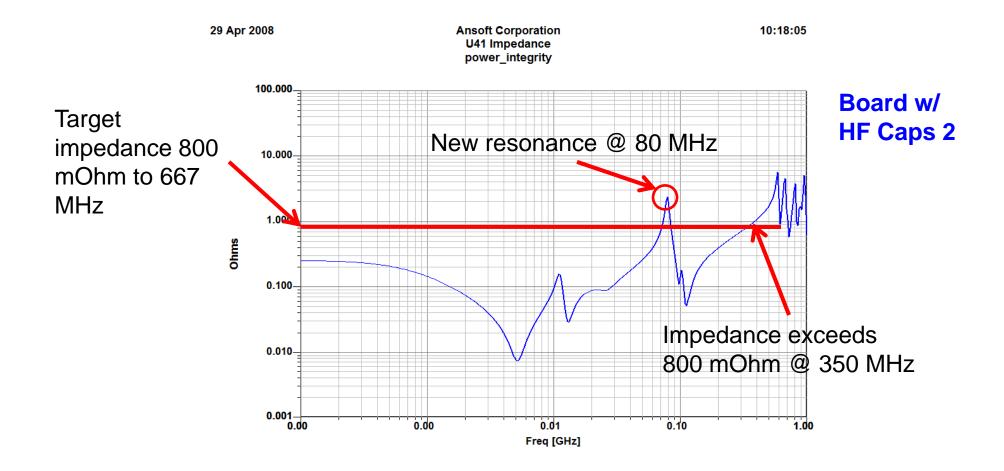

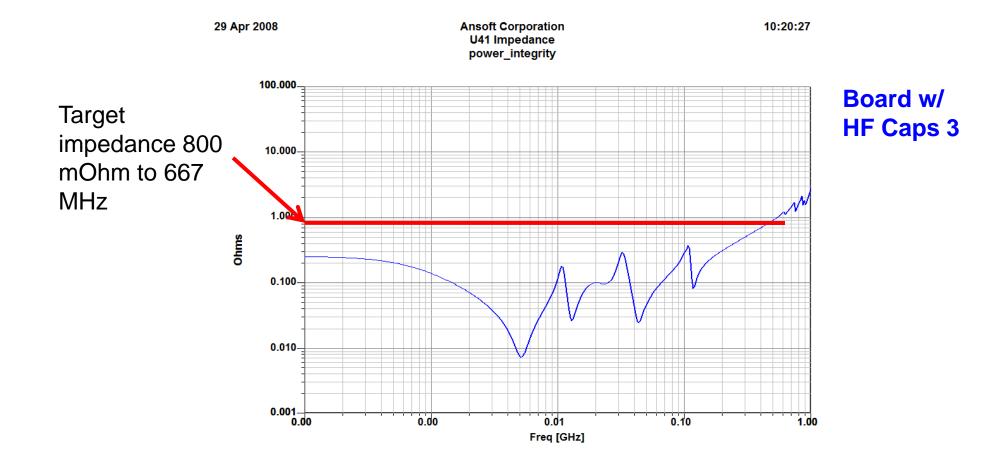

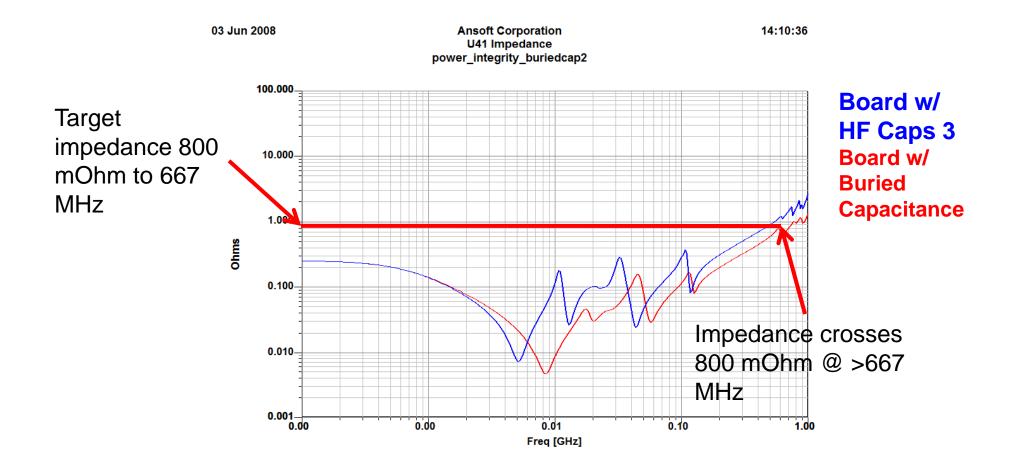

#### HF 2 vs. HF 3

#### **HF 3**

# **Switching Power Noise**

#### **Buried Capacitance**

- Due to parasitic inductance it will be impossible to further decouple the board with capacitors

- Using a thinner dielectric layer between power and ground planes introduces additional capacitance and reduces high frequency impedance

Capacitance of parallel plates:

$$C =$$

$$C = \varepsilon \frac{A}{d}$$

#### HF 3 vs. Buried Capacitance

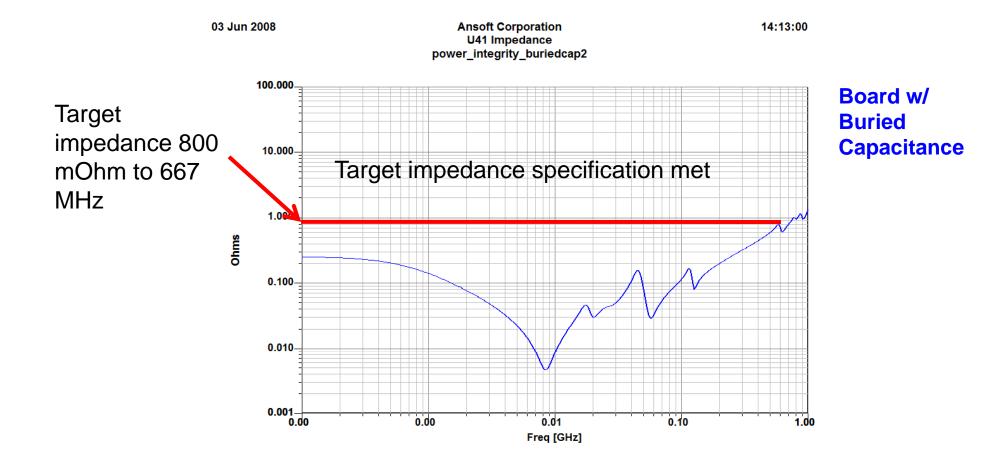

#### **Buried Capacitance**

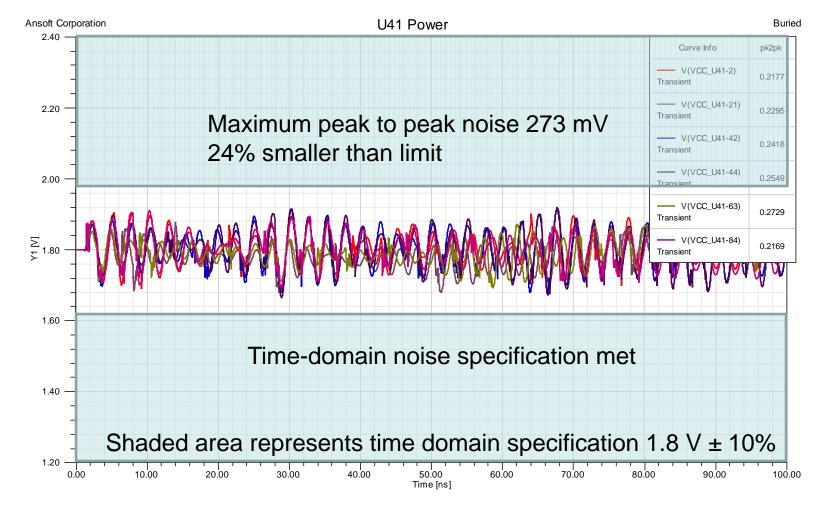

# **Switching Power Noise**

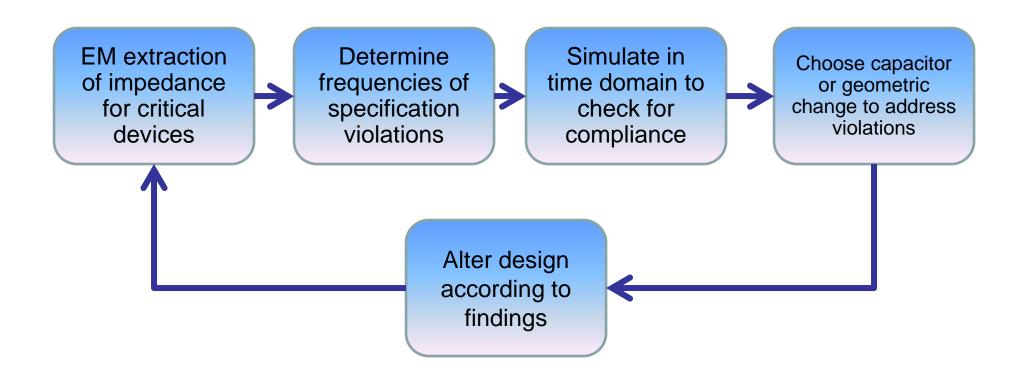

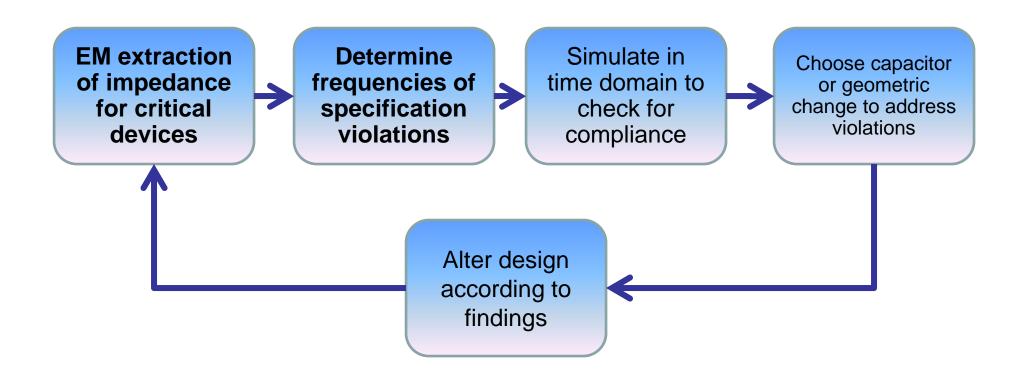

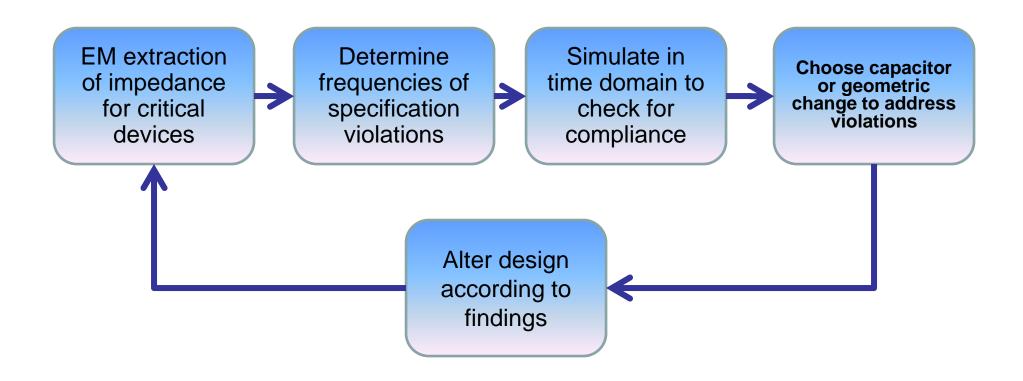

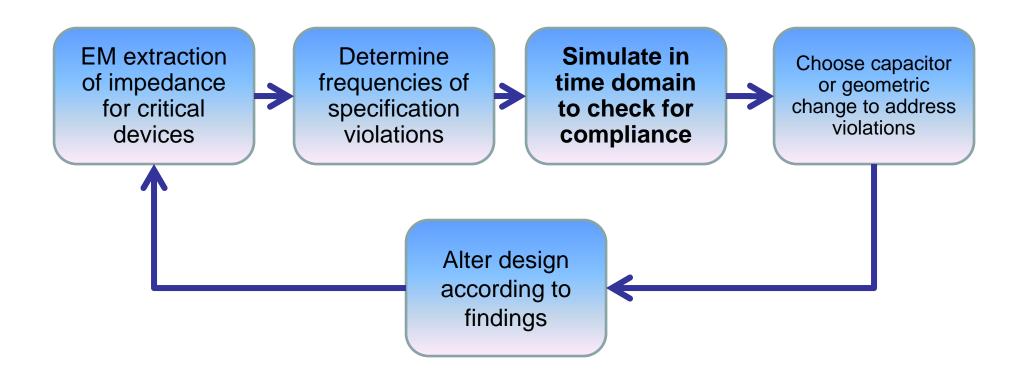

#### Conclusion

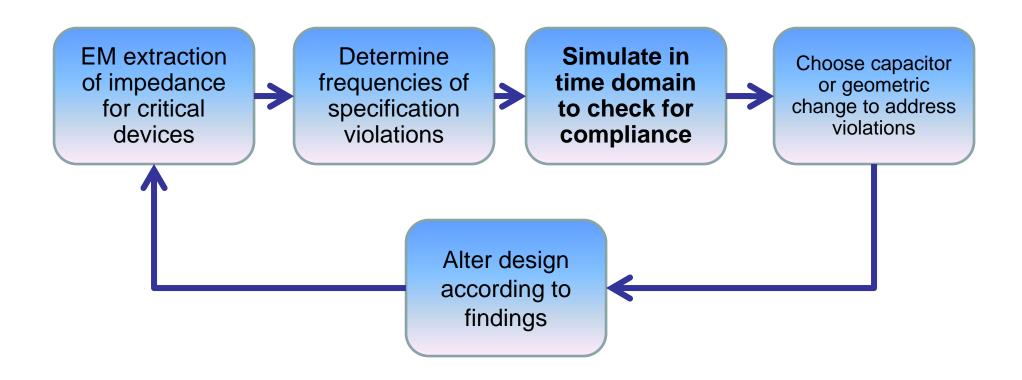

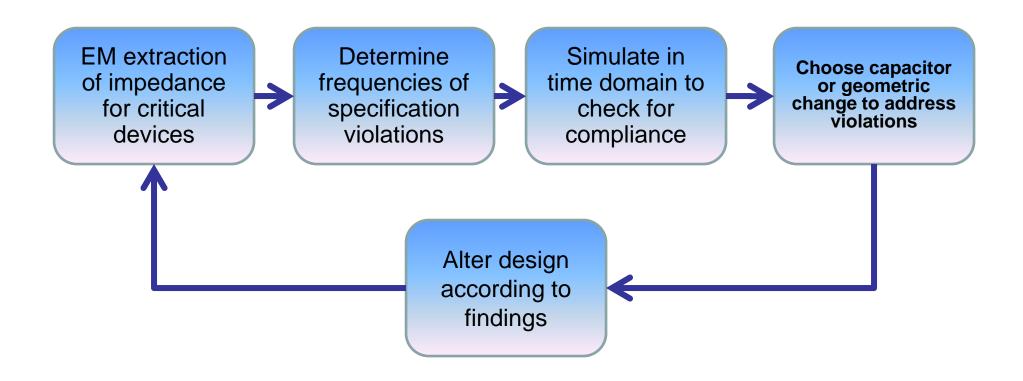

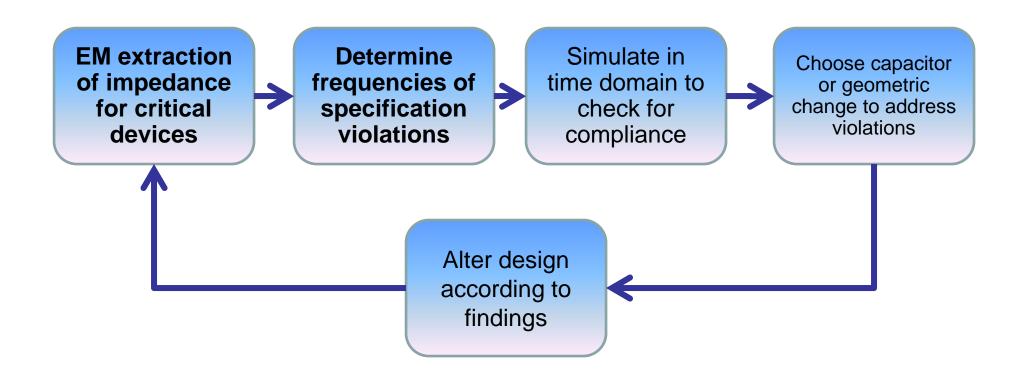

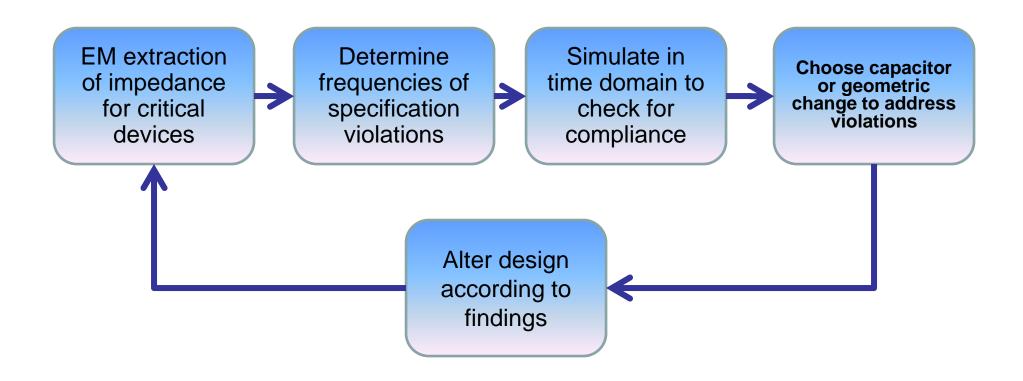

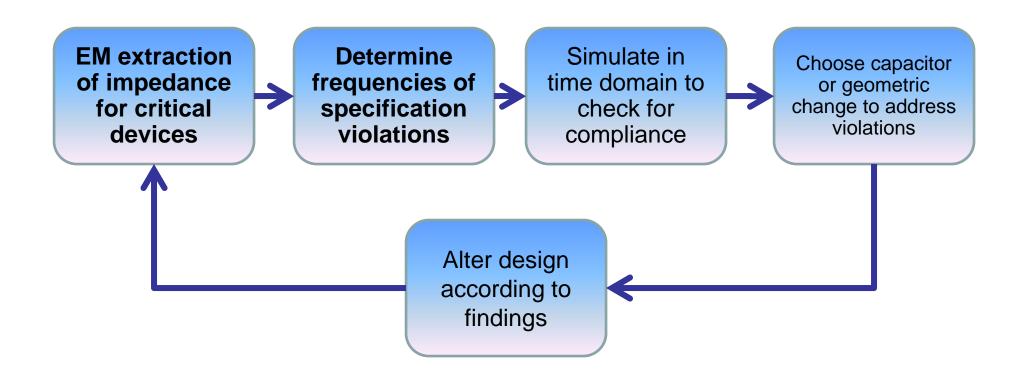

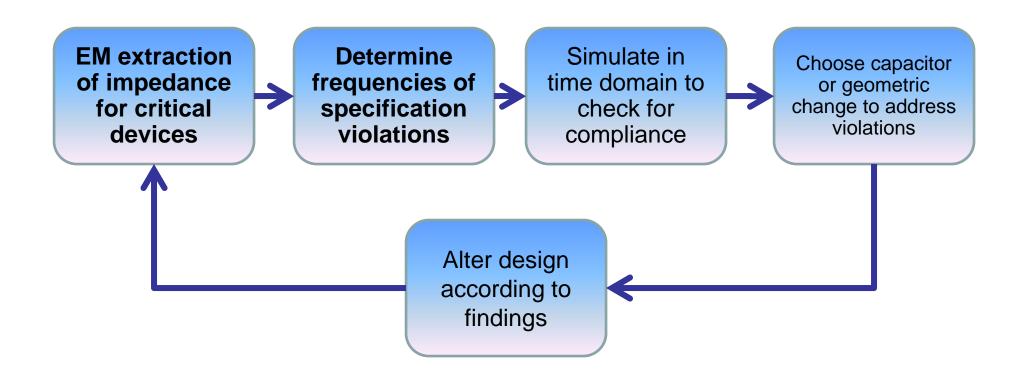

- Ansoft software allows PCB engineers to design effective decoupling solutions for their PCBs

- Impedance and resonant mode simulations connect the frequency domain to the spatial domain and allow selection of capacitor value and placement

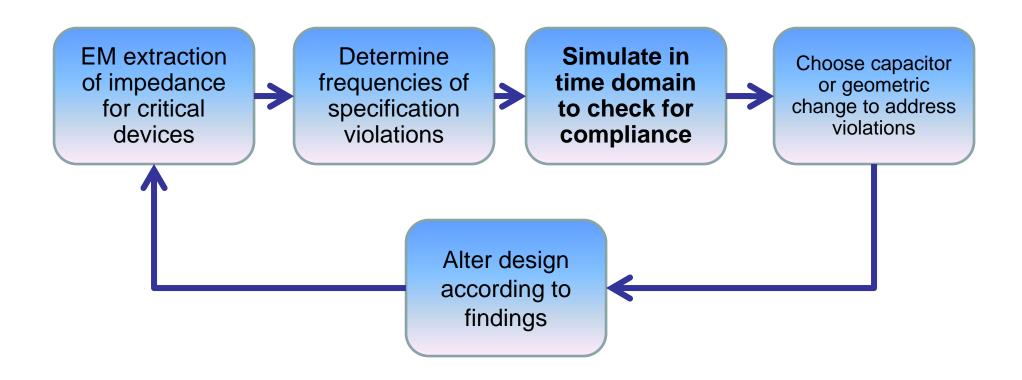

- Frequency domain extractions are useful for quickly optimizing PDS designs, but time domain simulations are necessary to ensure compliance with device specs