## **Inspiring Engineering**

### **EMI Driven by PI**

#### <u>Outline</u>

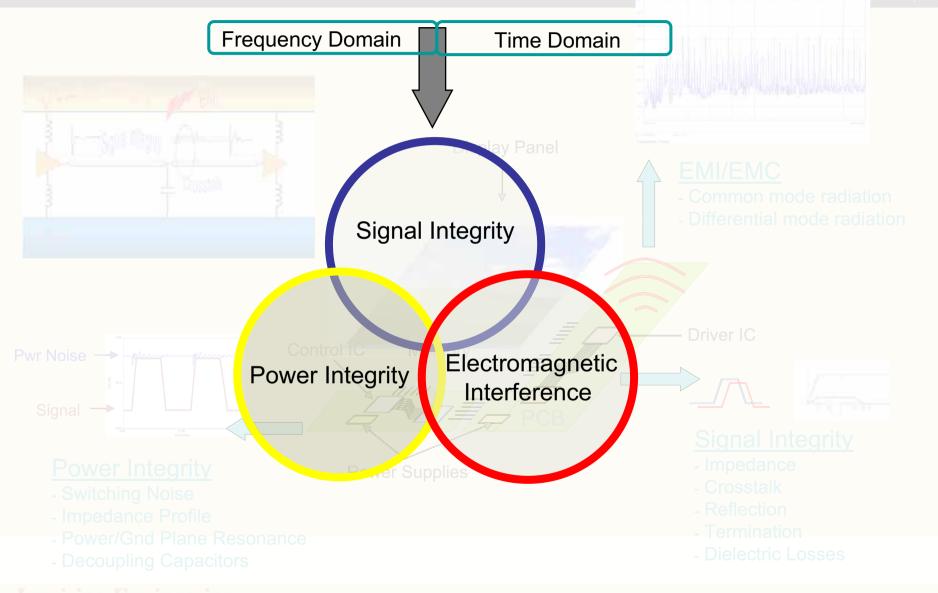

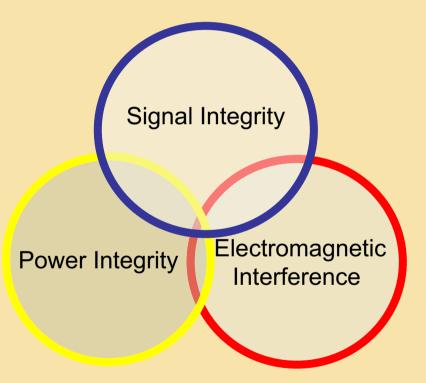

- SI + PI = EMI

- These disciplines are no longer independent of each other

- Fundamentals of EMI

- Where does it come from and how is it minimized

- Five Step EMC Design Flow

- Power Integrity design methodology to reduce EMI

- Fundamentals of Power Integrity

- Design Process to meet design specs in the Time and Frequency domain

- 2<sup>nd</sup> Presentation on EMI Driven by SI

- Fundamentals of Signal Integrity

- Crosstalk is the main contributor to EMI

- Case studies that show perils of crosstalk in real world designs

### **SI/PI/EMI Design Overview**

© 2008 Ansoft LLC. All rights reserved

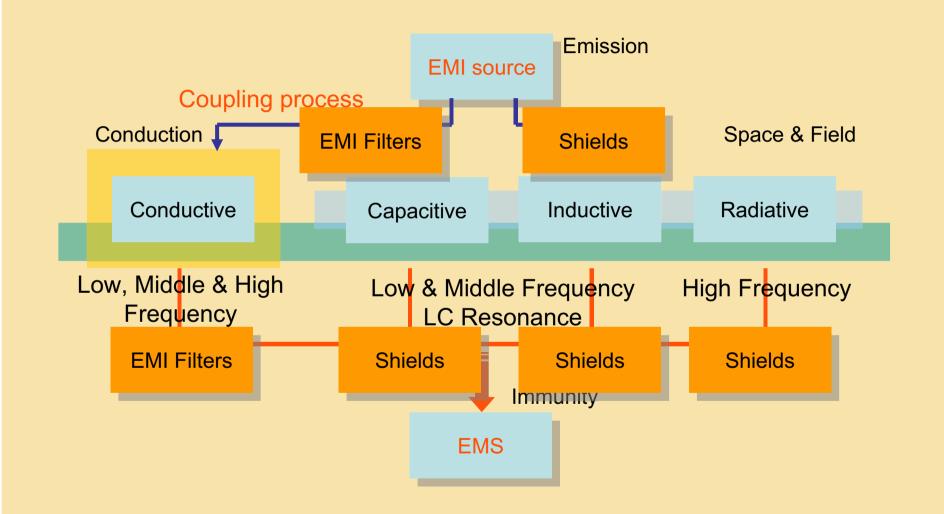

### **Three Basic Elements of EMC**

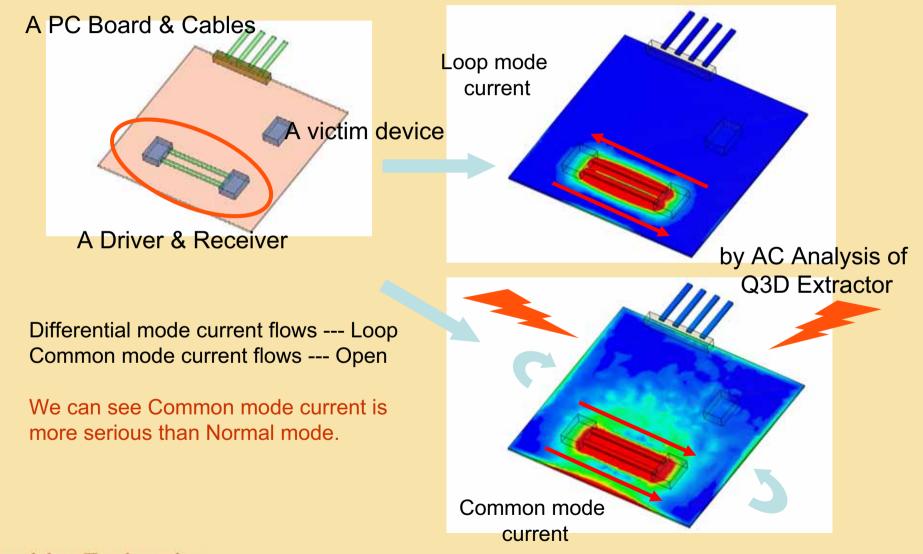

#### Loop Mode & Common Mode Noise

#### **Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

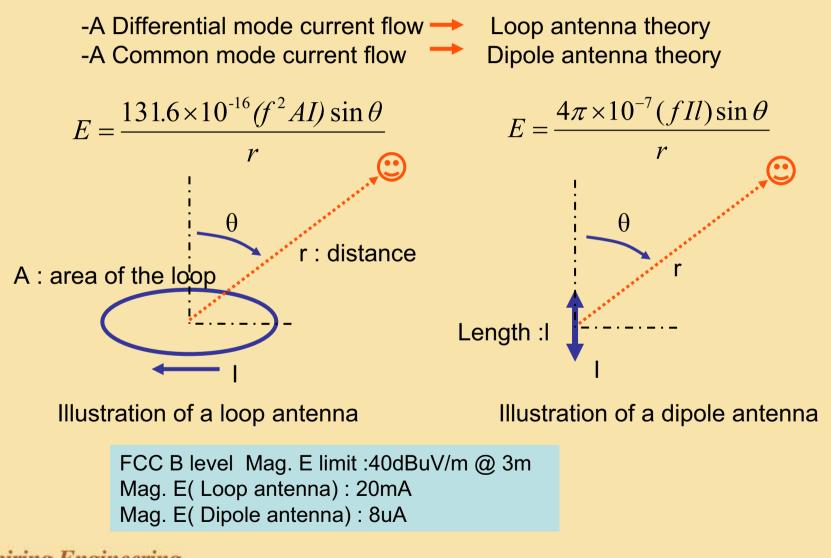

### Antenna theory

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

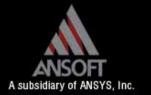

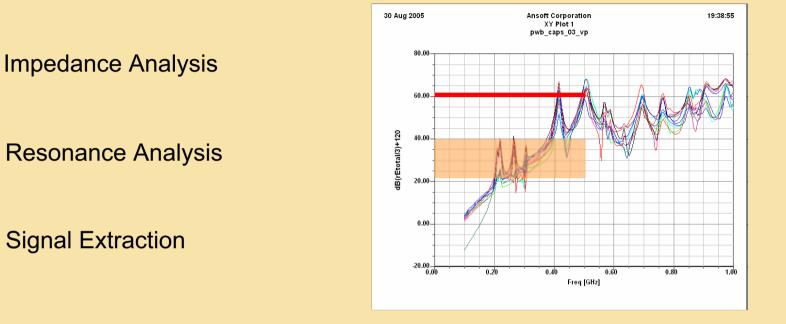

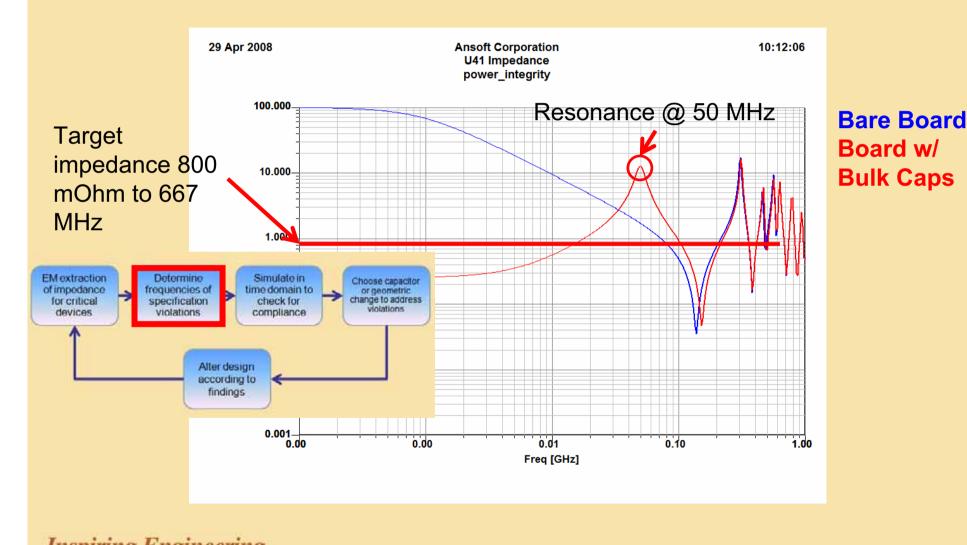

#### Impedance Analysis

**Resonance Analysis**

#### Planes deliver power to ICs and return path for signal

Ensure that Plane impedance is smooth and low over broad frequency range

**Signal Extraction**

**Emissions Analysis**

**Enclosure Simulation**

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

Impedance Analysis

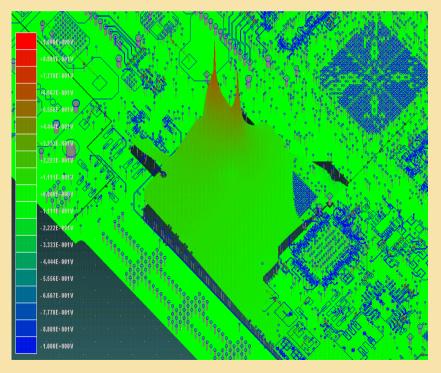

**Resonance Analysis**

**Signal Extraction**

**Emissions Analysis**

**Enclosure Simulation**

Resonances indicate areas of high impedance and EMI potential

## Ensure power planes do not resonant in critical locations

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

Impedance Analysis

**Resonance Analysis**

Signal Extraction

**Emissions Analysis**

**Enclosure Simulation**

If signal is not at the receiver, it went somewhere else

Ensure clean signal transmission and good return path for critical nets

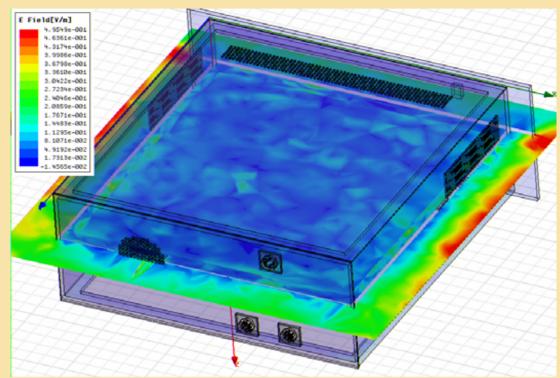

**Emissions Analysis**

Non-ideal planes and tight routing can lead to unintentional signals

**Enclosure Simulation**

Ensure there are no unintentional radiators

Impedance Analysis

**Resonance Analysis**

Signal Extraction

**Emissions Analysis**

**Enclosure Simulation**

Real enclosures are non-ideal and can pass radiation

Ensure minimal radiation from PCB escapes the chassis holes

Inspiring Engineering © 2008 Ansoft, LLC All rights reserved.

### **PI Methodology**

#### **Power Integrity – A Case Study**

- Active devices require clean power to operate correctly

- Power distribution system (PDS) design engineers must ensure that all parts receive voltage between certain limits and that noise is kept sufficiently low

- Today's designs with many separate power domains of high current and low voltage devices complicate power integrity analysis

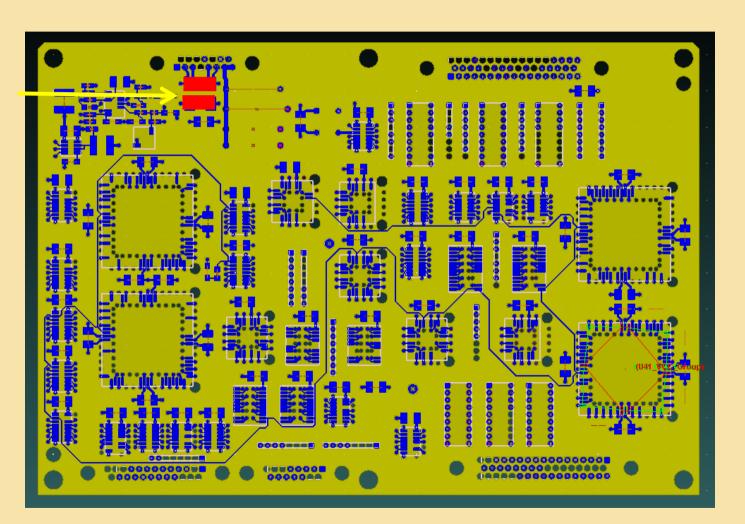

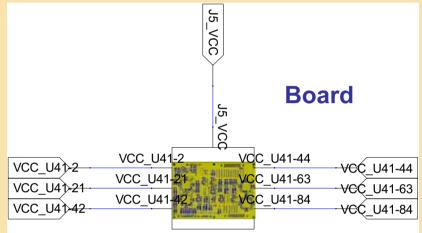

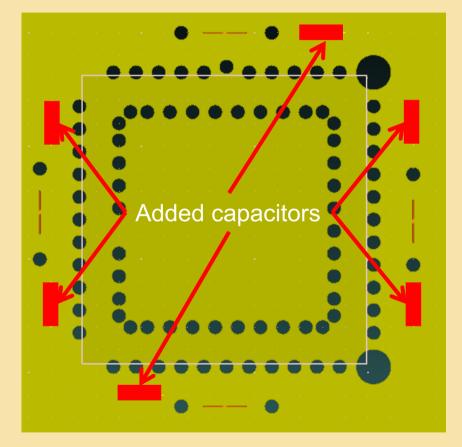

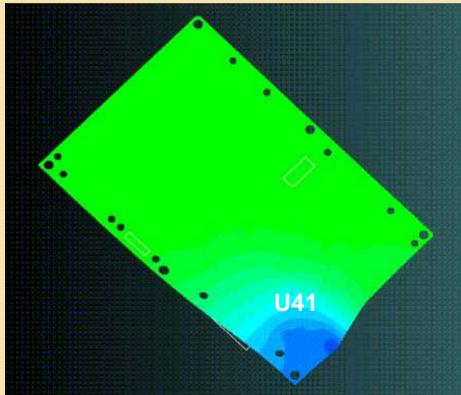

#### **Board Imported from Layout**

VRM 0000000000 0000008 eleccoccocce

Measuring impedance at the six VCC pins on U41

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

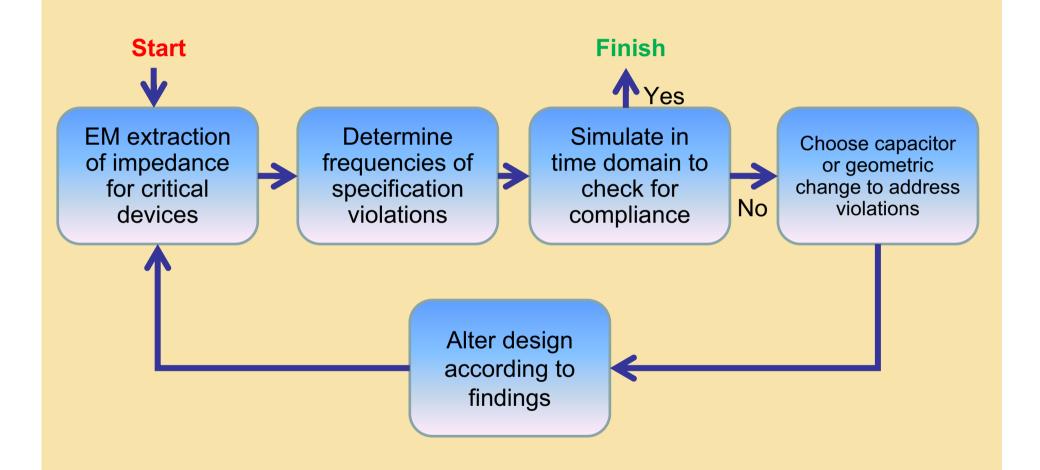

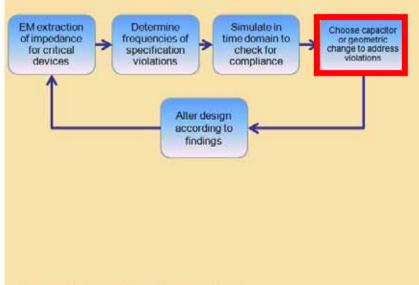

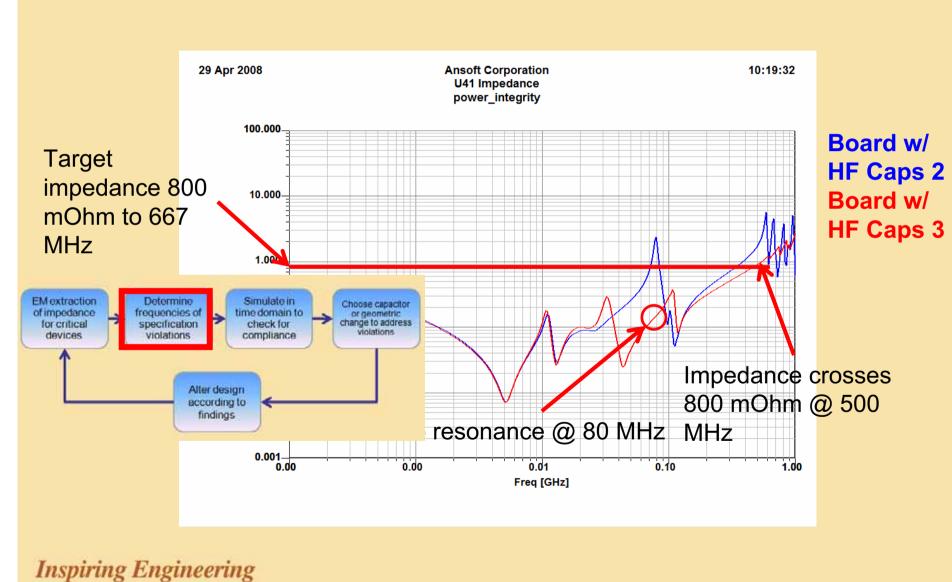

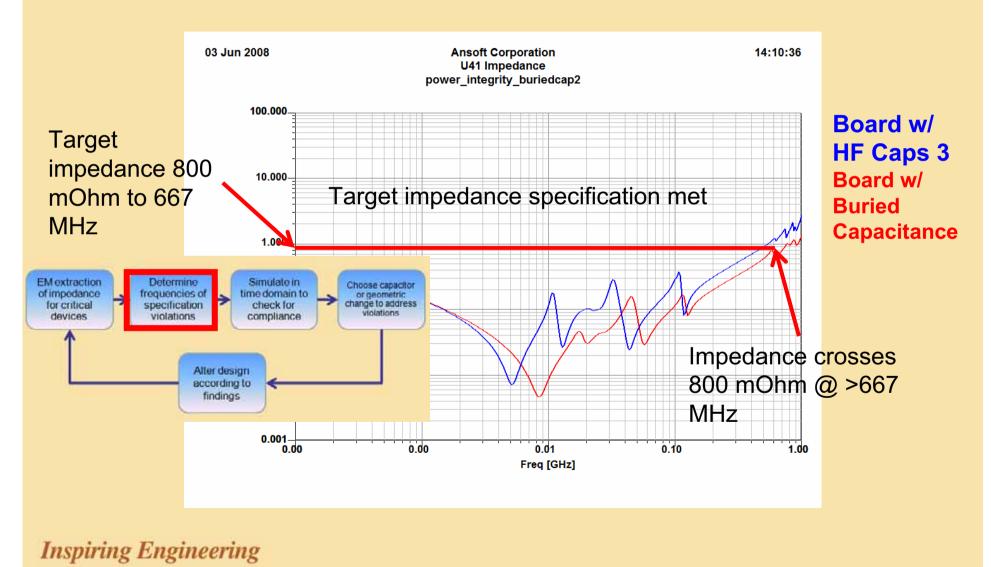

#### **PDS Design Flow**

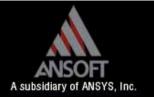

#### **Frequency Domain PDS Targets**

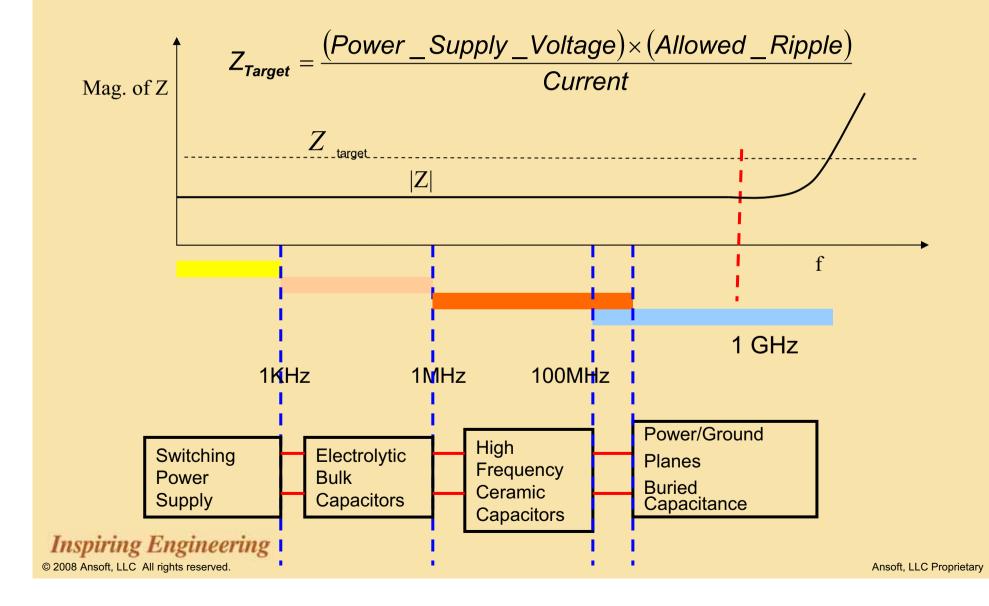

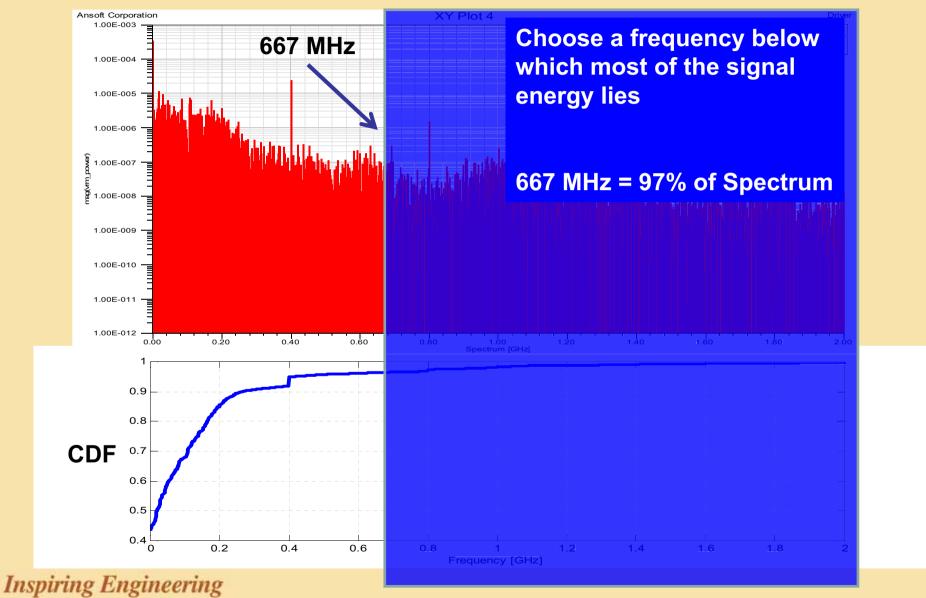

### **Defining the Target Impedance**

Driver

- To define the target impedance we need to consider two factors:

- Peak current

- Determines maximum impedance

- Spectral power

- Determines cutoff frequency

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

#### **Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

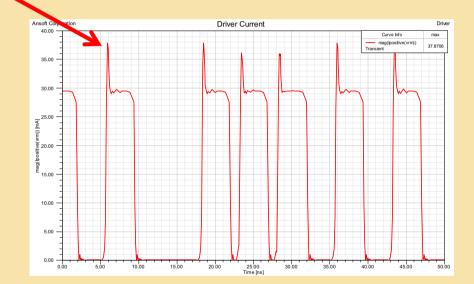

#### **Peak Current**

- Peak driver current 37.87 mA

- Example:

- Six drivers and 0.18 V maximum voltage swing:

$$\frac{0.18\,\mathrm{V}}{6(37.87\,\mathrm{mA})} = 800\,\mathrm{m}\Omega$$

#### **Driver Spectrum**

© 2008 Ansoft, LLC All rights reserved.

#### **Power Integrity Investigation**

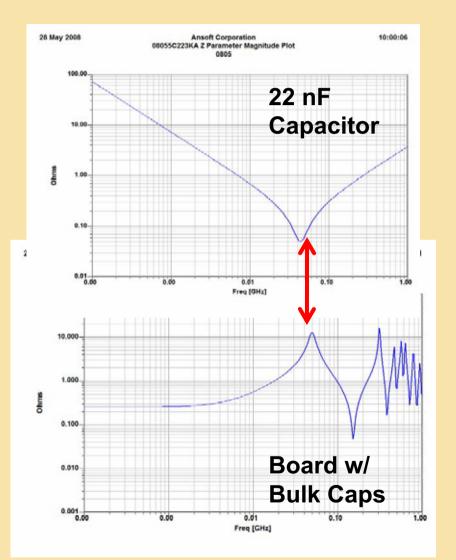

Added two bulk 47 uF capacitors as specified by VRM manufacturer

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

#### **Bare Board vs. Bulk Capacitors**

© 2008 Ansoft, LLC All rights reserved.

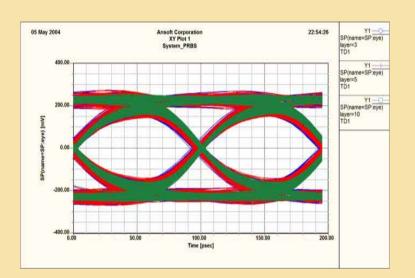

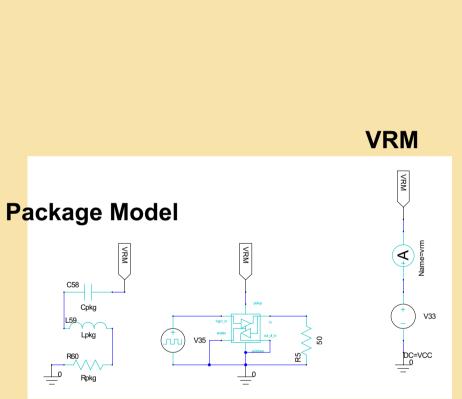

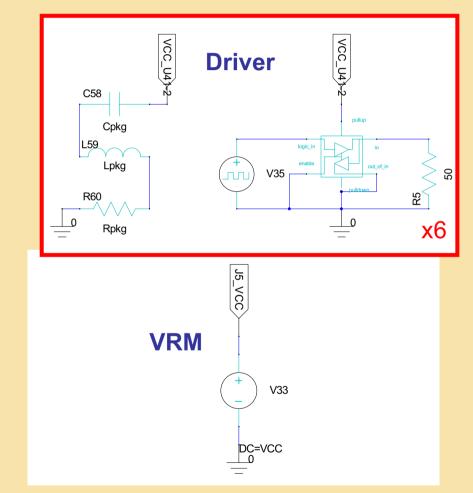

#### **Time Domain Schematic**

800 Mbps data rate

DDR2 IBIS driver into ideal termination used as load for PDS

Package decoupling modeled using a capacitor w/ ESR, ESL

#### **Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

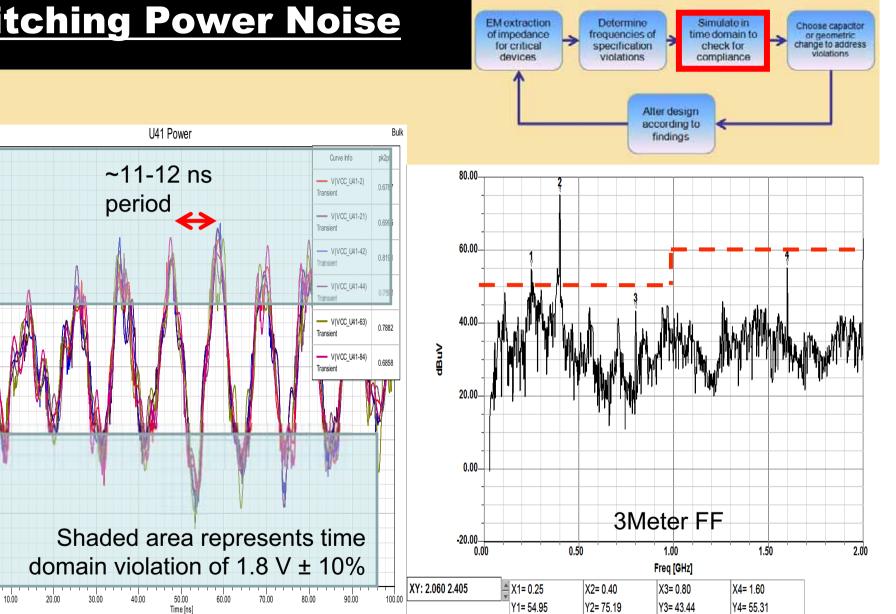

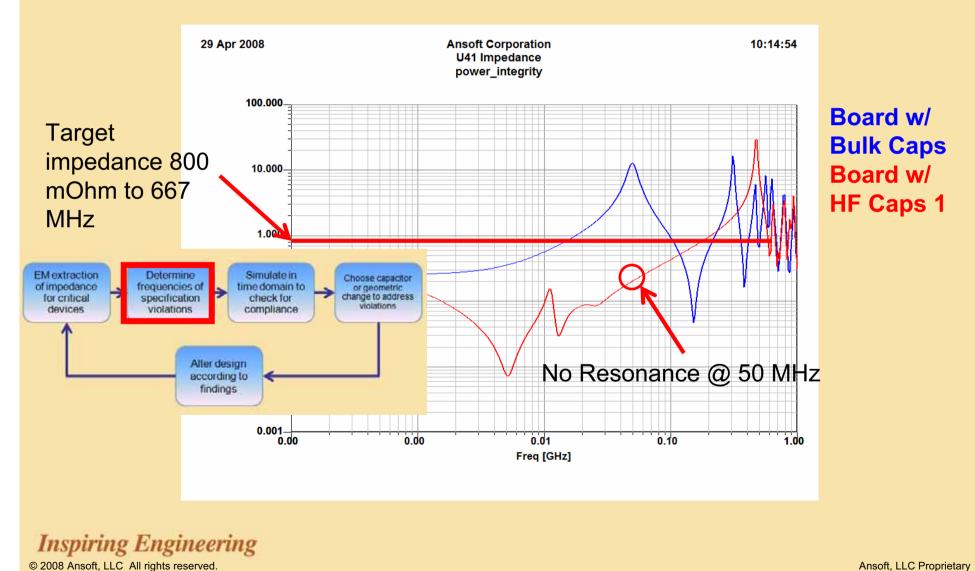

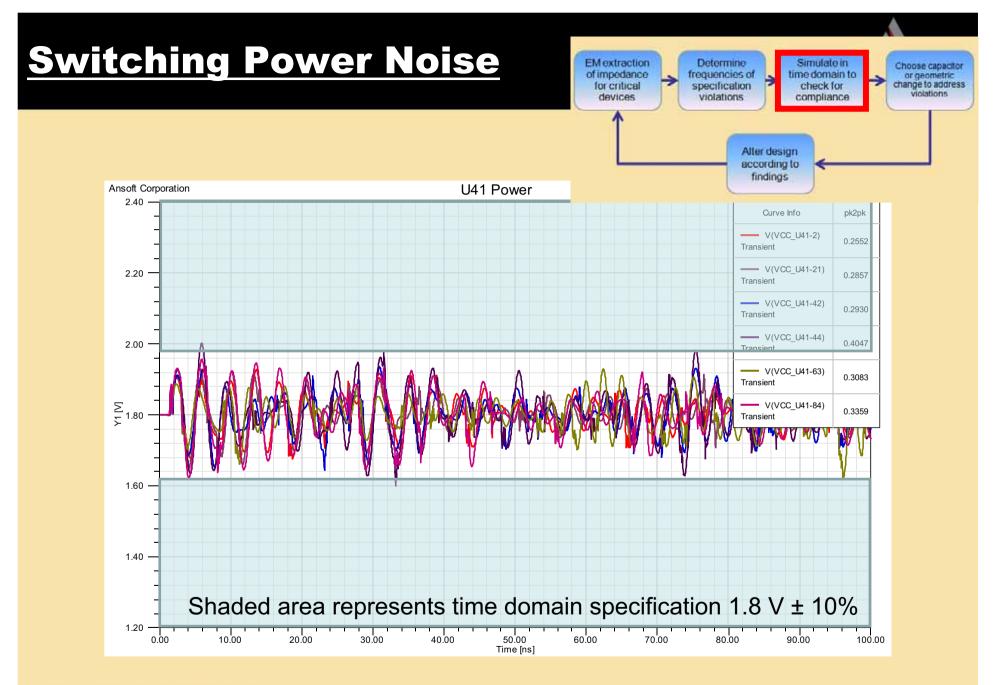

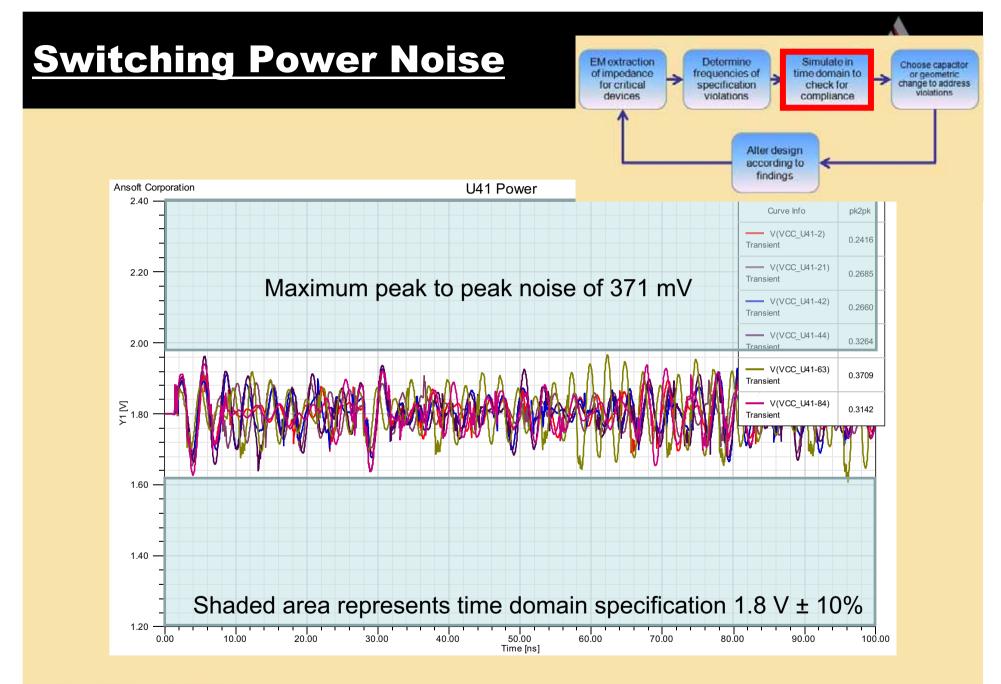

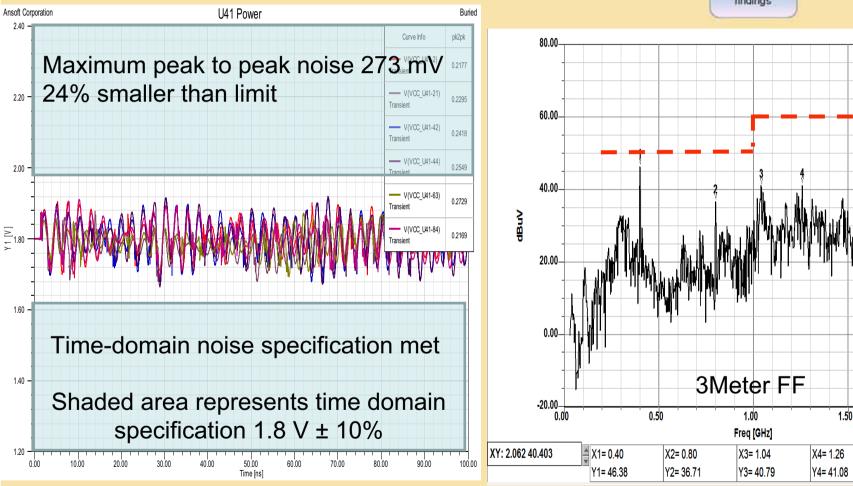

## **Switching Power Noise**

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

Ansoft Corporation

2.40

2.20 -

2.00

Y 1 [V]

1.60

1.40

1.20 -

0.00

### **Choosing a Decoupling Capacitor**

To reduce the effect of a resonance, choose a capacitor with a low impedance at the resonant frequency

#### **Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

#### **Bulk vs. HF Capacitors 1**

© 2008 Ansoft, LLC All rights reserved.

#### Inspiring Engineering © 2008 Ansoft, LLC All rights reserved.

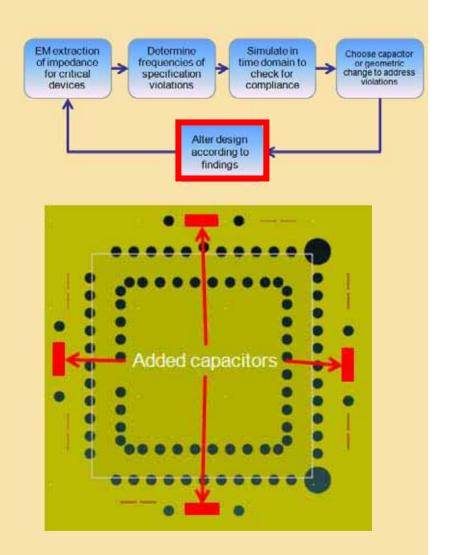

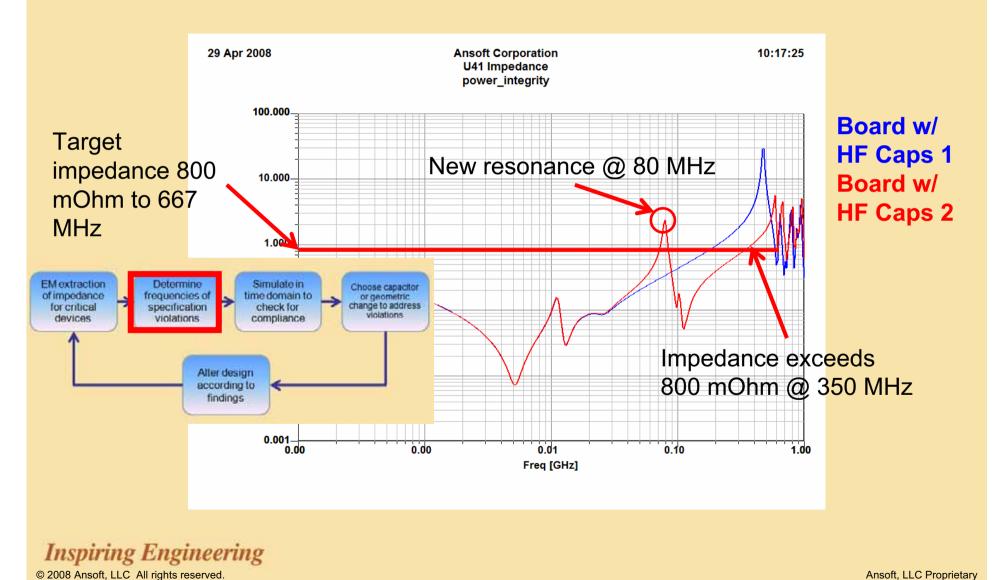

### **Extending Low Impedance**

- 10 1.2 nF capacitors were added across the board to extend minimum high-frequency impedance

- 1.2 nF capacitor was chosen due to low impedance at 200 MHz

- 4 of these were located near U41

**HF 1 vs. HF 2**

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

#### **Removing a Resonance**

Six 8 nF capacitors were added near U41 to cancel resonance at 80 MHz

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

© 2008 Ansoft, LLC All rights reserved.

#### <u>HF 2 vs. HF 3</u>

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.

#### **Buried Capacitance**

- Due to parasitic inductance it is impossible to decouple the board with capacitors at frequencies greater than a few hundred MHz

- Using a thinner dielectric layer between power and ground planes introduces additional capacitance and reduces high frequency impedance

Capacitance of parallel plates:

$$C = \varepsilon \frac{A}{d}$$

#### HF 3 vs. Buried Capacitance

© 2008 Ansoft, LLC All rights reserved.

### **Switching Power Noise**

X5= 1.60

Y5= 53.75

2.00

#### <u>Conclusions</u>

- SI / PI / EMI are all based on the same electromagnetic fundamentals and cannot be separated

- Impedance and resonant mode simulations connect the frequency domain to the spatial domain and allow selection of capacitor value and placement

- Frequency domain extractions are useful for quickly optimizing PDS designs, but *time domain* simulations are necessary to ensure compliance with device specs

- Using a single design environment can help reuse the same models for SI/PI/EMI simulations

# Any Questions?

**Inspiring Engineering** © 2008 Ansoft, LLC All rights reserved.