# Far-Field EMI Analysis Methodology and Verification on SSD Boards

Seong-Jin Mun, (Samsung Electronics Inc.)

Jin-Sung Youn (Samsung Electronics Inc.), Kyung-Nam Park (Samsung Electronics Inc.) Jieun Park (Samsung Electronics Inc.), Daehee Lee (Samsung Electronics Inc.) Chan-Seok Hwang (Samsung Electronics Inc.), Jong-Bae Lee (Samsung Electronics Inc.)

#### **SPEAKERS**

#### **Seong-Jin Mun**

*Engineer, Samsung Electronics Inc.* sungj.moon@samsung.com

Received the B.S. degree from Department of Electronic Engineering, Sogang University, Seoul, Korea, in 2010. Since 2010, He has been an engineer with the Semiconductor Business, Samsung Electronics, Korea. His research interests are in the area of signal integrity (SI), power integrity (PI), electromagnetic interference (EMI), thermal integrity (TI) and package/board layout design verification.

#### Agenda

#### Background

- Trends of Data Storage

- Necessity of EMI Simulation Methodology

#### Far-Field EMI Simulation Methodology

- Proposed EMI Simulation Flow

- PCB-Level EMI Solution

- Correlation with Far-Field Measurement Results

- Relationship Between Board Design and Far-Field EMI

- Conclusion

#### **Trends of Data Storage**

- Hard Disk Drive (HDD) → Solid-State Drive (SSD)

- *Higher* Read/Write Rate, *Faster* Access Time, *Lower* Power Consumption

Source: www.google.com

Source: www.samsung.com

|                       |                             | SSD           | HDD               | Difference      |

|-----------------------|-----------------------------|---------------|-------------------|-----------------|

| Media                 |                             | NAND FLASH    | Magnetic Platters |                 |

| Read/Write Speed      | Sequential [MB/s]           | 540 / 330     | 60 / 160          | × 9 / 2         |

|                       | Random [IOPS <sup>*</sup> ] | 98000 / 70000 | 450/400           | × 217 / 175     |

| Data Access Time [ms] |                             | 0.1           | 10~12             | × 100~120       |

| Power Consumption     | Active(Idle) [W]            | 0.127(0.046)  | 1.75(0.8)         | x 13 ↓( x 17 ↓) |

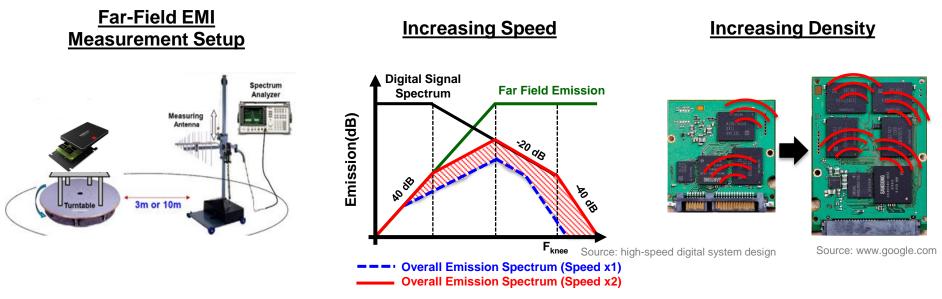

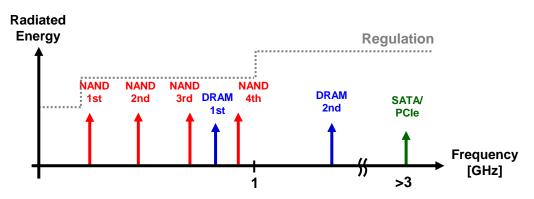

#### **EMI Problem in SSD Products**

SSD's speed and density is continuously increasing

#### EMI(Electromagnetic Interference) becomes a critical issue!

UBM

JAN 31-FEB 2, 2017

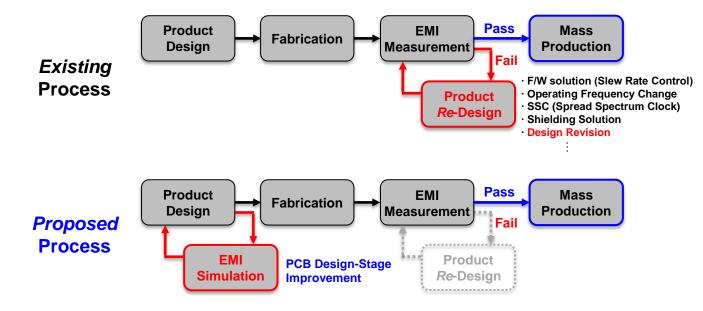

### **Necessity of EMI Simulation Methodology**

- Measurement-based EMI verification requires additional cost and time to debug

- EMI mechanisms and root causes of the radiated field need to analyze

#### **EMI Noises in SSD Products**

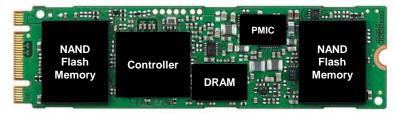

#### Composed of various devices

- NAND, DRAM, CTRL, PMIC ...

- $\circ\,$  Operated with different speeds / voltages

- Data Path

- o NAND interface, DRAM interface, Host interface

- → Higher supply voltage, longer board routing

Source: www.samsung.com

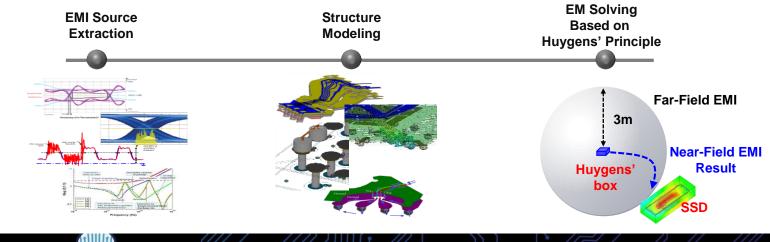

#### **Proposed Far-Field EMI Simulation Flow**

- Far-field EMI simulation methodology [Ref. APEMC2015, Benson Wei et. al.]

- Propose 3 items to enhance simulation accuracy and efficiency

- $\circ$  EMI source extraction

- Package and reference plane modeling

- $\,\circ\,$  Huygens' box optimization for N/F to F/F transform

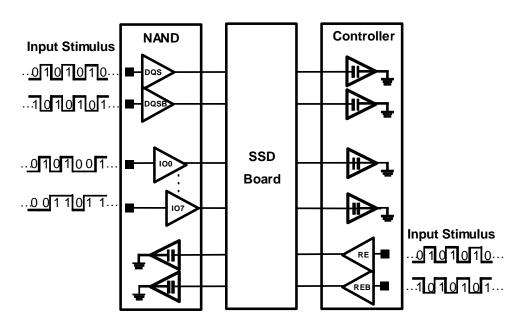

## **Stage 1: EMI Source Extraction**

- Read operation at 460 Mbps (NAND to Controller Interface)

- Block diagram

- NAND Flash I/O buffer

- Controller I/O buffer

- Board model (S-parameter)

- Input Stimulus

- I/O Buffer : PRBS 2<sup>7</sup>-1

- $\circ\,$  Strobe and clock signals

- Periodic pattern

- 5% duty cycle distortion

- : To include power noise

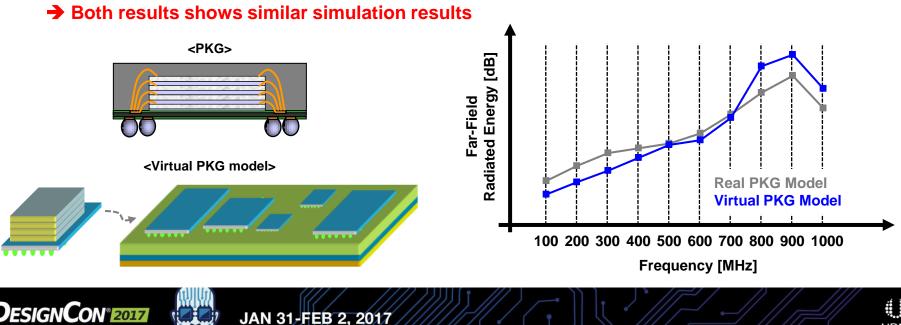

### **Stage 2: Structure Modeling (1)**

- EM simulation with package and board together

- o Impractical solution due to *simulation time* and *hardware resources*

- Propose virtual package model with metal plane

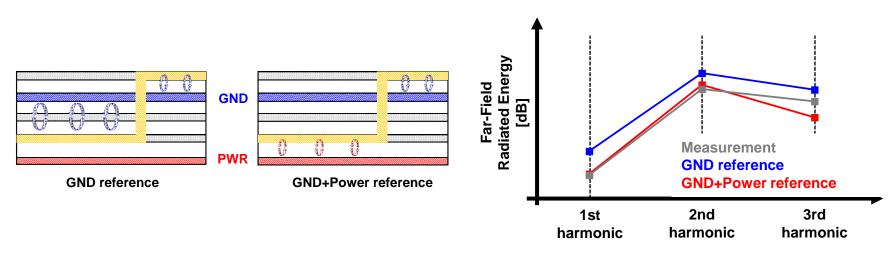

### **Stage 2: Structure Modeling (2)**

- Propose the merged reference plane

- $\circ\,$  Power and ground plane are modeled in connection to the one plane

- → Represents return path through the capacitor of the die

- Simulation result is similar to the measurement

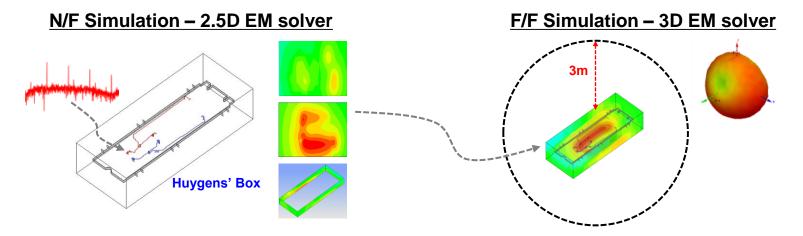

### Stage 3: EM Solving Based on Huygens' Principle

- Proposed near- to far-field transform method based on Huygens' principle

- $\circ$  Radiated energy simulation at 3-m distance from micro-unit SSD board

Attach I/O current as EMI source

Maximum electric field calculation at 3-m sphere surface

#### How to optimize Huygens' box size?

UBM

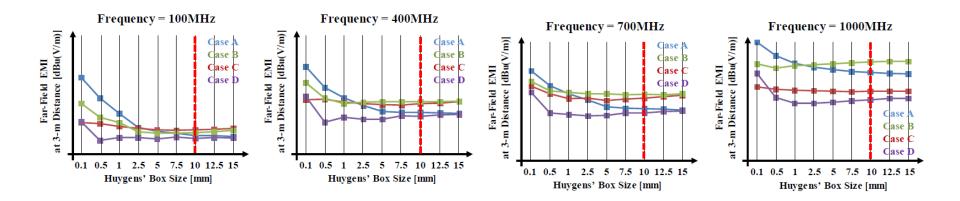

### Stage 3: EM Solving Based on Huygens' Principle

- Huygens' box size optimization

- $\circ\,$  Proper box size is necessary to minimize error for near- to-far field transform

- $\circ$  The radiated field is saturated from 10mm box size

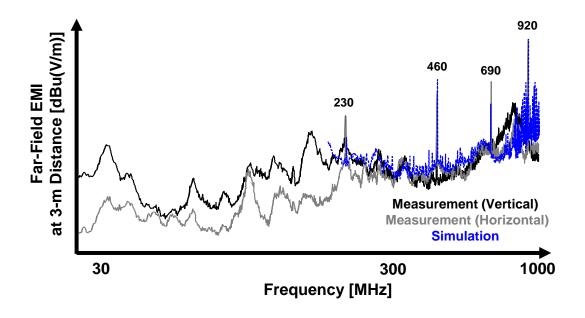

#### **Correlation with Far-Field Measurement Results**

- NAND read operation (460Mbps)

- Good agreement up to 1GHz between simulation and measurement

#### **Measurement (Vertical)**

Measurement (Horizontal)

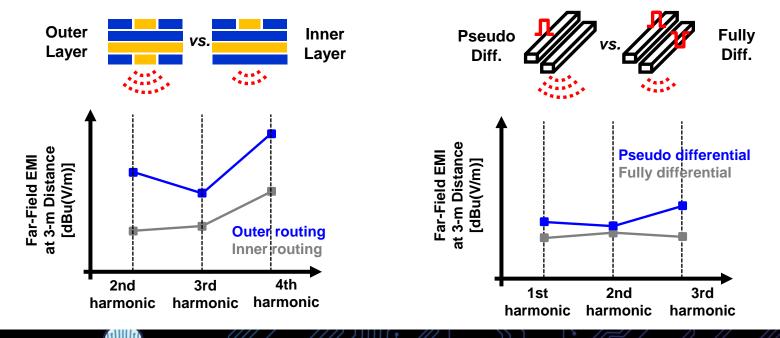

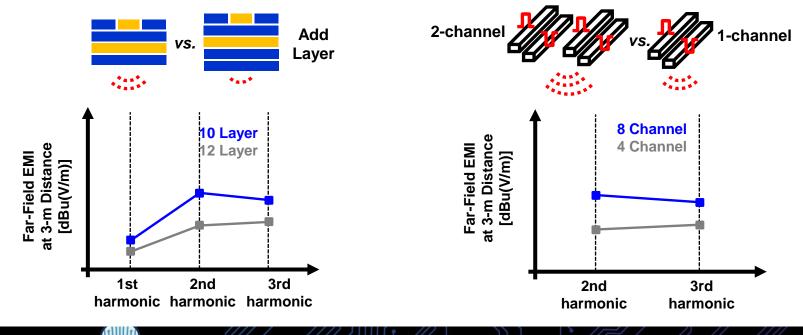

### **Case Analysis (1)**

- Investigate on relationship between board design and far-field EMI

- Routing scheme, Signaling scheme, Number of layer, Number of channel

### **Case Analysis (2)**

- Investigate on relationship between board design and far-field EMI

- **o** Routing scheme, Signaling scheme, Number of layer, Number of channel

#### Conclusion

- Far-field EMI analysis methodology for commercial SSD products

- EMI source extraction

- PCB structure modeling

- EM solving method based on huygens' principle

- Good correlation between simulation and measurement

- Investigation of the relationship between board designs and the radiated energy

Routing scheme, signaling scheme, number of layer and number of channel

- EMI analysis in the design stage prior to the manufacturing process

## Thank you!

#### Seong-Jin Mun sungj.moon@samsung.com

#### **QUESTIONS?**