### Capturing (LP)DDR4 Interface PSIJ and RJ Performance

John Ellis, Synopsys, Inc.

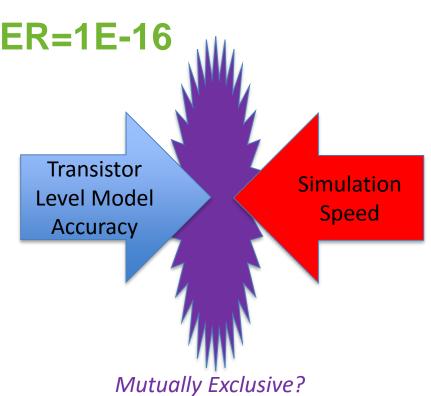

### Challenge: Simulate SSO Effects at BER=1E-16

- DDR4 and LPDDR4 now have explicit BER requirements.

- Simulating 1x10<sup>16</sup> Bits Requires:

- Lots of time in a SPICE Simulator...

- Or

- A Linear Time Invariant environment in a statistical simulator

- Capturing SSO Effects Accurately Requires:

- Transistor Level models (Slow)

- SSO Effects are non-Linear

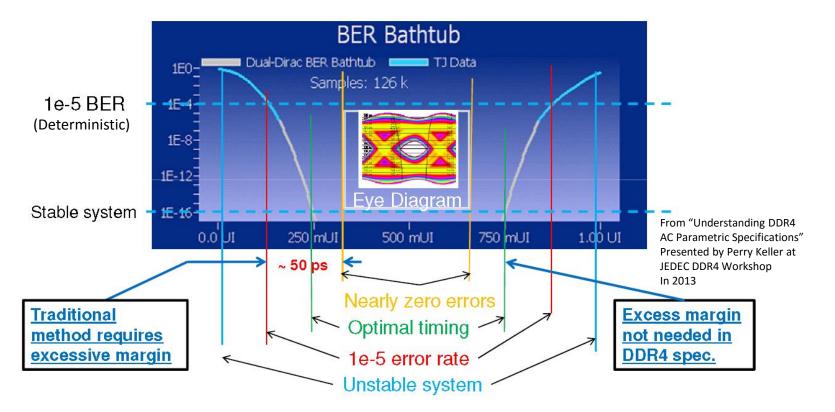

### Prior to DDR4, Padding was Added to DRAM Specs

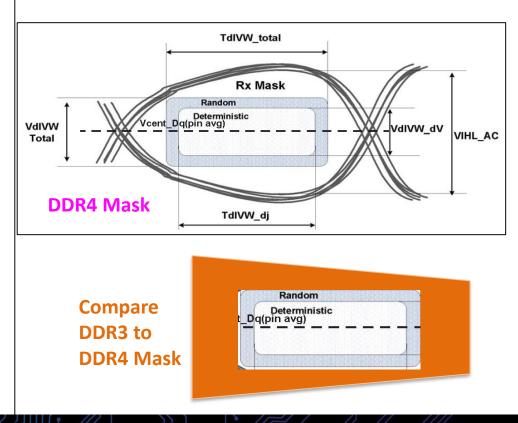

### **DDR4/LPDDR4 Eye with RJ Requirement**

- The DDR4/LPDDR4 mask reports a total that includes a fixed deterministic jitter requirement plus a random jitter requirement.

- The RJ requirement is still TBD, but BER of 1E-16 is the anticipated spec.

- If the RMS jitter value is known, the spec window can be varied to reflect the desired BER performance

- The mask assumes time and voltage training, unlike DDR3.

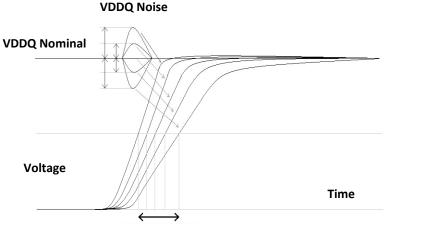

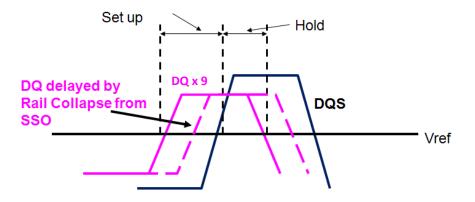

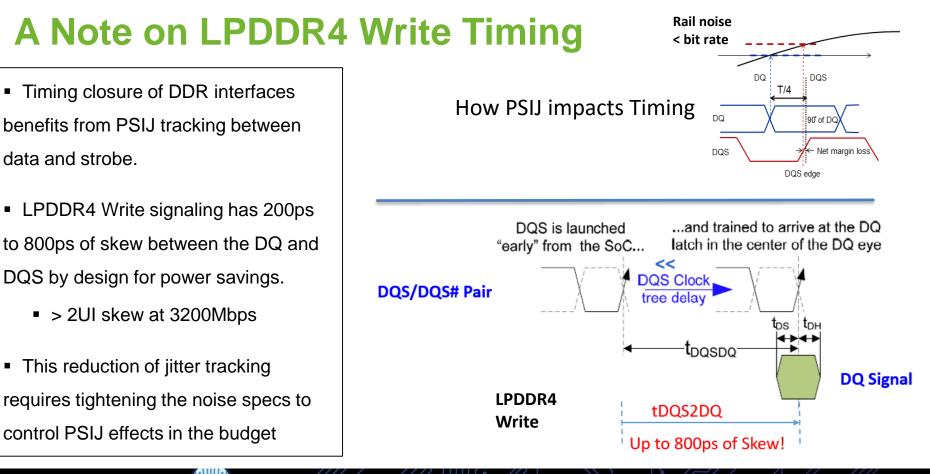

### DDR Timing is Dominated by Rail Collapse from Simultaneously Switching Outputs

- Rail noise will delay or speed up edges.

- Droop increases delay through circuits.

- The IO response to rail noise is non-linear

• Pushout from rail droop erodes Set Up

Change in delay due to SSO

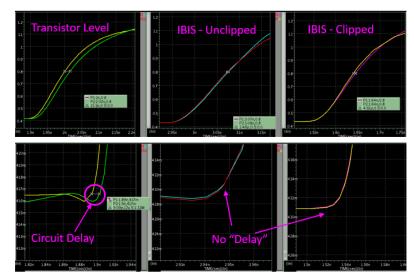

### Is IBIS an Option?

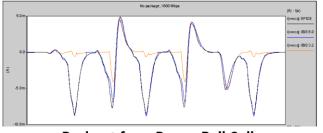

Power Aware IBIS does a good job of matching the currents generated by the SPICE model, especially when compared to older IBIS buffer models.

- IBIS does not do as good a job capturing the PSIJ created by the currents.

- The key difference is the absence of increased delay through the circuitry.

- Power Aware IBIS may have a role in modeling aggressor currents with a SPICE model as the victim.

Currents from SPICE v. IBIS 5.1 and 3.2 Good Match with 5.1

**Pushout from Power Rail Collapse**

JAN 31-FEB 2, 2017

### **IBIS v. Spice Models**

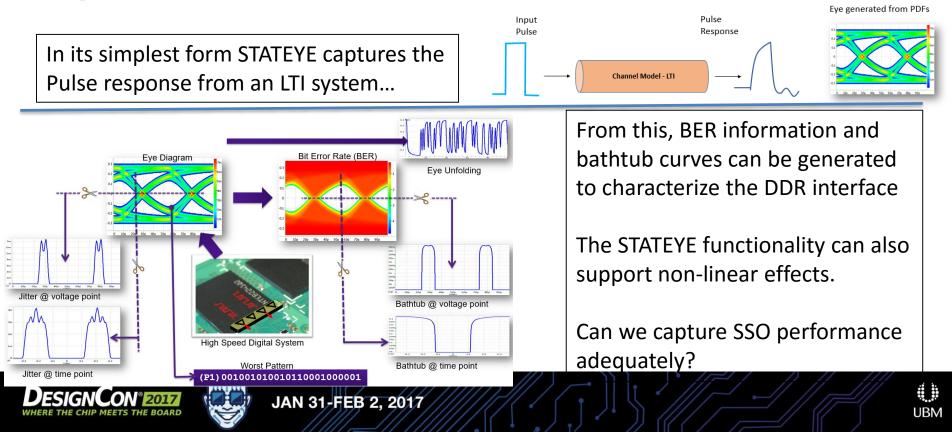

# Leveraging HSPICE® STATEYE Functionality to Capture SSO effects.

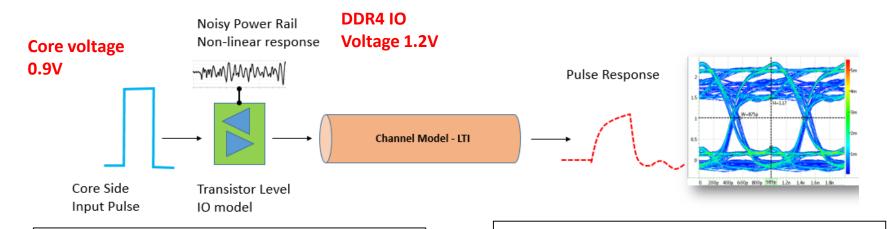

### Including the IO Model in the STATEYE Simulation

- The IO becomes part of the channel with the stimulus port applied to the core voltage domain.

- The pulse response is on the IO voltage domain.

- The resulting power rail noise creates a non-linear response with the output signal distorted by the SSO noise.

ideal supply path

Current for the IO is drawn from a non-

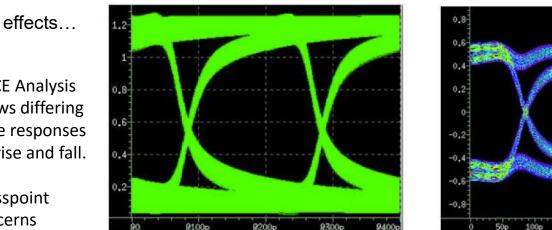

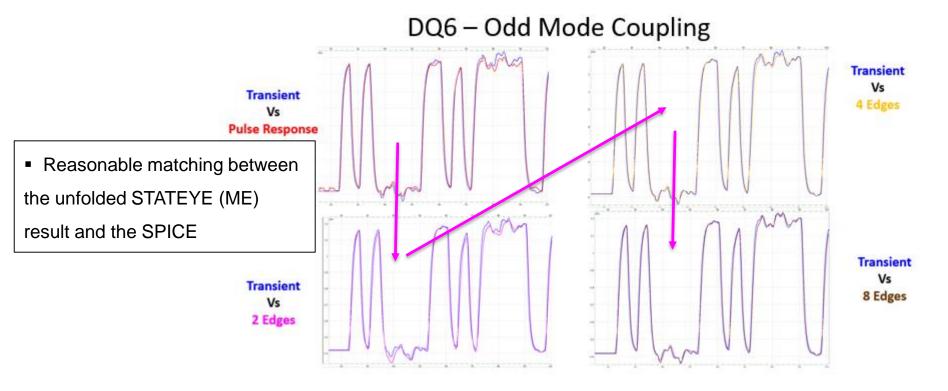

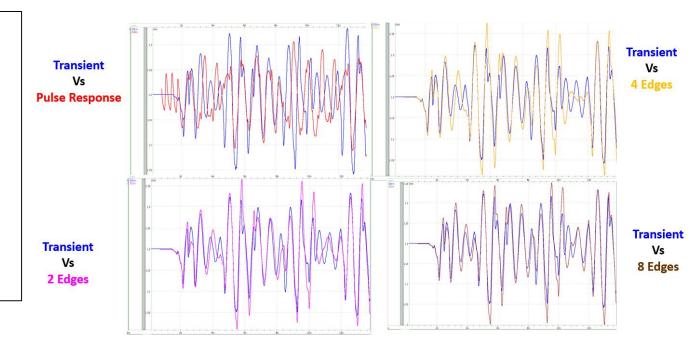

### Capturing Non-Linear Response with "Multi-Edge" Mode and "Full Transient" Mode.

- SPICE response on left shows a simple non-linearity with a falling edge faster than the rising edge.

- The standard STATEYE pulse response on the right does not capture this.

- HSPICE implementation of STATEYE includes a edge response methodologies to capture these

SPICE Analysis shows differing edge responses for rise and fall.

Crosspoint concerns

**STATEYE** standard pulse response does not capture these effects.

JAN 31-FEB 2, 2017

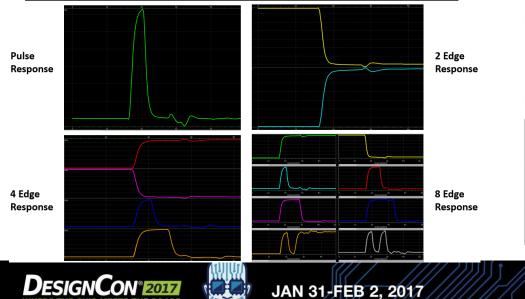

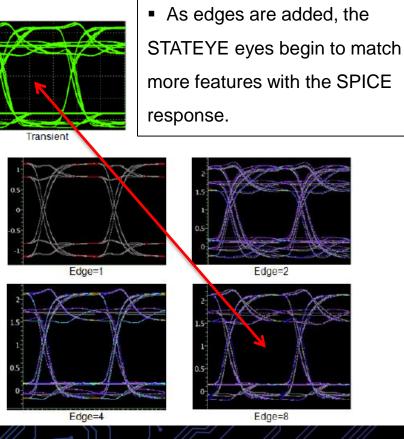

### **Multiple Edge Response**

• One simulation must be run for each edge

response. 8 edge= 8x runtime of pulse response.

Responses can be saved to greatly shorten

future runtimes.

### Full Transient Response

- Generates the probability density function based upon an arbitrary bit stream.

- Responses CANNOT be saved must rerun

- This should provide more accuracy

- Run this mode first to judge accuracy of potential solution. Then look at multi-edge

mode for increased flexibility and speed.

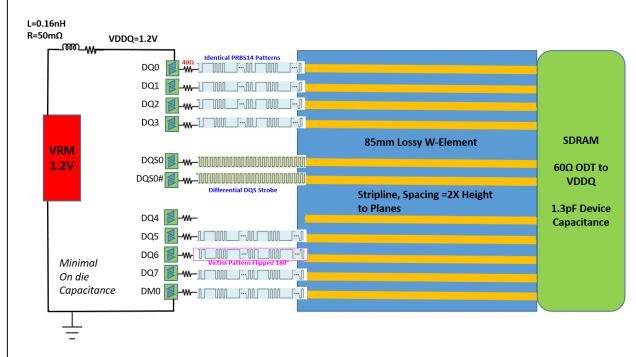

### Simulation Environment

- Simulate a single byte lane during

- a Write operation.

-

- Identical PRBS patterns to excite SSO effects. Then flip one bit to excite Odd mode coupling on one of the bits. 2667Mbps

- Minimal Decoupling included.

- 85mm of 51Ω stripline

60Ω ODT to VDDQ

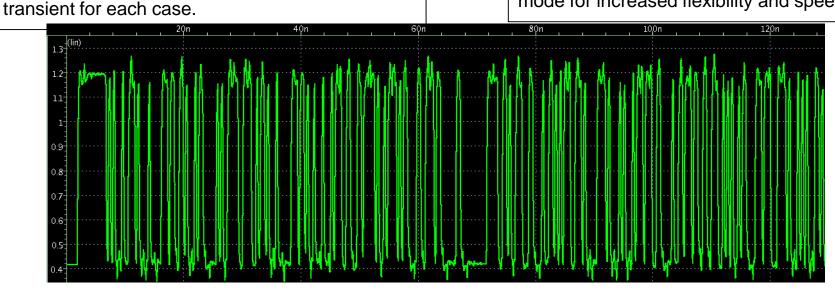

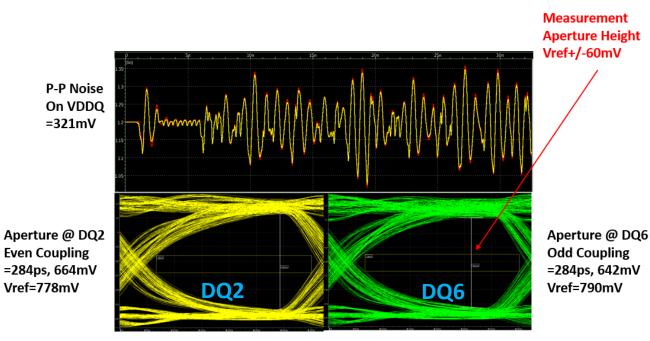

### **Initial SPICE Transient Results**

JAN 31-FEB 2, 2017

- Baseline for Comparison

- Assumes the SPICE results are "correct".

- Significant amount of Rail noise on VDDQ, +/-13%

- DQ2 ~ Even Mode

Coupling

DQ6 ~ Odd Mode

Coupling.

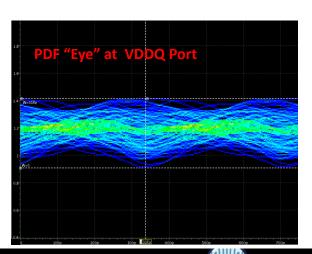

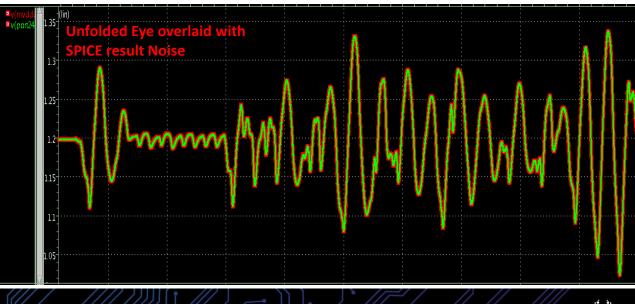

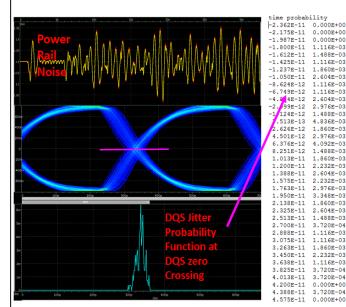

### **Overlay of STATEYE(FT) Noise vs. SPICE**

- As expected, the "Full Transient" Mode of STATEYE matches the SPICE results well in terms of capturing the Rail Noise.

- This is important to confirm since the rail noise will be the primary source of non-linearity.

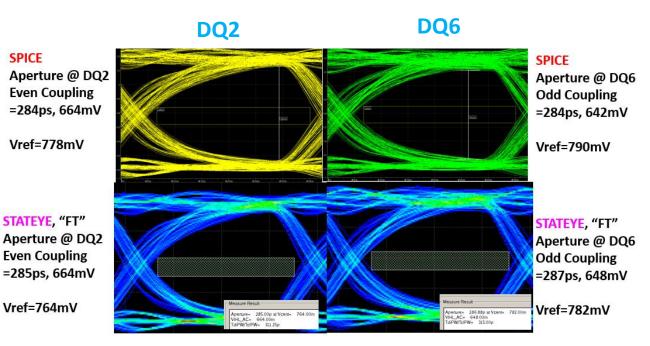

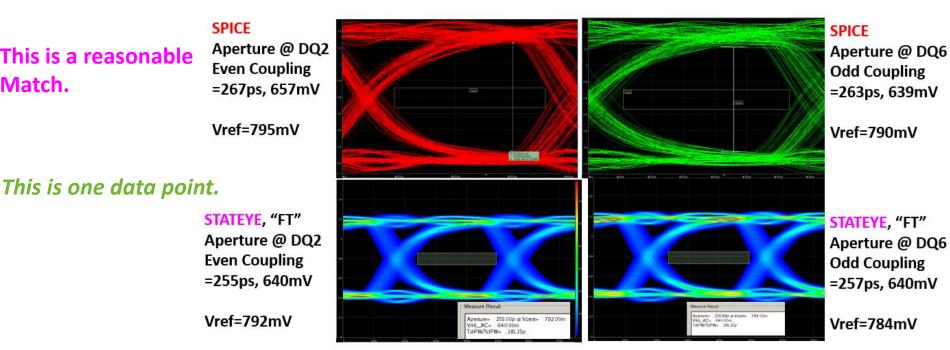

### **Comparing STATEYE(FT) Eyes to SPICE**

SPICE

JAN 31-FEB 2, 2017

- Overall Good Agreement in

- horizontal and vertical opening.

- VRFF somewhat shifted

- Eyes are triggered by and ideal Unit Interval.

- DDR is source synchronous, so the Eyes triggered by the DQS must be compared.

- Include DQS Jitter

- Jitter tracking effects

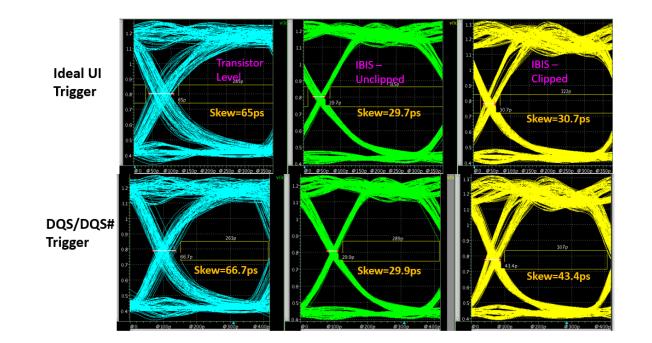

### "Triggering" the DQ Eye in STATEYE

- There is no triggering capability, but a DQS jitter function can be applied to the received DQ signal.

- Drawback:

- Two FT STATEYE simulations are now required.

- 1 to generate the jitter function and 1 to simulate with the function applied.

- For Further Study:

- Should this jitter function be applied to the stimulus or at the probe port?

## **Comparing STATEYE(FT) Triggered Eyes to SPICE**

#### **DQ2**

DQ6

### DESIGNCON<sup>®</sup> 2017

This is a reasonable

Match.

### Multi-Edge Mode – Data Stream Comparison

### Multi-Edge Mode – Power Rail Comparison

- Not a great match. With 8 edges the result is getting closer, but still exaggerates peaks.

- The Reusability of edge

responses makes ME mode

worth pursuing.

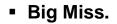

### **Comparing STATEYE(ME – 8 Edge) Eyes to SPICE**

STATEYE results seem to be missing the jitter effects from the power rail.

DQ6 looks closer, but that reflects the odd mode crosstalk on the board more than PSIJ.

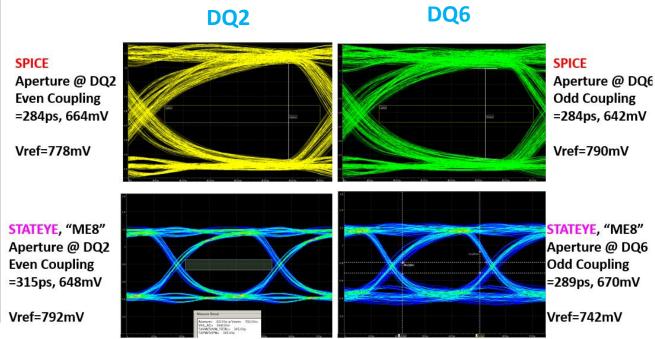

### **Multi-Edge Mode Misses the Time Shift Component**

- Compare the differential DQS SPICE simulation to the Full Transient and Multi-Edge STATEYE Simulations

- Eliminates any ISI effects and most of the Crosstalk.

- The superposition of edge responses does not capture the delay element of the non-linear response.

- Jitter must be added.

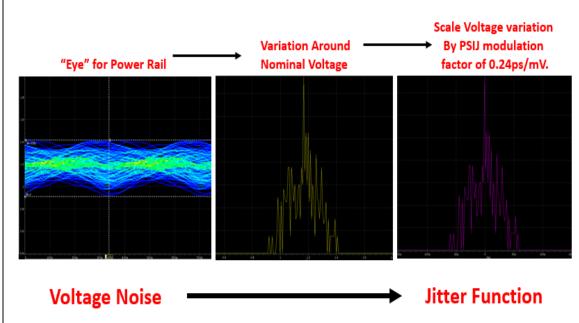

### **Capturing the Jitter from the Power Supply for ME8**

- Similar to generating the DQS jitter function.

- Cross-section through the power rail response

- Create a PDF of the voltage noise around nominal.

- Convert to jitter with ps/mV modulation factor

- Drawback:

- Additional ME STATEYE simulations are now required.

- For Further Study:

- Selection of Cross-Section

- Should this jitter function be applied to the stimulus or at the probe port?

### **ME-8 Edge with Jitter**

- STATEYE Results show significantly more closure than transient against ideal UI.

- Indicates poor capture of supply noise, wrong cross-section point selected, or a combination of both

- Results are closer when the DQS "trigger" is applied.

- The potential benefit of reusing the edge responses of the Multi-Edge method makes this method worth pursuing despite the current less than impressive results.

- Capturing the supply noise from a full transient method than applying to ME is worth exploring.

- This will be the subject of a future paper.

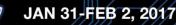

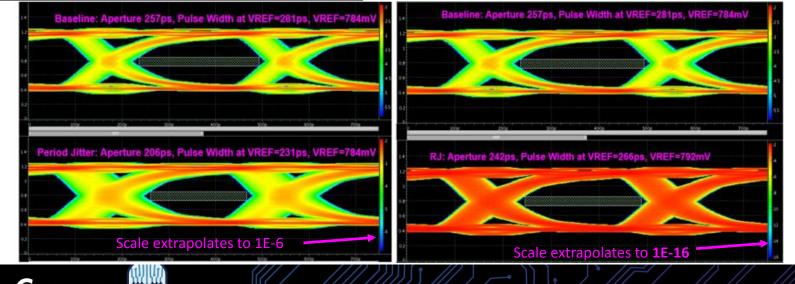

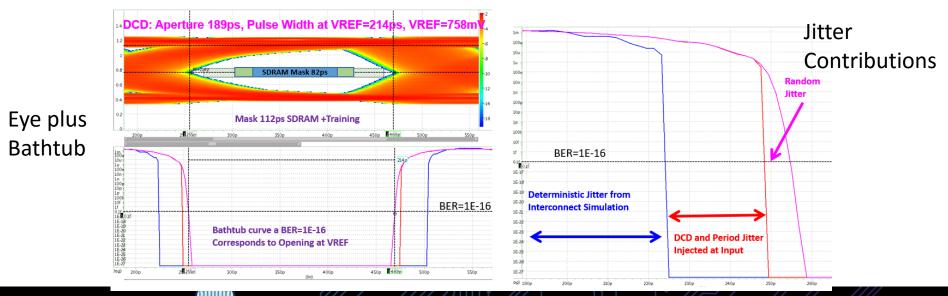

### **STATEYE Results into the Write Timing Budget**

| omponents                           | Description                                                                                                                                                         | Worst Case<br>Uncertainty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter Name                      |                                                                                                                                                                     | Contributions (ps)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PLL Clock Source<br>Jitter          | 18ps of Jitter from the PLL at BER=1E-16.<br>This is mostly RJ. RMS Jitter =1.095ps-<br>RMS. Treat as Random Jitter.                                                | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PowerSupply<br>Induced Jitter       | PSIJ from noise on the core power rail.<br>Noise is predominantly at package<br>resonance of 200MHz. Treat as Periodic<br>Jitter.                                   | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

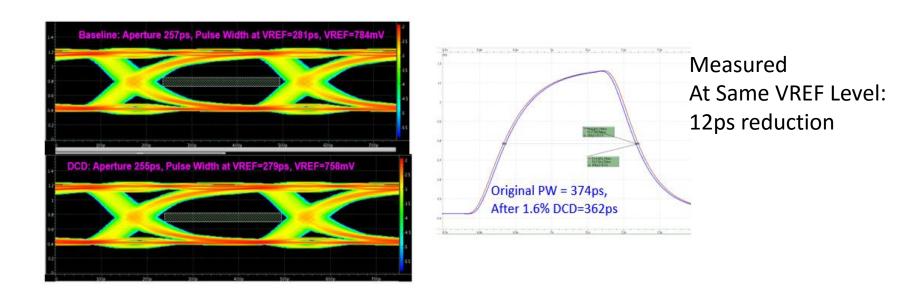

| VO Rise/Fall Skew                   | Duty Cycle Distortion that closes the pulse width. Treat the 12 ps as ~1.6% duty cycle distorion at 2667Mbps.                                                       | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Training Errors                     | Delay Line Granularity, Step size non-<br>linearity effects and VT drift impact on<br>timing. For simplicity, treat as a static<br>contributor to total uncertainty | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Total Transmitter (PHY) Uncertainty |                                                                                                                                                                     | 112                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Input Eye Mask                      | SDRAM Receiver Window Requirements -<br>0.22UI at 2667Mbps                                                                                                          | 82                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                     | Total Contributions for End to End Timing                                                                                                                           | 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     | Parameter Name PLL Clock Source Jitter PowerSupply Induced Jitter VO Rise/Fall Skew Training Errors                                                                 | Description           Parameter Name           PLL Clock Source<br>Jitter         18ps of Jitter from the PLL at BER=1E-16.<br>This is mostly RJ. RMS Jitter =1.095ps-<br>RMS. Treat as Random Jitter.           PowerSupply         PSIJ from noise on the core power rail.<br>Noise is predominantly at package<br>resonance of 200MHz. Treat as Periodic<br>Jitter.           VO Rise/Fall Skew         Duty Cycle Distortion that closes the pulse<br>width. Treat the 12 ps as ~1.6% duty cycle<br>distorion at 2667Mbps.           Training Errors         Delay Line Granularity, Step size non-<br>linearity effects and VT drift impact on<br>timing. For simplicity, treat as a static<br>contributor to total uncertainty           Input Eye Mask         SDRAM Receiver Window Requirements -<br>0.22UI at 2667Mbps |

#### **Known Quantities:**

- PHY Budget

- DRAM Mask Requirement

### **Using STATEYE to Remove Pessimism**

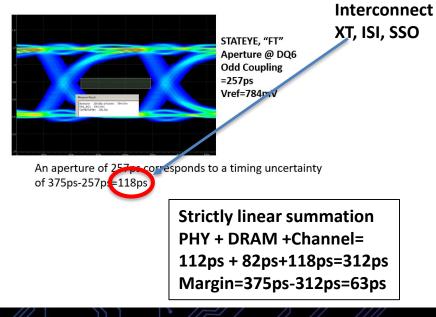

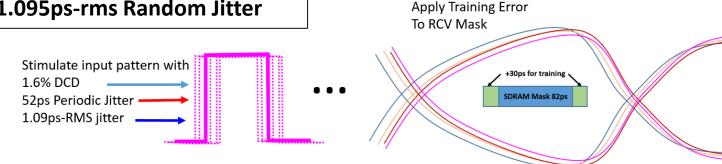

At the input stimulus, Apply jitter functions

- **1.6% Duty Cycle Distortion**

- 52ps Periodic Jitter (200MHz)

- 1.095ps-rms Random Jitter

For the Receive mask

- **DRAM requirement of 82ps**

- Add the static training error to this window.

- Total requirement of 112ps

### **Including Duty Cycle Distortion**

- DDR4/LPDDR4 interfaces train to the optimum VREF placement.

- Although DCD adds 12ps of uncertainty at the same VREF level, the training will find the widest part of the

eye, reducing the effective uncertainty to only 2ps.

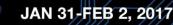

### Including Period Jitter and Random Jitter

JAN 31-FEB 2, 2017

- The Periodic Jitter reduces the eye by about 51ps.

- Fairly linear impact on result with no shift in ideal VREF.

- Applying RMS jitter of 1.095ps-rms reduces eye by 15ps.

- 1.095 x16.444 (Q-factor) =18ps

- Difference is shift in ideal VREF

.

UBM

### **Combine All Input Jitter Sources with Channel Sim**

- Total performance margin of interface =189ps-112ps mask = 77ps

- 14ps of pessimism was removed from the linear budget with this method, 3.7% of a UI

- Fairly linear impact on result with no shift in ideal VREF.

### **In Summary**

| StatEye Mode                                     | Pros                                                                                                         | Cons                                                        | Path Forward                                                                                           |  |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| STATEYE (Full Transient)                         | Good Match to Transient for Eye and<br>Power Rail                                                            | Long Initial Transient No Save and Reload Capabiliites      | Expand to Read Operations. More<br>Complex Interfaces (Multi-DIMM)                                     |  |

|                                                  |                                                                                                              | Need 2 simulations. 1st to determine<br>DQS jitter Function |                                                                                                        |  |

| STATEYE (Multi-Edge Mode)                        | Reasonable Match to Eye Amplitude.                                                                           | Poor Match to Supply Noise and Jitter.                      | Refinement of Jitter Function<br>Application. Explore Combining Full<br>Transient Mode with Edge Mode. |  |

|                                                  | Flexible. Reloading edge responses allows for quick simulation.                                              | Only vertical superposition of Edges                        |                                                                                                        |  |

| Topics for Further Exploration                   | on                                                                                                           |                                                             |                                                                                                        |  |

| Applying jitter functions for<br>Budget Purposes | Location of Application Port: Input, Load or Intermediate port after the level shifter but bere the channel? |                                                             |                                                                                                        |  |

|                                                  | Creating Rail Noise plots in FT mode to be included with ME mode.                                            |                                                             |                                                                                                        |  |

|                                                  | Selecting Time Slice Location for Voltage Noise Curve.                                                       |                                                             |                                                                                                        |  |

|                                                  | Edge Mode: When combining PSIJ and DQS Jitter functions, are some of the effects being double counted?       |                                                             |                                                                                                        |  |

|                                                  | Is Periodic Jitter the best representation of the PHY power supply induced jitter function?                  |                                                             |                                                                                                        |  |

| Other Interfaces                                 | Read Operations. Accuracy for non Point to Point Applications                                                |                                                             |                                                                                                        |  |

| Jitter Amplification                             | When must if be Considered for DDR and how should it be implemented?                                         |                                                             |                                                                                                        |  |

| StatEye Functionality                            | Limited save and Reload of Full Transient Mode Response. Greater than 8 edges. Jitter Amplification          |                                                             |                                                                                                        |  |

# Thank you!

#### **QUESTIONS?**

UBM