# DESIGNCON<sup>®</sup> 2015

# AND CTLE FEATURE OPTIMIZATION WITH STATISTICAL ENGINE FOR BER SPECIFICATION

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

Penglin Niu, penglin@xilinx.com

Fangyi Rao, fangyi rao@keysight.com

Juan Wang, juanw@xilinx.com

Gary Otonari, gary otonari@keysight.com

Nilesh Kamdar, nilesh kamdar2@keysight.com

Yong Wang, <a href="mailto:yongw@xilinx.com">yongw@xilinx.com</a>

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### Outline

- DDR4 feature and design challenge

- > FPGA DDR system design challenge

- > DDR4 statistical simulation method

- **DDR4** De-emphasis and CTLE optimization result discussion

## DESIGNCON<sup>®</sup> 2015

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

#### **DDR4 Features**

| Feature             | DDR3                      | DDR4                               |

|---------------------|---------------------------|------------------------------------|

| Voltage             | 1.5V                      | 1.2V                               |

| Max Datarate (Mbps) | 2133                      | 3200                               |

| DQ Bus              | SSTL15                    | POD12                              |

| DQ Vref             | external                  | Internal                           |

| DQ Driver           | 34 <i>,</i> 40 & 60 (ohm) | 34, 40, <mark>48</mark> & 60 (ohm) |

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### **FPGA DDR4 Design Challenges**

#### > DDR4 Design Challenge

VESIGN HONE

- Higher datarate, Higher loss, intensified ISI

#### > FPGA Configurable I/O standards

- DDR3, DDR3L, DDR4, LPDDR2, LPDDR3, RLDRAM3, QDR2+, QDR4

- High pad capacitance: FPGA ~3.5pF Vs. ~1.8pF ASIC

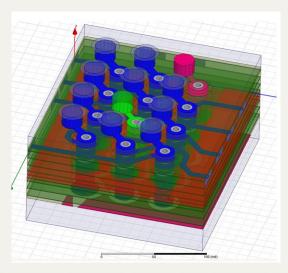

#### **FPGA High I/O count**

- Up to ~1400 IO counts in Ultrascale family

- High density signal routing

- High signal to ground ratio

#### > Signal enhancement techniques to mitigate

- De-emphasis & CTLE

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

FPGA DDR4 Design Challenges

ESIGN HO

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

#### **Traditional DDR Design Methodology**

- Run transient simulation using IBIS or SPICE models of controller and memory

- Measure setup and hold times on waveforms

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

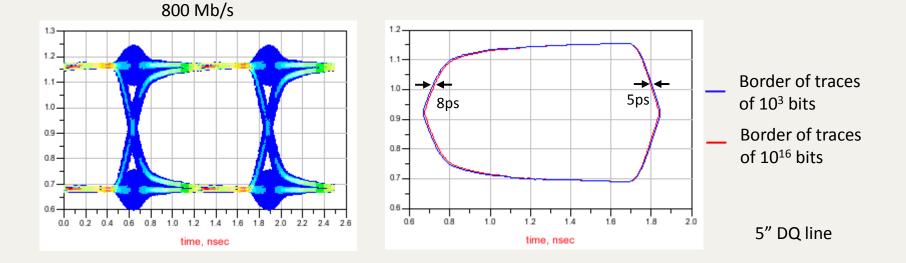

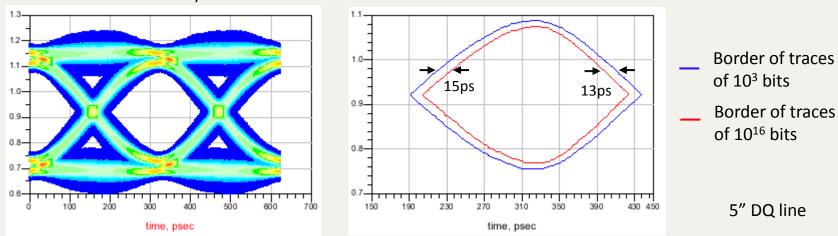

### **ISI at Low Speed**

- Timing margin deceases by 1% UI from 10<sup>3</sup> bits to 10<sup>16</sup> bits

- At low speed, limited number of bits is adequate for system verification

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

## **ISI at High Speed**

3200 Mb/s

- Timing margin deceases by 9% UI from 10<sup>3</sup> bits to 10<sup>16</sup> bits

- At high speed, design needs to be verified at target BER

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

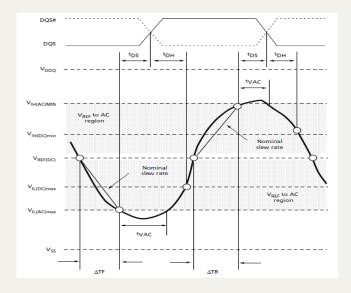

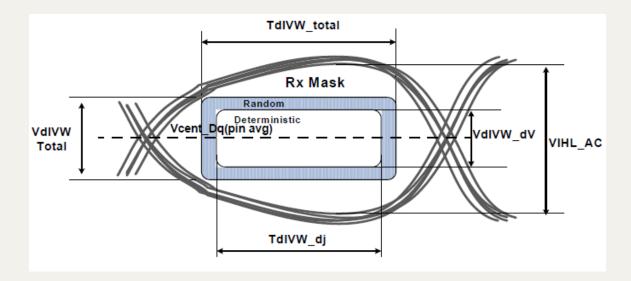

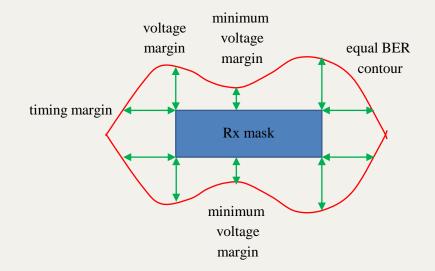

#### **DQ Rx Mask Spec in DDR4**

- Mask consists of deterministic and random portions

- BER inside the total mask must be below 10<sup>-16</sup>

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### **Statistical Simulation for BER**

- It's impractical to simulate 10<sup>16</sup> bits to estimate BER at 10<sup>-16</sup>

- Statistical method can be employed to calculate eye probability distributions

- Equivalent to running infinite number of bits

- BER can be obtained rigorously at arbitrarily low level

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

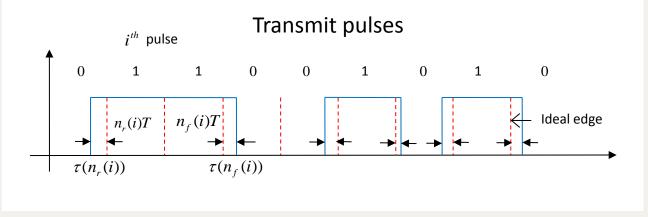

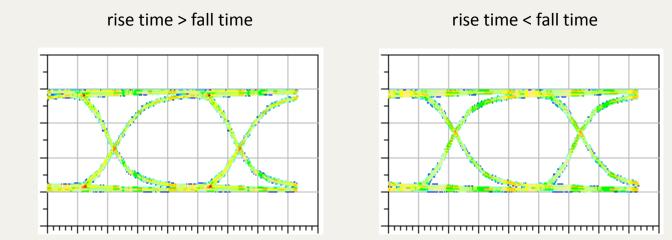

### **Linear Superposition**

$$v(t) = \sum_{i} \left\{ R[t - n_r(i) \cdot T - \tau(n_r(i))] - F[t - n_f(i) \cdot T - \tau(n_f(i))] \right\} + v_0$$

R(t): rise edge step response F(t): fall edge step response T: UI

$\tau$  : transmitter jitter

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

#### **Transmitter Jitter**

Jitter components include DCD, SJ and RJ

$$\tau(n_r) = -\frac{DCD_{pp}^{data}}{2} - (-1)^{n_r} \frac{DCD_{pp}^{clk}}{2} + Asin(2\pi f n_r T + \phi) + \rho(n_r)$$

$$\tau(n_f) = \frac{DCD_{pp}^{data}}{2} - (-1)^{n_f} \frac{DCD_{pp}^{clk}}{2} + Asin(2\pi f n_f T + \phi) + \rho(n_f)$$

$DCD_{pp}^{data}$  : peak-to-peak data DCD  $DCD_{pp}^{clk}$  : peak-to-peak clock DCD A & f: SJ amplitude and frequency  $\rho$ : RJ

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### **Eye Probability Distribution**

$p(v,t) = \frac{1}{2\pi} \int_0^{2\pi} d\phi \frac{1}{2^M} \sum_{m=1}^{2^m} \int \delta[v - v^{(m)}(t)] \cdot \prod_i g[\rho(n_r^{(m)}(i))] \cdot g[\rho(n_f^{(m)}(i))] \cdot d\rho(n_r^{(m)}(i)) \cdot d\rho(n_f^{(m)}(i))$

m: pattern indexM: step response settle time in bitg: RJ PDF

- Tx jitter affects the output distribution through channel step responses

- Jitter effect is directly handled in PDF calculation instead of post-processing

- PDF is computed rigorously using efficient algorithms w/o approximation

- Accurate prediction of BER

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

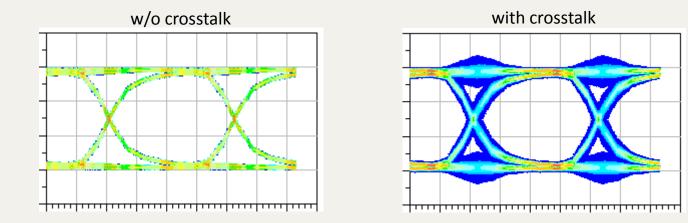

#### **Crosstalk**

Crosstalk is additive noise to victim signal

Included by convolution between victim PDF and crosstalk PDF

$p(v,t) = \int p_{victim}(v - v_1 - v_2 \cdots - v_n, t) p_{xtlk}^{(1)}(v_1, t) p_{xtlk}^{(2)}(v_2, t) \cdots p_{xtlk}^{(n)}(v_n, t) dv_1 dv_2 \cdots dv_n$

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

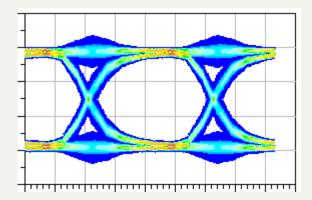

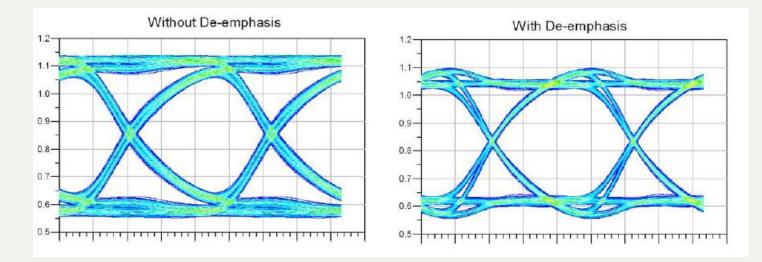

#### **Driver De-emphasis**

#### w/o de-emphasis

#### 3dB de-emphasis

## DESIGNCON<sup>®</sup> 2015

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

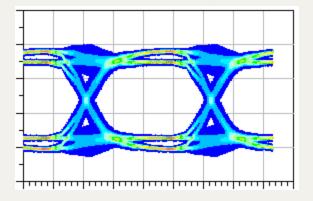

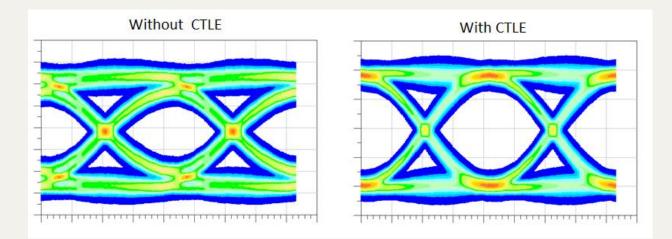

#### **Rx CTLE**

$$H(s) = A \frac{(s - z_1) \dots (s - z_n)}{(s - p_1) \dots (s - p_k)}$$

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

JESIGN HON

#### **Asymmetric Rise and Fall Edges Capability**

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### **Timing and Voltage Margins**

- Timing and Voltage margins are measured at each mask corner

- Ring-back is captured by minimum voltage margins

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

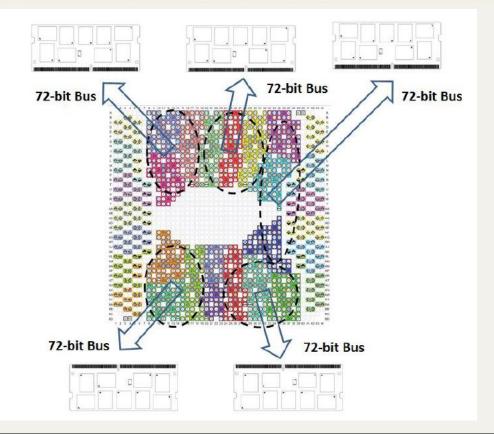

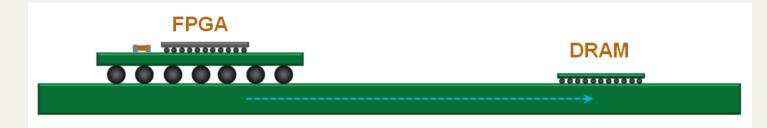

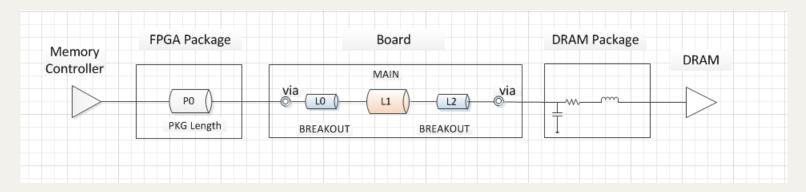

#### **DDR4 Channel Topology**

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### **CTLE Optimization**

#### > CTLE design parameters

- fz (zero), fp1 (first pole), fp2 (second pole), Gain\_dc (dc gain)

$$H_{CTLE}(s) = c \frac{(s+w_zero)}{(s+w_pole1)(s+w_pole2)}$$

$$c = Gain_dc \frac{w_pole1*w_pole2}{w_zero}$$

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

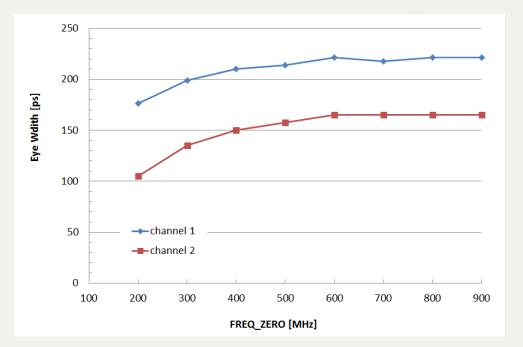

## **CTLE Optimization**

- CTLE fz sensitivity sweep for two study channels

- BER 10<sup>-16</sup> eye width @ Vref

+/-68mV saturated after

600Mhz fz

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

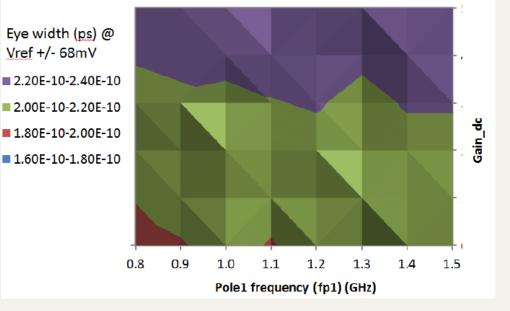

## **CTLE Optimization**

- CTLE fp1 Vs. Gain\_dc sensitivity sweep at 4.5GHz bandwidth

- BER 10<sup>-16</sup> eye width not sensitive to fp1 around 1.2GHz

- BER 10<sup>-16</sup> eye width increase with higher Gain\_dc

BER 10-16 eye width from fp1 and gain\_dc at 4.5GHz bandwidth (fp2)

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

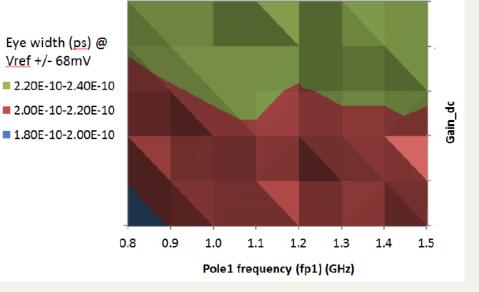

## **CTLE Optimization**

- CTLE fp1 Vs. Gain\_dc sensitivity sweep at 6 GHz bandwidth

- BER 10<sup>-16</sup> eye width not very sensitive to fp2 around 5GHz

- BER 10<sup>-16</sup> eye width increase with higher Gain\_dc

## DESIGNCON<sup>®</sup> 2015

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

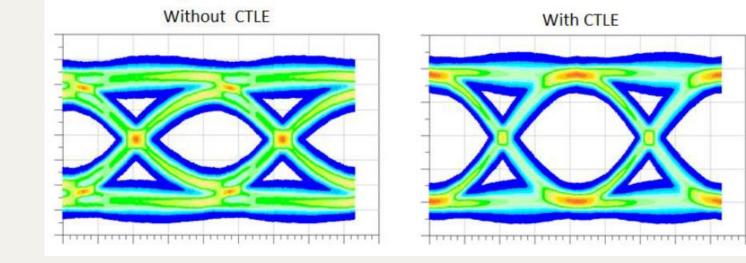

### **CTLE Optimization -- 2400Mbps DDR4**

#### significant BER 10<sup>-16</sup> eye width gain achieved with optimized CTLE

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

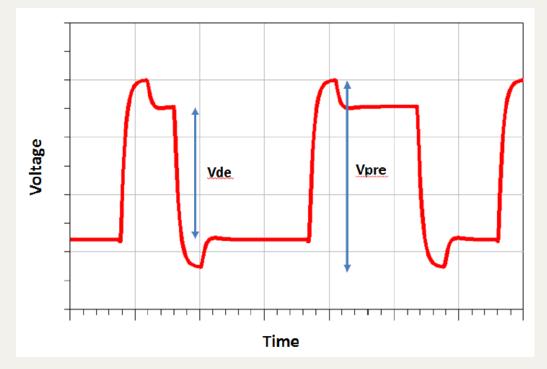

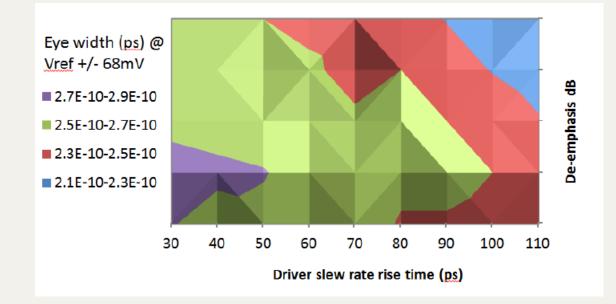

### **De-emphasis Optimization**

De-emphasis dB level is defined as 20\*log(Vde/Vpre)

#### January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

#### **De-emphasis Optimization**

JESIGN HON

#### > Optimal De-emphasis dB can be identified for driver slew rate

#### January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

VESIGN LOV

#### **De-emphasis Optimization – 2400Mbps DDR4**

#### > 10-20ps BER 10<sup>-16</sup> eye width gain achieved with optimized dB setting

January 27-30, 2015 | Santa Clara Convention Center | Santa Clara, CA

### Summary

- A statistical simulation engine is introduced for designing DDR4 system to JEDEC 10-16 BER target

- Effects of driver de-emphasis and Rx CTLE on DDR4 timing at BER target of 10-16 are investigated

- > De-emphasis and CTLE are effective techniques to mitigate jitter and achieve DDR4 design target after optimization.